通过FPGA的多重配置可以有效地精简控制结构的设计,同时可以用逻辑资源较少的FPGA器件实现需要很大资源才能实现的程序。以Virtex5系列开发板和配置存储器SPI FLASH为基础,从硬件电路

2014-01-24 14:17:22 13670

13670

在FPGA中实现在应用编程(In Application Pro—gramming,IAP)有两种方法:一种是,在电路板上加外电路。例如用MCU或CPLD来接收配置数据,在被动串行(PS)模式

2020-07-22 16:41:32 1693

1693

随着FPGA芯片密度的增加,串行PROM已不能适应高密度的FPGA的配置。大容量的并行PROM所要求的寻址方式又不能直接与FPGA接口,这时可以采用XC9500 CPLD和PROM对高密度FPGA

2020-07-23 16:58:08 797

797

的面阵CCD驱动时序发生器设计,基于CPLD的面阵CCD驱动时序发生器设计及其硬件实现,基于CPLD的线阵CCD驱动电路的设计,基于CPLD的线阵CCD驱动电路设计与实现,基于CPLD的线阵CCD驱动

2019-06-03 16:45:25

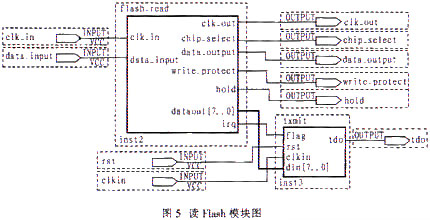

本人新手,在设计一个cpld的控制电路,需要从flash中读取数据传送给其他模块。由于数据量比较大,cpld内部的flash容量不够,需要在外部配置一块存储量较大的flash芯片,flash芯片中的数据以后会有更新,那么请问除了烧写器外我用什么方式将数据烧写进flash?

2013-07-31 11:23:19

电源、地连接到下载线即可。(特权同学,版权所有)说到FPGA的配置,这里不得不提一下他们和CPLD内部存储介质的不同。CPLD由于大都是基于PROM或FLASH来实现可编程特性,因此对他们进行在线编程

2019-01-30 02:34:52

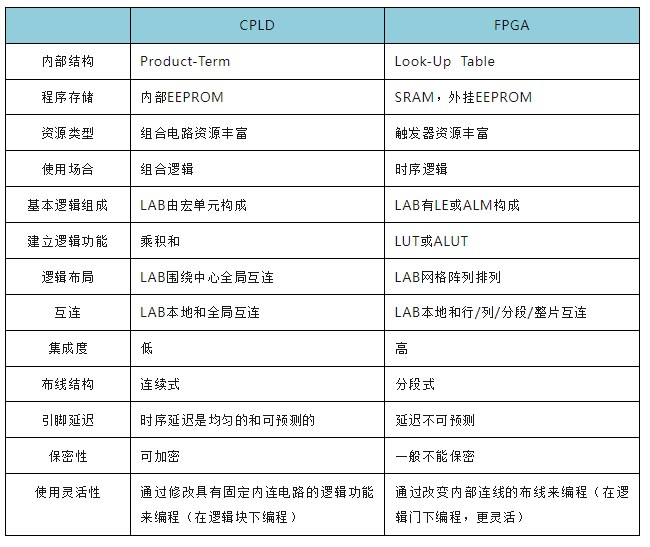

FPGA与CPLD的辨别和分类主要是根据其结构特点和工作原理。通常的分类方法是:将以乘积项结构方式构成逻辑行为的器件称为CPLD,如Lattice的ispLSI系列、Xilinx的XC9500系列

2019-07-01 07:36:55

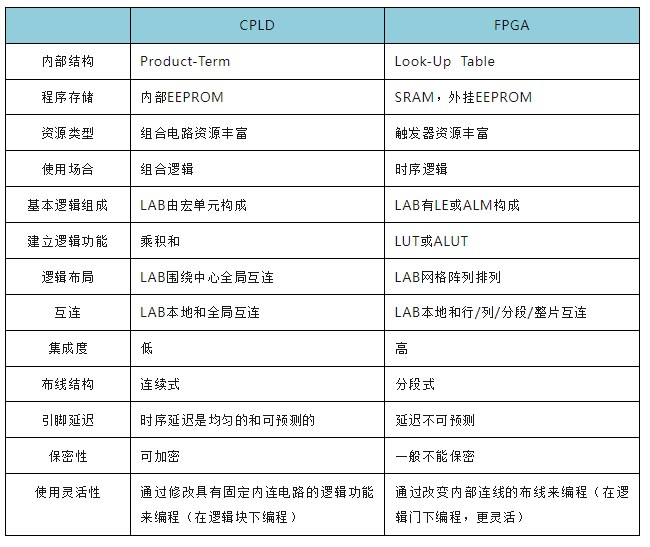

FPGA与CPLD的区别

尽管很多人听说过CPLD,但是关于CPLD与FPGA之间的区别,了解的人可能不是很多。虽然FPGA与CPLD都是“可反复编程的逻辑器件”,但是在技术上却有一些差异。简单

2011-09-27 09:49:48

、路由性能极好,用户可以改变他们的设计同时保持引脚输出不变。与FPGA相比,CPLD的I/O更多,尺寸更小。如今,通信系统使用很多标准,必须根据客户的需要配置设备以支持不同的标准。CPLD可让设备做出

2012-10-26 08:10:36

和CPLD最大的区别是他们的存储结构不一样,这同时也决定了他们的规模不一样。但是从使用和实现的角度来看,其实他们所使用的语言以及开发流程的各个步骤几乎是一致的。对于大多数的初学者来说,学FPGA还是

2019-02-21 06:19:27

用CPLD实现。 (2)数据密集型,需要大量的数据处理能力,但逻辑相对简单,对输入要求少,适合FPGA实现。7、配置不同 CPLD:采用EPROM,E2PROM工艺,直接写入,保密性好。 FPGA:采用SRAM工艺,故需外加ROM芯片,用于存储配置信息。其保密性较差。可实现动态重构。高端FPGA具备加密功能

2020-08-28 15:41:47

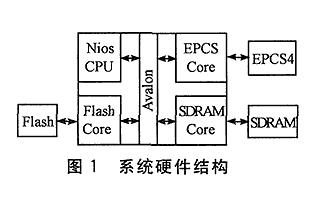

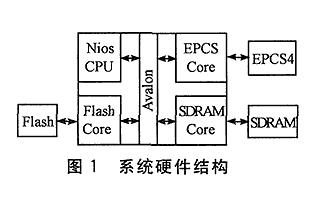

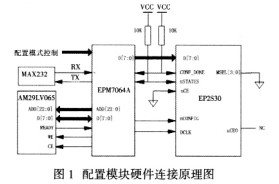

]图1]3 基于CPLD 的FPGA 加载方案3.1]在 设备端通信产品中,基于CPLD 的FPGA 从并加载框如图2 所示,配置数据存储在FLASH 中,且在加载数据之前,CPU 通过局部总线和双倍

2019-07-12 07:00:09

用“与—或”表达式来描述,所以该“与或阵列”结构能实现大量的组合逻辑功能) 简单的“与或”阵列:(PAL、GAL、CPLD) 含查找表的逻辑单元:(FPGA) CPLD和FPGA的主要

2020-07-16 10:46:21

电源、地连接到下载线即可。(特权同学,版权所有)说到FPGA的配置,这里不得不提一下他们和CPLD内部存储介质的不同。CPLD由于大都是基于PROM或FLASH来实现可编程特性,因此对他们进行在线编程

2015-04-13 12:29:55

和CPLD最大的区别是他们的存储结构不一样,这同时也决定了他们的规模不一样。但是从使用和实现的角度来看,其实他们所使用的语言以及开发流程的各个步骤几乎是一致的。对于大多数的初学者来说,学FPGA还是

2015-03-12 13:54:42

用vhdl实现cpld配置fpga,配置成功后在usermode下设置一个重新配置信号,当信号有效时对fpga进行重新配置;fpga配置程序放在flash内;现在遇到的问题是,上电cpld能够正常配置fpga并且进入usermode ,但是加上重新配置语句过后就不能成功配置fpga,求高人指点~

2013-01-17 22:35:39

Altera FPGA/CPLD设计与Verilog数字系统设计教程从网上找到了一些Altera FPGA/CPLD经典教材,包含夏宇闻老师的Verilog数字系统设计教程(第2版)Altera FPGA/CPLD设计与Verilog数字系统设计教程

2014-02-17 09:22:18

立题简介:内容:MCU+CPLD/FPGA实现GPIO扩展与控制;来源:实际得出;作用:MCU+CPLD/FPGA实现GPIO扩展与控制;仿真环境:Quartus II 11.0;日期

2021-11-04 07:42:16

] execute successfully..”即已完成 FPGA 或 CPLD的下载。

2. FPGA 的 Flash 固化

(1)FPGA 的 flash 固化需要先将.sbit 文件转换成 flash

2023-06-26 10:52:38

XILINX FPGA/CPLD ISE下载教程 第一章 XILINX FPGA/CPLD ISE下载教程——下载.bit文件第二章 XILINX FPGA/CPLD ISE下载教程——烧录Flash 图文详细资料!

2019-08-15 00:32:31

`内容简介· · · · · ·CPLD/FPGA是目前应用最为广泛的两种可编程专用集成电路(ASIC),特别适合于产品的样品开发与小批量生产。本书从现代电子系统设计的角度出发,以全球著名

2018-03-29 17:11:59

NOR闪存广泛用作FPGA的配置设备。FPGA在工业和通信及汽车ADAS应用中的使用取决于NOR Flash的低延迟和高数据吞吐量特性。快速启动时间要求的一个很好的例子是汽车环境中的摄像头系统。点火

2020-09-18 15:18:38

FPGA的配置,这里不得不提一下他们和CPLD内部存储介质的不同。CPLD由于大都是基于PROM或Flash来实现可编程特性,因此对他们进行在线编程时就已将配置数据流固化好了,重新上电后还能够运行固有

2016-07-27 16:45:59

请问哪位仁兄用过MCU、DSP或CPLD之类的芯片通过JTAG实现spartan-3AN(自带Flash)FPGA配置的?目前使用DSP+FPGA的架构硬件,想通过DSP实现FPGA的升级,目前想到

2014-08-05 16:18:37

、地连接到下载线即可。说到FPGA的配置,这里不得不提一下他们和CPLD内部存储介质的不同。CPLD由于大都是基于PROM或Flash来实现可编程特性,因此对他们进行在线编程时就已将配置数据流固化好了

2017-10-24 21:26:26

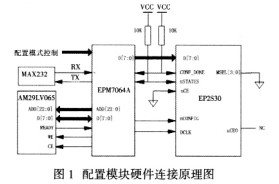

本文介绍了通过处理机用CPLD和Flash实现FPGA配置文件下载更新的方法。

2021-04-28 06:11:19

本文应用EDA技术,基于FPGA/CPLD器件设计与实现UART。

2021-05-07 06:33:09

伙计们,我的电路板提供了在FPGA处于硬复位状态时读取SPI闪存的能力(这种能力独立于FPGA;可以说是“侧读”)。假设我有一个具有有效FPGA配置的SPI Flash。如何确定SPI Flash中

2020-06-09 13:28:04

大家下午好,我计划使用主fpga板的IO引脚配置目标cpld板,即菊花链。我使用主fpga板的IO引脚连接cpld的JTAG头。如何编程master fpga的IO引脚来配置目标cpld?请发送与此相关的任何文件....谢谢问候Vimala

2020-03-24 06:43:09

从外部存储器将FPGA配置文件下载更新的方式有哪几种?如何用CPLD和Flash实现FPGA配置?

2021-04-08 06:07:22

数字系统的设计人员擅长在其印制电路板上用FPGA和CPLD将各种处理器、存储器和标准的功能元件粘合在一起来实现数字设计。除了这些数字功能之外,FPGA和CPLD还可以使用LVDS输入、简单的电阻电容(RC)电路和一些FPGA或CPLD的数字逻辑单元实现共模功能,从而构建模数转换器(ADC)。

2019-08-19 06:15:33

),有时我们不需要使用完整的UART的功能和这些辅助功能。或者设计上用到了FPGA/CPLD器件,那么我们就可以将所需要的UART功能集成到FPGA内部。使用VHDL将UART的核心功能集成,从而使整个设计更加紧凑、稳定且可靠。本文应用EDA技术,基于FPGA/CPLD器件设计与实现UART。

2012-05-23 19:37:24

FPGA/CPLD怎么验证是否正常工作? 现在手头上有一块板子,里面有FPGA/CPLD电路,芯片是Spartan-6系列的,现在已经有此芯片的FLASH烧写程序,也通过烧写器烧进flash,焊上

2020-06-14 09:04:40

如何通过添加一个简单的RC电路至FPGA或CPLD 的LVDS输入来实现模数转换器?请问怎么实现低频率(DC至1K Hz)和高频率(高达50K Hz)ADC?

2021-04-15 06:29:55

XC2S200型FPGA器件实现。采用Spansion公司的NOR Flash存储器来存放配置文件,其型号为S29GL512N,容量为512 Mb。系统总体框图如图3所示。上位机软件包括Flash烧写

2019-05-30 05:00:05

针对基于SRAM工艺的器件的下载配置问题,本文介绍采用AT89S2051单片机配合串行E2PROM存储器,实现CPLD/FPGA器件的被动串行(PS)模式的下载配置。

2021-04-13 06:25:40

《Altera FPGA/CPLD设计(高级篇)》结合作者多年工作经验,深入地讨论了Altera FPGA/CPLD的设计、优化技巧。在讨论FPGA/CPLD设计指导原则的基础上,介绍了Altera器件的高级应用;引领读者

2009-02-12 09:19:12 4799

4799 结合继电保护测试装置的研制体会,介绍基于DSP 的CPLD 多方案现场可编程配置方法,给出硬件的配置连接、CPLD 配置数据的获取与存储方法和CPLD 在DSP 控制下的被动串行配置过程。设

2009-04-15 08:50:55 29

29 为配合某电力测量仪表的开发,对Xilinx 公司的SpartanII 系列FPGA 的配置方案进行了探索。该方案采用大容量串行e- Flash 存储器MM36SB010 存放FPGA 配置文件,MCU 读取该配置文件并在被动串

2009-04-15 08:58:40 29

29 结合继电保护测试装置的研制体会,介绍基于DSP 的CPLD 多方案现场可编程配置方法,给出硬件的配置连接、CPLD 配置数据的获取与存储方法和CPLD 在DSP 控制下的被动串行配置过程。设

2009-05-18 14:33:24 16

16 altera fpga/cpld设计 基础篇结合作者多年工作经验,系统地介绍了FPGA/CPLD的基本设计方法。在介绍FPGA/CPLD概念的基础上,介绍了Altera主流FPGA/CPLD的结构与特点,并通过丰富的实例讲解

2009-07-10 17:35:45 57

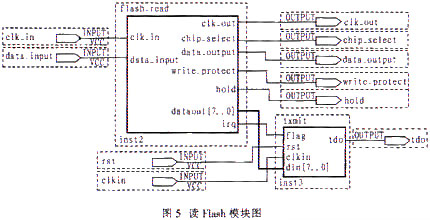

57 在使用Flash 存储数据时,有时需要对其设计读写控制逻辑。本文介绍了用VHDL 语言在CPLD内部编程,实现对Flash 中数据的读取控制的具体方法,并给出

2009-09-04 09:29:36 35

35 UART 是广泛使用的串行数据通讯电路。本设计包含UART 发送器、接收器和波特率发生器。设计应用EDA 技术,基于FPGA/CPLD 器件设计与实现UART。关键词 :FPGA/CPLD;UART;VHDLUART(即U

2009-09-29 08:01:20 23

23 基于单片机的CPLD/FPGA被动串行下载配置的实现:介绍采用AT89S2051单片机配合串行E2PROM存储器,实现CPLD/FPGA器件的被动串行模式的下载配置,阐述了其原理及软硬件设计。 &nb

2009-10-29 21:57:22 19

19 CPLD是复杂的可编程逻辑器件(Complex Programable Logic Device)的简称,FPGA是可编程门现场可编程门阵列,不同厂家有不同的称呼,Xilinx把SRAM工艺,要外挂配置用的EPROM的PLD叫FPGA,把Flash工

2009-11-12 14:22:36 117

117 当利用CPLD/FPGA开发系统完成数字电路或系统的开发设计并仿真校验通过之后,就需要将获得的CPLD/FPGA编程配置数据下载到CPLD/FPGA芯片中,以便最后获得所设计的硬件数字电路或系

2010-06-01 10:14:46 23

23 本文举例分析了DSP的引导装载过程和FPGA的配置流程,并据此提出了一种使用单个FLASH存储器实现上述两个功能的方法。

2010-07-21 17:14:42 12

12 摘 要 :UART是广泛使用的串行数据通讯电路。本设计包含UART发送器、接收器和波特率发生器。设计应用EDA技术,基于FPGA/CPLD器件设计与实现UART。

2009-06-20 13:14:52 982

982

基于CPLD/FPGA的多功能分频器的设计与实现

引言

分频器在CPLD/FPGA设计中使用频率比较高,尽管目前大部分设计中采用芯片厂家集成的锁相环资源 ,但是对于要求

2009-11-23 10:39:48 1139

1139

基于FPGA的串行Flash扩展实现

FPGA凭借其方便灵活、可重复编程等优点而日益被广泛应用;闪速存储器(Flash Memory)以其集成度高、成本低、使用方便等优点,在众多领域中

2010-01-12 10:39:55 1363

1363

FPGA重复配置和测试的实现

从制造的角度来讲,FPGA测试是指对FPGA器件内部的逻辑块、可编程互联线、输入输出块等资源的检测。完整的FPGA测试包括两步,一是配置FPGA

2010-01-26 09:39:56 544

544

常用FPGA/CPLD四种设计技巧

FPGA/CPLD的设计思想与技巧是一个非常大的话题,本文仅介绍一些常用的设计思想与技巧,包括乒乓球操作、串并转换、流水线操作和数据接口

2010-05-12 11:10:43 766

766

基于FPGA和CPLD数字逻辑实现ADC技术

数字系统的设计人员擅长在其印制电路板上用FPGA和CPLD将各种处理器、存储器和标准的功能元件粘合在一起来实现

2010-05-25 09:39:10 1309

1309

本文讨论的四种常用FPGA/CPLD设计思想与技巧:乒乓操作、串并转换、流水线操作、数据接口同步化,都是FPGA/CPLD逻辑设计的内在规律的

2010-11-04 10:11:28 625

625

本章将首先介绍FPGA配置方式和配置过程,然后简单介绍了配置芯片、配置文件的种类以及配置电路设计要点,本章最后讲述了配置文件下载、Flash编程等方面的内容,其中Flash编程包括

2011-03-22 10:53:46 801

801 SPI方式FPGA配置和SPI flash编程

2011-05-16 18:01:02 164

164 本文结合具体应用需求,介绍了利用嵌入式CPU Leon3软核处理器对Virtex系列FPGA的配置进行控制的方法。此系统能够实现FPGA配置数据的重构,并且减少了外围CPU和CPLD器件的使用,具有很好

2011-07-04 10:13:41 3151

3151

UART 是广泛使用的串行数据通讯电路。本设计包含UART 发送器、接收器和波特率发生器。设计应用EDA 技术,基于FPGA/CPLD 器件设计与实现UART。

2011-12-17 00:15:00 57

57 FPGA和CPLD的区别,以及设计思路思想

2016-02-17 11:20:56 38

38 SVPWM算法优化及其FPGA_CPLD实现

2016-04-13 15:42:35 18

18 基于FPGA/CPLD的UART功能设计

2017-01-23 20:45:37 30

30 的桥接的,难道FPGA内部有专用的电路去实现这一功能吗? 其实不是的。FPGA内部并没有设计(预留)专用的电路去实现JTAG到Flash的转换,在我们通过JTAG烧写Flash时,电脑其实是先要预下载

2017-02-08 02:40:11 6513

6513

CPLD和FPGA都是我们经常会用到的器件。有的说有配置芯片的是FPGA,没有的是CPLD;有的说逻辑资源多的是FPGA,少的是CPLD;有的直接就不做区分,把他们都叫做FPGA。那么两者到底有什么区别呢?下面我们就以Altera公司的CPLD和FPGA为例来说说两者的区别。

2017-09-18 16:35:32 5

5 FPGA/CPLD能完成任何数字器件的功能,上至高性能CPU,下至简单的74电路,都可以用FPGA/CPLD来实现。 FPGA/CPLD如同一张白纸或是一堆积木,工程师可以通过传统的原理图输入法

2017-10-09 09:52:20 14

14 随着FPGA的广泛应用, 其实现的功能也越来越多, FPGA 的动态重构设计就显得愈发重要。在分析Xilinx Vertex II Pro系列FPGA配置流程、时序要求的基础上, 设计了基于CPLD

2017-11-22 07:55:01 937

937

数字系统的设计人员擅长在其印制电路板上用FPGA和CPLD将各种处理器、存储器和标准的功能元件粘合在一起来实现数字设计。除了这些数字功能之外,FPGA和CPLD还可以使用LVDS输入、简单的电阻电容(RC)电路和一些FPGA或CPLD的数字逻辑单元实现共模功能,从而构建模数转换器(ADC)。

2018-04-26 11:53:00 1121

1121

在FPGA中实现在应用编程(In Application Programming,IAP)有两种方法:一种是,在电路板上加外电路。例如用MCU或CPLD来接收配置数据,在被动串行(PS)模式

2017-12-13 13:58:10 24009

24009

FPGA LAB和CPLD的LAB设计不同。CPLD LAB由宏单元构成,包括自己的本地可编程阵列,而FPGA LAB由大量的逻辑模块构成,这些模块被称为逻辑单元,即LE,而且本地互连和逻辑分开。LE看起来可能和CPLD宏单元相似,但更容易配置,有更丰富的特性来提高性能,减少逻辑资源的浪费。

2018-04-17 17:02:00 1979

1979

CPLD和FPGA都是我们经常会用到的器件。有的说有配置芯片的是FPGA,没有的是CPLD;有的说逻辑资源多的是FPGA,少的是CPLD;有的直接就不做区分,把他们都叫做FPGA。那么两者到底有什么区别呢?下面我们就以Altera公司的CPLD和FPGA为例来说说两者的区别。

2018-05-24 02:03:00 49472

49472

现代高速度FPGA运行时需将其配置数据加载到内部SDRAM中,改变SDRAM里面的数据,可使FPGA实现不同的功能,即所谓的可重构技术。可重构技术包括静态系统重构和动态系统重构。在FPGA处于工作

2019-06-10 08:17:00 2799

2799

CPLD通常用于实现前面提到的简单组合逻辑功能,并负责“引导”FPGA以及控制整个电路板的复位和引导顺序。

2018-09-27 11:56:01 6191

6191 介绍了采用CPLD和Flash器件对FPGA 实现快速并行配置,并给出了具体的硬件电路设计和关键模块的内部编程思路。

2018-10-24 15:15:49 7

7 Altera FPGA支持AS,PS,JTAG等几种较常见的配置方法。 当为AS配置模式时,FPGA为主设备,加载外部FLASH中的数据至内部RAM中运行。当为PS配置模式时,FPGA为从设备,外部

2018-11-18 18:05:01 481

481 本文档详细介绍的是FPGA教程之CPLD与FPGA的基础知识说明主要内容包括了:一、复杂可编程逻辑器件简介二、CPLD的组成与特点三、FPGA的组成与特点四、CPLD与FPGA的异同五、主要的PLD厂商

2019-02-27 17:09:32 32

32 本文档详细介绍的是FPGA教程之CPLD和FPGA的配置与下载的详细资料说明主要内容包括了:一、CPLD/FPGA器件的配置,二、MAX系列非易失性器件的下载配置,三、FLEX/ACEX系列FPGA的下载配置,四、ALTERA的编程文件

2019-02-28 09:56:18 17

17 与CPLD不同,FPGA是基于SRAM结构的(Actel也有基于Flash结构的FPGA,但不是今天讨论的重点),所以FPGA每次上电都需要重新配置,而不像CPLD那样能够直接运行固化在芯片内的代码

2019-03-05 14:16:27 6

6 对于CPLD/FPGA初学者而言,如何实现双向信号往往是个难题。duoduo 当年初接触CPLD/FPGA的时候也为这个问题头疼过。让我们透过下面这个简单的例子看看CPLD/FPGA设计中如何实现双向信号。

2019-06-11 16:13:51 15

15 CPLD和FPGA都是我们经常会用到的器件。有的说有配置芯片的是FPGA,没有的是CPLD;有的说逻辑资源多的是FPGA,少的是CPLD;有的直接就不做区分,把他们都叫做FPGA。

2019-09-13 14:58:00 5135

5135 FPGA/CPLD能完成任何数字器件的功能,上至高性能CPU,下至简单的74电路,都可以用FPGA/CPLD来实现。

2020-01-20 09:29:00 3264

3264 Altera CPLD和配置设备,并配置Altera FPGA设备。在你的设计成功编译后,你可以使用Quartus II程序员来编程或配置你的设备。

2020-09-17 14:41:00 32

32 本文主要介绍CPLD和FPGA的基本结构。 CPLD是复杂可编程逻辑器件(Complex Programable Logic Device)的简称,FPGA是现场可编程门阵列(Field

2020-09-25 14:56:33 12233

12233

CPLD/FPGA的基本知识讲解。

2021-03-30 09:55:18 27

27 FPGA_ASIC-DSP和FPGA共用FLASH进行配置的方法(哪些专业适合嵌入式开发)-该文档为FPGA_ASIC-DSP和FPGA共用FLASH进行配置的方法讲解文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-07-30 11:16:55 21

21 广义的来说,FPGA的配置包括直接使用下载电缆对FPGA器件进行编程、对外部EEPROM和FLASH进行编程、使用MPU对FPGA器件进行编程、外部EEPROM和FLASH对器件进行编程

2021-09-06 09:41:56 6052

6052 FPGA CPLD可编程逻辑器件的在系统配置方法(深圳市村田电源技术有限公司)-FPGA CPLD可编程逻辑器件的在系统配置方法

2021-09-18 10:51:20 13

13 Altera FPGA CPLD学习笔记(肇庆理士电源技术有限)-Altera FPGA CPLD学习笔记

2021-09-18 10:54:41 79

79 FPGA CPLD中的Verilog设计小技巧(肇庆理士电源技术有限)-FPGA CPLD中的Verilog设计小技巧

2021-09-18 16:49:18 35

35 立题简介:内容:MCU+CPLD/FPGA实现GPIO扩展与控制;来源:实际得出;作用:MCU+CPLD/FPGA实现GPIO扩展与控制;仿真环境:Quartus II 11.0;日期

2021-10-29 10:21:11 2

2 都是FPGA/CPLD逻辑设计的内在规律的体现,合理地采用这些设计思想能在FPGA/CPLD设计工作种取得事半功倍的效果。

2023-05-18 08:56:57 350

350

CPLD和FPGA都是由逻辑阵列模块构成的,但是CPLD的LAB基于乘积和宏单元,而FPGA的LAB使用基于LUT的逻辑单元。

2023-06-28 11:28:04 862

862

可编程逻辑包括 PAL、GAL、PLD 等。通过不断发展,它已经发展成为现在的CPLD/FPGA。CPLD(复杂可编程逻辑器件)和FPGA(现场可编程门阵列)的功能基本相同,只是实现原理略有不同

2023-07-03 14:33:38 6041

6041

FPGA(现场可编程门阵列)是一种高度灵活的硬件设备,可以根据特定的需求进行重新配置。FPGA通常用于处理大量数据和实时计算。然而,FPGA通常并没有内置大容量的数据存储器,例如硬盘或固态硬盘。这就

2023-12-15 15:42:51 544

544

正在加载...

电子发烧友App

电子发烧友App

评论