通过上一篇文章“时钟管理技术”,我们了解Xilinx 7系列FPGA主要有全局时钟、区域时钟、时钟管理块(CMT)。 通过以上时钟资源的结合,Xilinx 7系列FPGA可实现高性能和可靠的时钟分配

2023-08-31 10:44:31 1032

1032

嗨,我使用的是virtex 5 FPGA。我正在运行外部10Mhz时钟信号来运行二进制计数器。当我尝试使用DCM时,它表示最低频率为32MHz。可以将此信号运行到FPGA的i / o输入并通过全局

2019-02-21 10:32:51

28377D的I/O输出响应时间受系统时钟影响吗?最近在使用2M*16的FLASH,但是28377D 得EMIF地址只能够访问到1M地址空间,此时用I/O做其高位地址线,现在想知道I/O响应

2020-05-29 09:41:39

能够对这些数据进行处理。以下两个例子说明了FPGA的I/O结构的发展。源同步接口在源同步接口中,发送器芯片发送数据字和数据采样时钟至接收器。接收器芯片使用时钟来采集数据。从理论上说,源同步接口的速度

2018-11-26 11:17:24

FPGA 时钟分配网络设计技术

2012-08-20 17:15:27

,这就按照连线最短的原则将对应的信号分配到与外部器件连线最近的BANK 中,2 、 掌握FPGA 内部BANK 的分配的情况。 现在FPGA 内部都分成几个区域,每个区域中可用的I/O 管脚数量各不相同

2012-08-11 10:27:54

说说专用时钟引脚,它的出现具体原因可以说是FPGA自身的实现结构引起的,FPGA实现时,具体的时钟大概有外部供给FPGA的工作时钟,由DCM或者PLL产生的时钟,和FPGA输入输出数据的随路时钟;再说

2019-07-09 08:00:00

FPGA中的I_O时序优化设计在数字系统的同步接口设计中, 可编程逻辑器件的输入输出往往需要和周围新片对接,此时IPO接口的时序问题显得尤为重要。介绍了几种FPGA中的IPO时序优化设计的方案, 切实有效的解决了IPO接口中的时序同步问题。

2012-08-12 11:57:59

`引脚分配规划和扩展I/O电路本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 核心板上专门留了一个LED

2015-05-06 11:31:16

电路设计的可选择性丰富而言的。话说回来,这里的“自由”也还是要建立在一定的基础之上的。笔者根据多年的工程经验,对于I/O与外设的连接扩展,归纳出以下一些要点:●输入和输出时钟信号尽量分配到专用的引脚

2019-04-12 06:35:33

FPGA的I/O结构的发展的怎么样了?

2021-04-29 06:12:52

喜我对时钟门控有一些疑问。从我所读到/学到的东西 - 时钟门控可用于低功率fpga设计(关闭时钟以防止元件切换以节省功率)。但是,我还读到时钟门控很糟糕,因为它可能会引起系统故障。我想我已经看到了

2019-02-21 10:21:41

FPGA 内部 BANK 的分配的情况。现在 FPGA 内部都分成几个区域,每个区域中可用的 I/O 管脚数量各不相同。在 IC 验证中都是采用了ALTERA 与XILINX系列的FPGA ,这两个厂商

2024-01-10 22:40:14

的 BANK 中。 2、 掌握 FPGA 内部 BANK 的分配的情况。现在 FPGA 内部都分成几个区域,每个区域中可用的 I/O 管脚数量各不相同。在 IC 验证中都是采用了ALTERA 与XILINX系列

2017-03-25 18:46:25

/O信号分配 可提供最多的多功能引脚、I/O标准、端接方案和差分对的FPGA在信号分配方面也具有最复杂的设计指导原则。尽管Altera的FPGA器件没有设计指导原则(因为它实现起来比较容易),但赛灵思

2020-09-07 11:01:46

:图2:Spartan-7 FPGA同一bank连接1.8V SPI Flash和1.35V DDR3L虽然这不是一个标准的解决方案,只是限于有限的I/O资源,但是对于小型系统设计不失为一种好的方法。具体设计细节如器件选型、原理图、确定时钟频率等要求请参看官方文档`

2018-08-02 09:37:08

你好,我是新的virtex 4设计师。有人可以告诉I / O和时钟区域之间的关系。这可能是一个时钟能够i / o驱动多个BUFIO和更进一步的BUFR?提前致谢。求爱

2020-06-03 07:22:35

fpga I/O 引脚都一样吗?为什么有些管脚只能分配为输入,有的只能为输出?求大神指点

2015-05-27 08:12:40

PIC32MX795F512L,所有PIC管脚都有断路,8个LED可以跳到,一个开关,SPI连接的微SD卡和USB端口。运行代码配置器,设置时钟,定时器0和PORTA 0-7上的I/O管脚作为输出。当我生成代码

2019-10-21 06:38:23

分配fpga管脚时该怎么选择,引脚有什么属性需要考虑,quartus2中引脚有几个属性:Reserved,Group,I/O Bank,Vref Group,I/O standard( 3.3-V

2019-04-03 07:00:00

通过前面的输入输出的内容(LED控制与按键的使用),我们对控制I/O口有了一个基本的了解。如果需要输出高低电平,可以对该引脚进行写"1"或者"0";如果需要

2022-01-24 07:38:13

嗨, 我想把晶体振荡器的CLK带到FPGA里面的数字设计。该CLK连接到FPGA的I / O引脚。如果我在映射中运行Impliment设计,我将得到错误。所以我将在UCF文件中将网名命名如下。NET

2019-01-29 10:05:43

控制系统为核电厂提供了各种控制和保护手段及监控信息,保证了核电厂在正常启动、停堆、异常和事故工况下能够安全、可靠和有效运行。DCS系统I/O分配原则及I/O分配方法 yunrun.com.cn/tech

2018-02-22 13:18:08

使用INIT_B引脚(内部路由)作为标记非FPGASEU检查结果的通用I / O,此外还可以根据积分配置错误检查结果进行驱动。我看到INIT_B被描述为“Dedicated”(UG362,表2-2,第27页),所以我不确定它是否可以作为通用I / O运行。如果没有,我需要专门为此目的的另一个输出引脚。

2020-06-10 15:09:16

将这些信号和FPGA的引脚进行映射。 如图所示,点击ISE菜单上的“Tools à PlanAhead à I/O Pin Planning(PlanAhead) – Pre-Synthesis…”选项

2015-10-14 12:23:31

labview怎么实现像plc一样的通过输入输出I/O量,控制开关量,比如通过I/O点控制继电器的吸合。怎么给I/O量分配地址,怎么在程序里使用这些变量实现一系列有序的动作。希望能附上一份样例程序,让小弟学习领会,请多指教,谢谢。

2016-04-25 00:51:33

我想使用外部1K Hz时钟或写入遇到代码将时钟分配到K Hz电平,它会起作用吗? 第二个问题是如何定义I / O类型,我想使用单个lvcmos3.3V作为I / O标准。我应该在哪里定义I / O标准?在代码中我还是需要将供应跳线改为3.3位置?感谢您的帮助!

2020-04-29 09:22:03

外部时钟信号。• rst_I 同步重起信号。• arst_I 异步重起信号。• adr_I 从节点地址。• dat_I 输入数据。• dat_o 输出数据。• we_I 写有效信号。• stb_I

2018-10-09 11:28:28

时钟XCLK引脚用定时器来控制I/O做10M时钟,没行通,也不知道这种方法可不可行。想问下官网工程师们能不能替我解决下问题。。

2020-04-09 15:39:38

I/O控制对于单片机而言是最基础最核心的东西,其实单片机除了模/数转换之外的事情。其他大部分的事情I/O口都能做的到。I/O控制简单却能千变万化。单片机在大部分应用中做的事情,莫过于 输入高低

2021-11-24 06:47:23

美国国家仪器有限公司(National Instruments,简称NI)近日针对PXI平台,推出了一个全新的、开放式的、基于FPGA的产品系列。NI FlexRIO系列产品是工业领域首款成熟商用现成产品,它为工程师们提供了同时结合高速、工业级I/O和NI LabVIEW FPGA技术的解决方案。

2019-10-29 07:03:11

(从而将输入输出时延控制在允许的范围内),需要在时钟驱动器和负载之间插入时钟缓冲器。DCM可用作时钟输入引脚和逻辑块之间的时钟缓冲器。 最后,还可以使用DCM将输入时钟信号转换为差分I/O标准

2020-04-25 07:00:00

嗨,我使用的是Virtex-7 FPGA。我们通过专用时钟引脚等成功设置了多个时钟输入。然而,当我使用标准I / O引脚作为时钟输入时,我无法获得synplify-rpo 2014.09将输入识别为“声明”时钟。我总是得到一个推断时钟,这打破了门控时钟树构建下来。任何帮助赞赏。西蒙

2020-07-30 08:30:40

,而是指着电路设计的可选择性丰富而言的。话说回来,这里的“自由”也还是要建立在一定的基础之上的。笔者根据多年的工程经验,对于I/O与外设的连接扩展,归纳出以下一些要点:● 输入和输出时钟信号尽量分配到专用

2016-07-30 18:19:39

`勇敢的芯伴你玩转Altera FPGA连载49:PWM蜂鸣器驱动之引脚分配特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1i

2018-02-27 21:50:07

CPU、ASIC 或 FPGA 等数字电路。电源旁路将帮助过滤掉其中一部分噪声,而剩下的噪声则将影响器件性能。在剩余噪声影响时钟分配器件电源时,会导致窄带相位调制以及时钟输出的幅度调制。在 100kHz

2018-09-17 16:12:25

走线将CCLK输出引脚连接到另一个FPGA I / O引脚,还是可以在内部连接到它?我没有看到有CCLK的原理图库部件。有没有办法做到这一点?谢谢你,-J以上来自于谷歌翻译以下为原文If i read

2019-05-07 13:40:54

大家好,我刚开始学习FPGA并试图弄清楚哪些FPGA引脚可以分配我的数据信号。我正在使用FPGA Spartan 6封装TQG114器件LX9。查看产品规格,有102个可用的用户I / O.这是

2019-04-23 06:55:23

先分配差分I/O。然后,分配电压参考I/O和相关的VREF管脚,它们可以从任何绑定的I/O中进行配置。最后,对所有其它单端I/O进行分配。Altera:虽然灵活的管脚分配对FPGA很重要,但某种程度

2012-02-27 15:18:09

的 BANK 中2、 掌握 FPGA 内部 BANK 的分配的情况。现在 FPGA 内部都分成几个区域,每个区域中可用的 I/O 管脚数量各不相同。在 IC 验证中都是采用了ALTERA

2015-01-06 17:38:22

TinyOS系统下的I/O控制程序,并给出在CC2340芯片上实现的结果,可用来控制对Sink节点的输入和输出.对该程序进行一定的扩展和改进便可以实现对Sink节点与节点通信和数据传输的控制. 0

2018-11-13 16:27:39

同步数字系统中的时钟信号(如远程通信中使用的)为系统中的数据传送定义了时间基准。一个时钟分配网络由多个时钟信号组成,由一个点将所有信号分配给需要时钟信号的所有组件。因为时钟信号执行关键的系统功能,很显然应给予更多的关注,不仅在时钟的特性(即偏移和抖动)方面,还有那些组成时钟分配网络的组件。

2019-10-16 07:11:33

大家好,我使用PIC18F4620 40PIN DIP封装,大约30的I/O引脚没有使用。我不知道我应该把它们留在硬件中,还是应该把它们绑定到VDD或VSS?在软件中也推荐使用未使用的I/O引脚

2019-01-25 14:33:08

我是使用virtex 4的先行者。我正在使用ISE xilinx13.1和verilog。我通过配置LVCOM33,拉式无,转换速率快,为j6端口的pin2分配了一个时钟输入信号。但我无法观察到波形。任何人都可以指导我 - 如何使用I / O?

2019-09-04 10:35:35

如何克服FPGA I/O引脚分配挑战?

2021-05-06 08:57:22

如何在PlanAhead I / O引脚分配中启动LVDS系统时钟? I / O STD列中没有LVDS选项?

2019-09-17 08:19:59

正确。我的问题是 - 1)警告可以被忽略吗?如果没有,我怎么能摆脱上述警告?我只在CPLD实施的情况下看到它。如果我将设备更改为virtex FPGA,警告就会消失2)如何约束内部生成的i2s_o时钟

2019-04-12 14:24:54

你好先生:我有一个关于Spartan-6时钟I / O引脚的问题,数据表“UG382第24页”就是说“P和N输入遵循与时钟输入引脚上的标准输入相同的配置”,但我不知道其含义这个描述。我想这意味着

2019-07-15 14:04:11

嗨专家,我正在使用Spartan3AN(XC3S50AN)FPGA板和平台线USB II。你能告诉我如何通过JTAG监控PC中FPGA I / O的状态吗?谢谢,V。Prakash以上来自于谷歌翻译

2019-06-18 09:05:14

一定能够满足特殊 I/O 的需要。 近期最值得一提的技术跃进,即为适用于 PXI 的 NI FlexRIO 硬体;不仅整合了其他 NI 系统中的 LabVIEW FPGA 技术,并具有开放式的使用者客

2019-04-28 10:04:14

嗨,我是第一次在Fpga工作。我为所有32个收发器提供125 MHz差分时钟。现在我需要为I / O bank提供125 MHz差分时钟。有没有办法使用GTX时钟用于这个目的(正如我读到的,MRCC

2020-07-15 09:48:46

使用器件XC2S100E-6TQ144,我需要将4个GCK引脚中的3个配置为通用I / O引脚。第4个GCK用作100MHz时钟。当我使用其他3个GCK引脚作为通用I / O引脚时,在“器件

2019-05-08 08:00:24

图片一是我需要110个I/O接口,图片二是板子的所有接口,问一下我该如何分配接口?????

2016-10-25 15:05:04

我想用布尔开关来控制I/O输出的高低电平,请问出现图片这种情况,该怎么解决。还有如果要用8个开关控制8个口要用8个DAQ助手还是可以合在一起的。

2017-05-13 23:01:59

大家好,物理封装引脚分配完成后,ISE自动推断I / O芯片分配使用LOC约束。有没有办法明确分配特定的I / O芯片垫?谢谢。以上来自于谷歌翻译以下为原文Hi All, ISE

2019-02-14 12:12:04

大家好,我想检查FPGA功能和I / O引脚功能在我的主板上使用“Selftest application”。在我的Selftest应用程序中,我可以使用哪些方法来检查这些?请提供一些想法。谢谢

2019-04-01 12:33:26

FPGA的I/O口如果作为input,输入外部控制信号,电平还有其他设置等等,与作output时有什么区别?

2016-06-21 12:50:04

求西门子PLC控制沼气发电程序 I\o分配表谢谢

2016-10-15 16:16:11

您好,最近在设计一款雷达,发射板、接收板、和信号处理板,发射板使用的是FPGA控制+PLL产生发射波形和本振,想知道这个FPGA的时钟、PLL的时钟,信号处理板的时钟,是使用一个晶振的来分配时钟呢

2019-01-02 15:36:07

轻松实现高速串行I/OFPGA应用设计者指南输入/输出(I/O)在计算机和工业应用中一直扮演着关键角色。但是,随着信号处理越来越复杂,I/O通信会变得不可靠。在早期的并行I/O总线中,接口的数据对齐

2020-01-02 12:12:28

使用LabVIEW FPGA 模块和可重新配置I/O 设备开发测量与控制应用通过使用LabVIEW FPGA 模块和可重新配置I/O(RIO)硬件,NI 为您提供了一种直观可用的解决方案,它可以将

2009-07-23 08:15:57

FPGA怎么选择?针对功耗和I/O而优化的FPGA介绍

2021-05-06 09:20:34

一种FPGA时钟网络中锁相环的实现方案:摘 要:本文阐述了用于FPGA 的可优化时钟分配网络功耗与面积的时钟布线结构模型。并在时钟分配网络中引入数字延迟锁相环减少时钟偏差,探

2009-08-08 09:07:22 25

25 本文阐述了用于FPGA的可优化时钟分配网络功耗与面积的时钟布线结构模型。并在时钟分配网络中引入数字延迟锁相环减少时钟偏差,探讨了FPGA时钟网络中锁相环的实现方案。

2010-08-06 16:08:45 12

12 摘要:介绍了为PET(正电子发射断层扫描仪)的前端电子学模块提供时间基准而设计的一种新型高频时钟扇出电路。该电路利用FPGA芯片来实现对高频时钟的分频

2009-06-20 12:41:04 1238

1238

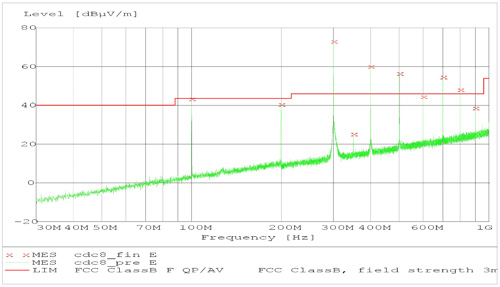

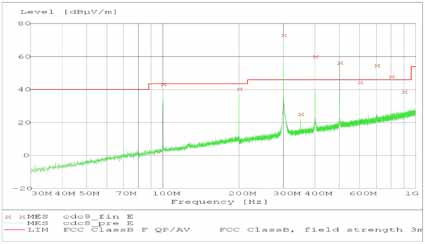

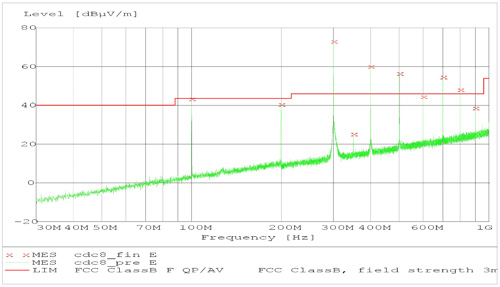

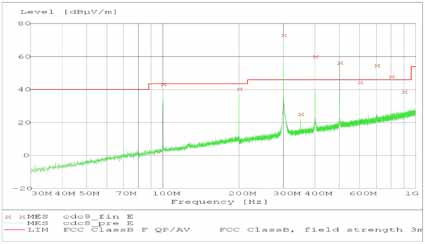

控制板级时钟分配期间出现的EMI

今天,我们来谈谈所有电子系统都存在的一种常见问题——电磁干扰也即 EMI,并侧重讨论时钟的影响。

从广义来讲,EMI&n

2010-01-19 11:13:14 1958

1958

控制板级时钟分配期间出现的 EMI

今天,我们来谈谈所有电子系统都存在的一种常见问题——电磁干扰也即 EMI,并侧重讨论时钟的影响。

从广义来讲,EMI 是

2010-01-21 09:36:19 874

874

在FPGA设计中,为了成功地操作,可靠的时钟是非常关键的。设计不良的时钟在极限的温度、电压下将导致错误的行为。在设计PLD/FPGA时通常采用如下四种类型时钟:全局时钟、门控时钟

2011-09-21 18:38:58 3472

3472

设计过FPGA的原理图,看FPGA的手册,说管脚的分配问题,如时钟管脚要用GC类管脚,而且单端时钟输入时要用P类型的管脚,不能用N类型管脚等等。

2017-02-11 03:48:34 10684

10684

本文档的主要内容详细介绍的是spartan-6 FPGA的时钟资源的用户指南资料免费下载。

2019-02-15 16:39:07 27

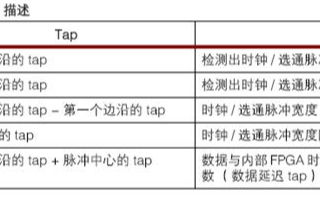

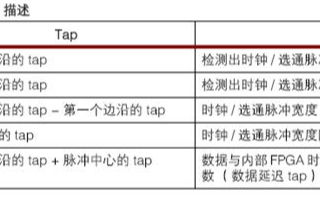

27 ,并与内部 FPGA 时钟实现中心对齐。在这个方案中,内部 FPGA时钟采集传出的数据。存储器传出的时钟/ 选通脉冲用于决定与数据位相关的延迟值。因此,与选通脉冲相关的数据位的数量不受限制。由于无需将选通脉冲分配给相关数据位,所以不需要其他时钟资源。

2020-11-26 10:01:31 1219

1219

本文档的主要内容详细介绍的是FPGA硬件基础之理解FPGA时钟资源的工程文件免费下载。

2020-12-10 14:20:11 6

6 本文档的主要内容详细介绍的是FPGA硬件基础之FPGA时钟资源的工程文件免费下载。

2020-12-10 15:00:29 15

15 超低抖动时钟的产生与分配

2021-04-18 14:13:51 8

8 基于FPGA的数字时钟设计毕业设计论文免费下载。

2021-05-28 10:49:19 56

56 本章的主要内容: 分析时钟驱动器、时钟信号的特殊布线 改进时钟信号分配的特殊电路

2022-09-20 14:55:40 0

0 如何优化 PCIe 应用中的时钟分配

2022-11-07 08:07:15 0

0 控制板级时钟分配期间出现的 EMI

2022-11-07 08:07:32 0

0 电子发烧友网站提供《使用FPGA的数字时钟(计时表).zip》资料免费下载

2022-11-23 10:38:36 5

5 基于FPGA的高频时钟的分频和分频设计

2023-08-16 11:42:47 0

0 第11章时钟分配

2022-12-30 09:21:58 2

2

电子发烧友App

电子发烧友App

评论