138译码器的设置目的是为了实现IO复用,单片机上IO资源紧张,挂载的外设较多,为了解决这一矛盾,引入了138译码器单个138译码器能够利用3个IO实现8路选择(在逻辑上相当于扩展了5个IO),比赛

2022-01-12 07:25:11

看完74hl138译码器的技术文档,就编了这个。很好用的芯片。{:soso_e130:}

2012-08-19 00:54:06

3 -8译码器 不知怎么仿真波形弄不出来,主要是输出引脚的波形有问题,希望大家能给以指导,感谢大家!!!

2014-06-12 21:41:50

74LS138译码器是什么?74LS138译码器的扩展方法是什么?

2022-01-19 07:14:36

的器件只能作十进制BCD码译码,然而数字系统中的数据处理和运算都是二进制的,所以输出表达都是十六进制的,为了满足十六进制数的译码显示,最方便的方法就是利用译码程序在FPGA/CPLD中来实现。图4-1

2009-10-11 09:22:08

论坛里面的大神们,有没有已经完成LDPC码编译码算法的FPGA实现,本人目前在做这方面的项目,时间比较紧,紧急求购IP核。。

2012-04-16 23:43:28

第一次发帖,自己仿真的一个译码器,谢谢大家!

2016-03-22 13:34:35

译码器及其应用实验

2017-03-21 13:36:44

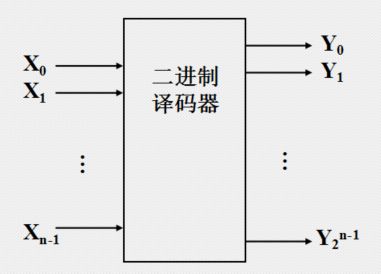

译码器1. 译码器定义译码器是一种用以检测输入位(码)的特定组合是否存在,并以特定的输出电平来指示这种特定码的存在的数字电路。——《数字电子技术基础系统方法》译码器的功能是将具有特定含义的二进制码

2021-12-07 09:37:27

这是译码器的一些资料。

2014-07-13 11:59:08

。TTL、CMOS又没有现成译码器可用。故而用二极管搭建此特殊译码器,简单、可靠低成本与现有系统亲和度高。我的高一级的产品显示部分用的是人机界面。

2016-11-17 09:40:39

,OFF,ON1D7点亮 ONON,ON,OFF1D8点亮 ONON,ON,ON1D9点亮注:X表示ON或OFF,即任意状态。 2 板级调试下载sp6.bit文件到FPGA中,可以如图视频一样操作拨码开关,实现3-8译码器的功能。 `

2015-11-02 13:17:03

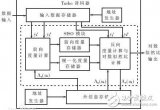

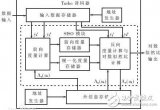

【作者】:申睿;邓运松;向波;陈赟;曾晓洋;【来源】:《小型微型计算机系统》2010年03期【摘要】:提出一种通用的QC-LDPC码译码器架构.该架构采用一种特殊的绑定结构和一个可配置的循环移位网

2010-04-24 09:26:56

芯片,这种数字芯片由简单的输入逻辑来控制输出逻辑,比如 74HC138这个三八译码器,图 3-15 是 74HC138 在我们原理图上的一个应用。从这个名字来分析,三八译码器,就是把 3 种输入状态...

2021-07-19 09:08:52

什么是3-8译码器,急啊,速求

2013-03-26 16:52:38

将译码器的使能端看做输入端、译码器的输入端看做地址端,则全译码器可作什么使用

2015-05-18 11:41:06

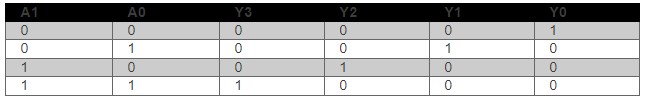

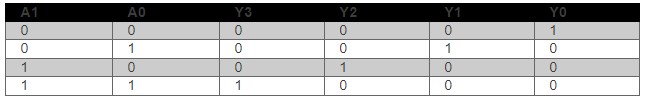

可以baidu或bing一下。相信学习FPGA的读者一定都上过数字电路的课程,所以这里对3-8译码器功能的实现给个真值表,如表8.1所示,一目了然。表8.1 3-8译码器真值表[tr

2018-03-26 16:13:33

译码器有哪些功能?Viterbi译码器是由哪几部分组成的?

2021-05-07 07:28:33

的?还有这篇文章是2010年发表的了,如今汉明码译码器的FPGA实现是否有更好的实现方法呢?有大神可以给我提供一个思路吗?or2万分感谢

2020-02-26 23:29:41

【摘要】:Viterbi译码器在通信系统中应用非常普遍,针对采用DSP只能进行相对较低速率的Vit-erbi译码的问题,人们开始采用FPGA实现高速率Viterbi译码。本文首先简单描述了

2010-04-26 16:08:39

对不同的设计方法进行分析和比较,选择优化的设计方法,利用VHDL分别设计(15,7)BCH码的编码器和译码器,并能够对两部分进行单独仿真调试,实现其相应的功能。

2012-05-10 11:36:06

在DIY的时候,有多元的选择是最好的。不同品种,不同的厂家,可必免断供,不同的型号可避免涨价打消制作的想法。在CPU或MCU中译码器器至关重要,多位译码器可使用74138多片联级,4位译码器可选

2022-10-02 16:40:44

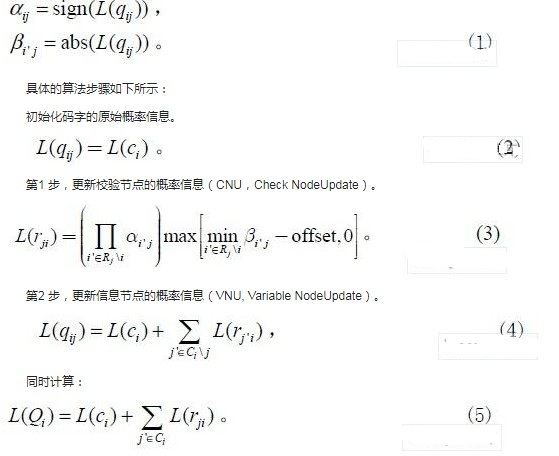

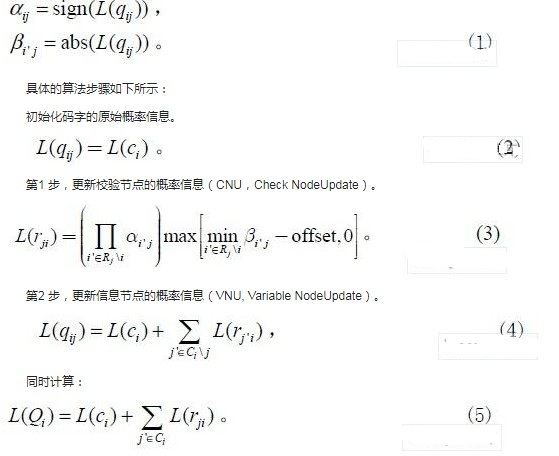

LDPC码是近年来发展较快且日趋成熟的一种信道编码方案,因其具有的优越性能和实用价值而被人们认知,但由于随机结构的LDPC码编译码器硬件实现较为复杂,具有的准循环特性QC_LDPC码已成为IEEE802.11n(WiFi)、IEEE802.16e(WiMAX)、(DVB—S2)等众多标准的信道编码方案。

2019-09-30 07:19:45

显示译码器是什么?如何准确设计出符合功能要求的显示译码器?

2021-06-01 06:58:12

增加一些监督码元,这些监督码与信码之间有一定的关系,接收端可以利用这种关系由信道译码器来发现或纠正错误的码元。

2019-08-15 06:12:00

集成电路编码器和译码器的工作原理即逻辑功能是什么?如何利用逻辑门去实现一种集成电路编码器呢?如何利用译码器进行组合逻辑电路的设计呢?

2021-11-03 06:55:24

如何利用VHDL实现线性分组码编译码器的设计?

2021-04-28 06:41:40

本文通过对长BCH码优化方法的研究与讨论,针对标准中二进制BCH码的特性,设计了实现该译码器的FPGA硬件结构。

2021-06-15 09:23:27

BCH码是目前最为常用的纠错码之一,我国的数字电视广播地面传输标准DTMB也使用了缩短的BCH码作为前向纠错编码的外码。针对该BCH码的特点,采用BM译码算法,设计了一种实时译码器。与其它设计方案

2021-05-25 07:04:32

本文研究了RS码的实现方法,并基于Xilinx的FPGA芯片Spartan-6 XC6SLX45完成了RS编译码器的设计,同时对其进行了仿真和在线调试,并给出了功能仿真图和测试结果。时序仿真结果表明,该编译码器能实现预期功能。

2021-06-21 06:23:53

了一种合适的硬件实现结构,因而在保证译码器较高性能和较快译码速度的情况下,以较低的硬件资源实现了两种码率的复用。

2019-08-23 07:22:50

基于FPGA的Turbo码编译码器各模块实现的 VHDL或verilog HDL程序。急求啊谢谢大神啦!!

2015-06-08 22:45:24

截短Reed-Solomon码译码器的FPGA实现提出了一种改进的BM算法,并在此基础上提出了一种大量采用并行结构的截短RS码译码器的实现方式。验证表明,该算法能显著提高基于FPGA的RS译码器

2009-09-19 09:39:43

截短Reed_Solomon码译码器的FPGA实现提 出 了 一 种 改 进 的 算 法 并 在 此 基 础 上 提 出 了 一 种 大 量 采 用 并 行 结 构 的 截 短 码译 码 器 的 实

2012-08-11 15:50:06

标准中LDPC码的构造、编码及解码算法原理,结合MAT-LAB仿真对其算法有效性进行了分析比较。【关键词】:数字电视传输系统;;低密度奇偶校验码;;DMB-TH;;编译码器【DOI】:CNKI:SUN

2010-04-23 11:36:52

毕业设计 基于EDA的CMI码编码译码器的设计,共20页,7505字 摘要 CMI码是一种应用于PCM四次群和光纤传输系统中的常用线路码型,它具有码变换设备简单、便于时钟提取、有一定的纠错能力

2009-03-25 13:19:20

求multisim数码显示译码器仿真!!!!译码器是CC4511。。。。。我的调不太通,希望看看大神做的成品,参考一下!!!!,很急!

2015-12-21 21:13:26

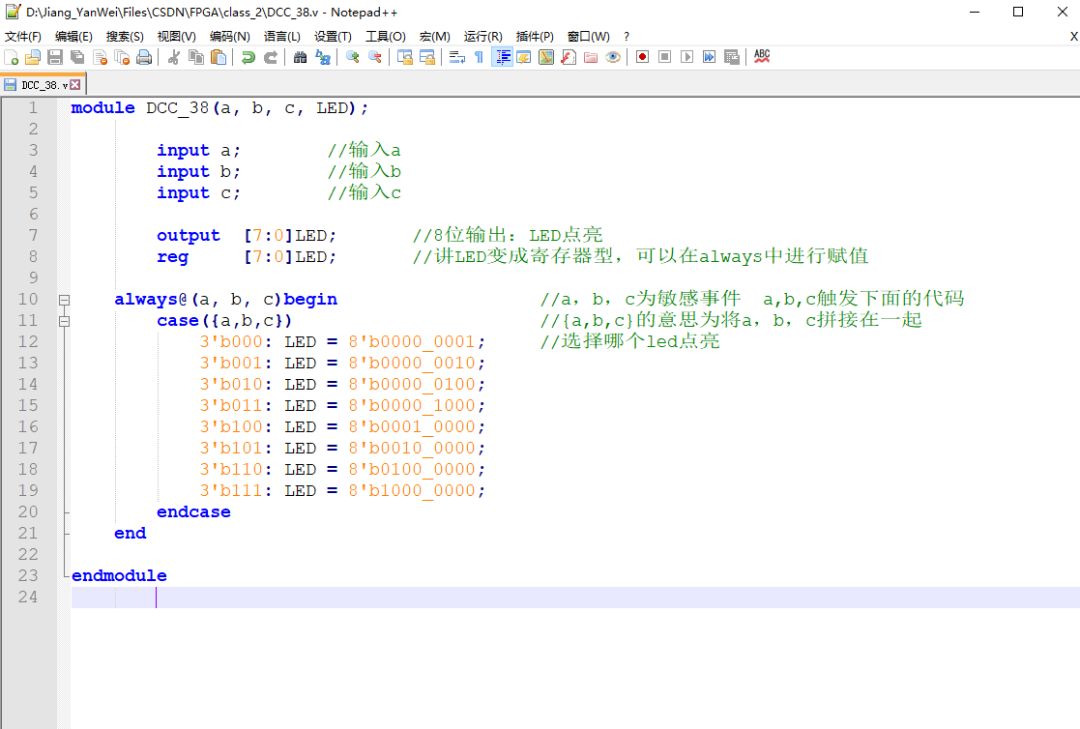

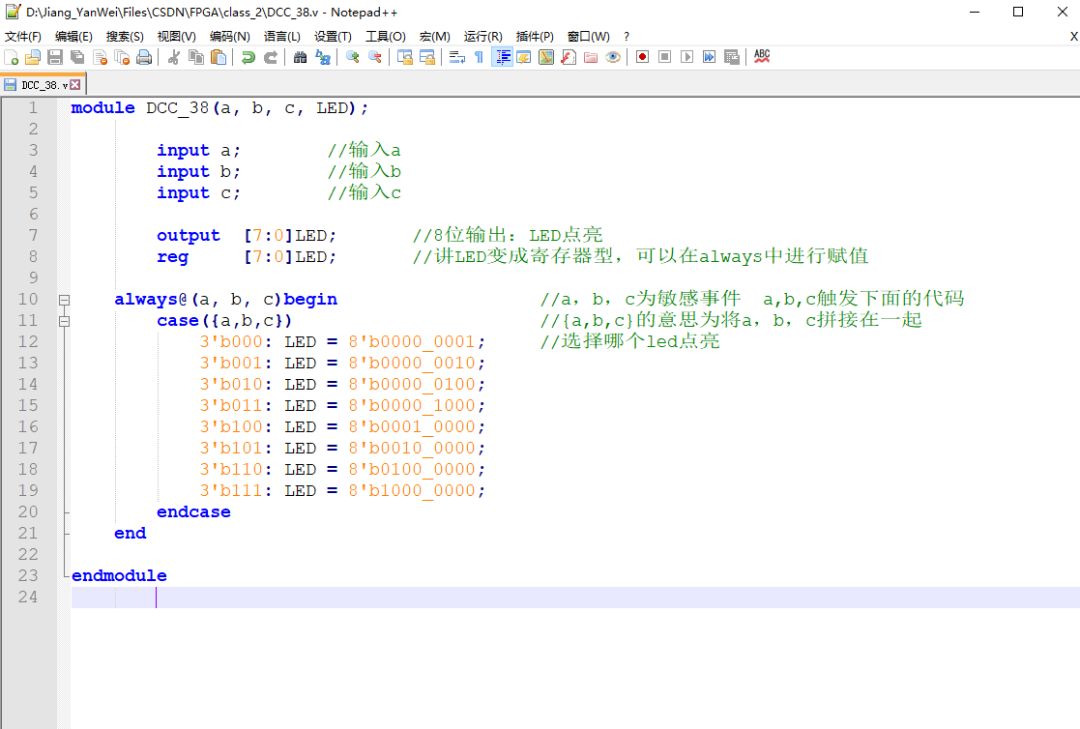

1、在FPGA中使用行为描述语句实现3-8译码器设计思路译码器电路有n个输入和2n个输出,每个输出都对应着一个可能的二进制输入。本实验设计实现一个3-8译码器,表3.1给出了该译码器的真值表。从

2022-07-01 15:26:26

Turbo码编码器的FPGA实现Turbo码译码器的FPGA实现Turbo码编译码器的性能有哪些?

2021-05-07 06:06:23

编码器和译码器一、 实验目的掌握用逻辑门实现编码器的方法掌握中规模集成电路编码器和译码器的工作原理即逻辑功能掌握 74LS138 用作数据分配器的方法熟悉编码器和译码器的级联方法能够利用译码器进行

2021-07-30 07:41:16

设计一个虚拟3-8译码器,实现138译码器的功能

2012-05-15 15:16:39

设计一个虚拟3-8译码器,实现138译码器的功能!急急急{:soso_e183:}

2012-05-15 15:12:44

在做HDB3码编译码器的实验,查到资料说FPGA只能处理单极性码,而HDB3码是双极性码。想请教下是所有的FPGA的芯片都只能处理单极性码么?如果是的,那么想处理双极性码的话要加什么样的辅助电路才能用FPGA处理双极性码?

2016-09-14 16:31:36

本文在SvstemGenerator中对LDPC码整个编译码系统进行了参数化的硬件实现,并构建了超宽带通信系统LDPC码硬件仿真平台,验证了LDPC码在UWB通信中的优异性能。

2021-06-03 07:01:58

Reed_Solomon码译码器的FPGA实现快速浮_定点PID控制器FPGA的研究与实现一种密钥可配置的DES加密算法的FPGA实现应用于LTE_OFDM系统的Viterbi译码在FPGA中的实现[hide][/hide]

2012-02-02 17:26:14

针对LDPC码与RS码的串行级联结构,提出了一种基于Chase的联合迭代译码方法。软入软出的RS译码器与LDPC译码器之间经过多次信息传递,性能可以逼近最大似然译码。模拟结果显示:

2009-05-12 21:47:25 22

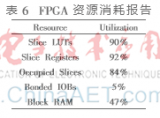

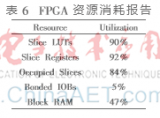

22 本文基于Altera的FPGA(StatixⅡ-EP2S30F484C3)架构,实现了码率为1/2,帧长为1008bits的规则(3,6)LDPC码译码器。所采用的最小-和算法相对于传统的和-积算法在不损失译码性能的前提下,

2009-06-06 14:12:20 31

31 面向IEEE 802.16e 中 LDPC 码,分析了各种译码算法的译码性能,归一化最小(NMS)算法具备较高译码性能和实现复杂度低的特点。提出一种基于部分并行方式的LDPC 译码器结构,可以满

2009-08-05 08:46:59 24

24 循环移位置换单元是准循环LDPC 码的部分并行译码器的重要组成部分。该文研究并证明了ReverseBanyan 交换结构在实现信息循环移位时各个基本交换单元的连接规律。基于该规律设计了

2009-11-09 14:21:56 17

17 本文以CCSDS 推荐的7/8 码率LDPC 码为例,提出了一种适于高码率LDPC 码译码器的硬件结构优化方法。高码率的LDPC 码通常也伴随着行重与列重的比例较高的问题。本方法是在拆分校验矩

2009-11-25 15:21:25 26

26 本文利用可编程逻辑的灵活性和Nios 的强大处理能力,将多种编译码模块和微处理器模块集成到一片FPGA 内部,方便地实现了通用编译码器的设计。由于采用了VHDL 语言,使系统具有可移

2009-11-30 14:27:56 22

22 基于TMS320C6416高性能通用DSP,实现了对AWGN信道的信噪比(SNR)估计,并以此估计值设计了一种低密度奇偶校验(LDPC)码的译码系统;详尽介绍了集成SNR估计的译码系统的实现方案和流程;仿真

2010-07-27 16:28:32 11

11 译码器

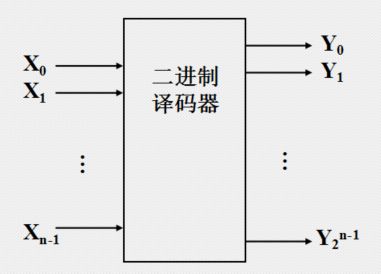

译码是编码的逆过程,即将某个二进制翻译成电路的某种状态。实现译码操作的电路称为译码器。

2008-09-27 12:59:06 12538

12538

数码译码器的应用:译码器课件ppt

2008-12-17 14:31:20 1056

1056

LDPC编译码LDPC码是一种线性分组奇偶校验码,它采用基于因子图的置信传播(Belief Propagation,BP)迭代译码算法进行译码。其性能接近Turbo码,不规则LDPC码甚至超过Tur

2009-03-01 17:36:05 1798

1798

第十七讲 译码器

6.4.1 二进制译码器一、二进制译码器 二、译码器CT74LS1381.逻辑图。2.真值表。3.逻辑功能:4.

2009-03-30 16:22:26 7525

7525

译码器,译码器是什么意思

译码器是组合逻辑电路的一个重要的器件,其可以分为:变量译码和显示译码两类。 变量译码一

2010-03-08 16:32:18 5304

5304 Turbo码虽然具有优异的译码性能,但是由于其译码复杂度高,译码延时大等问题,严重制约了Turbo码在高速通信系统中的应用。因此,如何设计一个简单有效的译码器是目前Turb

2010-11-25 10:10:26 1772

1772

本文描述了一种可用于CDMA 2000 通信系统的通用高速维特比译码器基于FPGA的设计与实现。该维特比译码器具有通用性和高速性, 它支持可变码率、可变帧长的译码。同时它采用四个ACS 并

2011-05-14 15:18:14 33

33 该文介绍了两种Viterbi 译码器回溯译码算法,通过对这两种算法硬件实现结构上的优化,给出了这两种算法的FPGA 实现方法,比较了两种实现方法的优缺点。最后将其应用在实际的Viter

2011-05-28 15:18:48 33

33 本文介绍了 RS[ 255, 223 ]编译码器的 FPGA设计和基于线形反馈移位寄存器的编码器设计 , 以及由伴随式计算、关键方程求解、钱氏搜索、Forney算法等功能模块组成的译码器。为了实现简单

2012-05-22 10:43:40 45

45 介绍了符合CCSDS标准的RS(255,223)码译码器的硬件实现结构。译码器采用8位并行时域译码算法,主要包括了修正后的无逆BM迭代译码算法,钱搜索算法和Forney算法。采用了三级流水线结构实现

2013-01-25 16:43:46 68

68 香农的学生Gallager首次提出了LDPC码的概念和完整的译码方法,目前LDPC码正向着高速高增益的方向发展。文中针对目前对高速LDPC码译码技术的迫切需求,以CCSDS标准近地通信(8176,7154)

2013-07-26 11:17:00 0

0 动态显示-译码器片选实现【汇编版】动态显示-译码器片选实现【汇编版】动态显示-译码器片选实现【汇编版】

2015-12-29 15:51:29 0

0 动态显示-译码器片选实现【C语言】动态显示-译码器片选实现【C语言】动态显示-译码器片选实现【C语言】动态显示-译码器片选实现【C语言】

2015-12-29 15:51:36 0

0 800Mbps准循环LDPC码编码器的FPGA实现

2016-05-09 10:59:26 37

37 截短Reed_Solomon码译码器的FPGA实现

2016-05-11 11:30:19 11

11 的低运算复杂度、低误码平台译码的改进算法。 该算法校验节点的运算采用修正最小和算法,外信息的更新采用串行方式,既保持了串行和积算法在有限迭代次数下译码门限低的优点,又降低了节点运算复杂度和误码平台。用定点DSP芯片实现的非规则LDPC码译码器的实测结果表明,该算法能以较低的实现复杂度获

2017-10-20 10:41:11 0

0 量化位数。然后基于该算法和这3个参数设计了一种全新的、高速部分并行的DSC译码器。该译码器最大限度地实现了译码效率、译码复杂度、FPGA资源利用率之间的平衡,并在Xilinx XC7VX485T芯片上实现了该译码器,其吞吐率可达197 Mb/s。

2017-11-16 12:59:01 2766

2766

该文通过对低密度校验(LDPC)码的编译码过程进行分析,提出了一种基于FPGA 的LDPC 码编译码器联合设计方法,该方法使编码器和译码器共用同一校验计算电路和复用相同的RAM 存储块,有效减少

2017-11-22 07:34:01 3928

3928

通过正确配置译码器的使能输入端,可以将译码器的位数进行扩展。例如,实验室现在只有3线- 8线译码器(如74138),要求我{ ]实现一个4线-16线的译码器。该如何设计呢?图1是其中的一种解决方案

2017-11-23 08:44:53 33058

33058

本文首先介绍了译码器的定义与译码器的分类,其次介绍了译码器的作用和译码器的工作原理,最后介绍了译码器的逻辑功能。

2018-02-08 14:04:06 107559

107559

本文主要介绍了译码器的分类和应用。译码器指的是具有译码功能的逻辑电路,译码是编码的逆过程,它能将二进制代码翻译成代表某一特定含义的信号(即电路的某种状态),以表示其原来的含义。译码器可以分为:变量

2018-04-04 11:51:12 37755

37755

的重视。基于准循环LDPC(QC-LDPC)码结构特点,提出了一种支持多种码率QC-LDPC 译码器的设计方法,并设计实现了一个能够实时自适应支持三个不同H 阵的通用QC-LDPC 译码器。

2019-01-08 09:22:00 2787

2787

可编程逻辑技术的不断发展,其高密度、低功耗、使用灵活、设计快速、成本低廉、现场可编程和反复可编程等特性,使FPGA逐步成为Viterbi译码器设计的最佳方法。项目目的是用FPGA实现一个Viterbi译码器。

2019-04-24 08:29:00 2635

2635

为块准循环结构,从而能够并行化处理译码算法的行与列操作。使用这个架构,我们在Xilinx Virtex-5 LX330 FPGA上实现了(8176,7154)有限几何LDPC码的译码器,在15次迭代的条件下其译码吞吐量达到800Mbps。

2021-01-22 15:08:39 9

9 针对一类规则(r,c)-LDPC(low-density parity check)码,提出了一种基于Turbo译码算法的高吞吐量存储器效率译码器。与传统的和积译码算法相比,Turbo译码算法对多个

2021-02-03 14:46:00 9

9 结构化LDPC码可进行相应扩展通过对编译码算法,优化编译码结构进行调整,降低了编译码嚣硬件实现中的关键路径迟延,并采用Xilinx公司的Virtex一4 VLX80 FPGA芯片实现了一个码长10 240,码率1/2的非正则结构化LDPC码编码器和译码器。实现结果表明:该编码器信息吞吐量为1.878 Gb/

2021-03-26 15:58:00 12

12 给出了跳频系统中 Turbo码译码器的FPGA( field programmable gate array)实现方案。译码器采用了MaxLog-map译码算法和模块化的设计方法,可以

2021-04-01 11:21:46 5

5 基于FPGA的800Mbps准循环LDPC码译码器

2021-06-08 10:31:31 26

26 关于Actel 的FPGA的译码器的VHDL源代码(通信电源技术期刊2020年第14期)-关于Actel 的FPGA的译码器的VHDL源代码。适合感兴趣的学习者学习,可以提高自己的能力,大家可以多交流哈

2021-09-16 15:18:01 10

10 一听到三八译码器这个东西可能会感觉有点熟悉,其实在STC89C51系列单片机中,里面就有一个三八译码器,就是一开始的流水灯程序,LED0-7这八个LED!但是怎么在FPGA中实现三八译码器呢?其实很简单。

2023-04-26 15:38:21 1787

1787

输入:二进制代码,有n个;

输出:2^n 个特定信息。

1.译码器电路结构

以2线— 4线译码器为例说明

2线— 4线译码器的真值表为:

2023-04-30 16:29:00 2335

2335

本次实验的任务是构建一个3-8译码器,且将译码结果通过小脚丫的LED灯显示。

2023-06-20 16:10:59 692

692

正在加载...

电子发烧友App

电子发烧友App

评论