特权同学为大家介绍市面上最常见的Xilinx spartan-3的xc3s400的配置电路...

2013-05-31 14:07:33 3814

3814

本文主要介绍Xilinx FPGA的配置模式。

2021-01-01 10:12:00 21578

21578

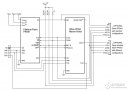

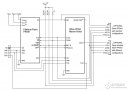

我们所说的FPGA配置电路,一方面要完成从PC上把bit文件下载到FPGA或存储器的任务,另一方面则要完成FPGA上电启动时加载配置数据的任务。

2023-06-10 10:09:52 317

317

锁相环基本上是每一个fpga工程必不可少的模块,之前文档xilinx 7 系列FPGA时钟资源对xilinx fpga的底层时钟资源做过说明,但是对于fpga的应用来说,使用Clocking Wizard IP时十分方便的。

2023-06-12 17:42:03 2883

2883

本帖最后由 lee_st 于 2017-10-31 08:58 编辑

FPGA技巧Xilinx,

2017-10-21 20:30:04

FPGA技巧Xilinx,,

2017-09-28 13:45:41

在电路板或TPS650860评估模块上对器件进行编程,以进行测试。TPS65086100具有多种示例配置,可快速适应某些最流行的FPGA和多处理器片上系统(MPSoC),如Xilinx Zynq

2018-07-24 17:27:53

引言: 我们在进行FPGA原理图和PCB设计时,都会涉及到FPGA芯片管脚定义和封装相关信息,本文就Xilinx 7系列FPGA给出相关参考,给FPGA硬件开发人员提供使用。通过本文,可以了解到

2021-05-28 09:23:25

:CCLK,重新生成download.bit,SelectMAP加载,FPGA工作正常!查Xilinx关于SelectMAP的说明(v4的配置手册ug71.pdf),发现一句话:The BitGen

2015-09-22 23:36:50

Xilinx FPGA配置的一些细节0 参考资料(1) Xilinx: Development System Reference Guide. dev.pdf, v10.1在Xilinx的doc目录

2015-08-20 22:57:10

Xilinx FPGA配置的一些细节0 参考资料(1) Xilinx: Development SystemReference Guide. dev.pdf, v10.1在Xilinx的doc目录

2016-05-22 23:38:23

Xilinx FPGA入门连载24:PLL实例之基本配置 1 工程移植可以复制上一个实例sp6ex7的整个工程文件夹,更名为sp6ex8。然后在ISE中打开这个新的工程。 2 新建IP核文件

2019-01-21 21:33:40

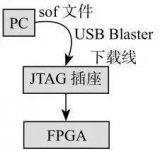

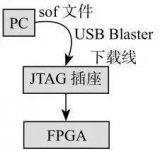

“Tools à iMPACT...”,启动专门用于FPGA下载配置的iMAPCT工具。第一次打开通常会弹出如下图所示的提示,点击“OK”继续。IMAPCT界面打开如下图所示。 2 初始化下载线缆连接

2015-10-22 12:35:16

`Xilinx FPGA入门连载44:FPGA片内ROM实例之ROM配置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 ROM初始化

2016-01-08 13:12:44

Xilinx FPGA配置clocking时钟动态相位输出

2019-08-05 11:35:39

-- PWM蜂鸣器驱动之引脚分配Lesson15 特权Xilinx FPGA SF-SP6入门指南 -- PWM蜂鸣器驱动之综合实现与配置文件产生Lesson16 特权Xilinx FPGA

2015-07-22 11:49:20

Xilinx FPGA入门连载44:FPGA片内ROM实例之ROM配置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 ROM初始化

2019-01-09 16:02:21

大家好,最近刚接触FPGA不久 现在手上有一块xilinx SP3E开发板,简单的设计了一个流水灯的程序 通过JTAG下载方式 直接下到FPGA里 板子可以运行 因为想实现断电后重启板子自动

2014-10-11 11:16:08

`Xilinx Artix-7 FPGA快速入门、技巧与实例连载6——FPGA开发流程更多资料共享链接:https://share.weiyun.com/53UnQas如图1.32所示,这是一个

2019-04-01 17:50:52

想通过SelectMAP方式配置Xilinx Virtex II。Selectmap的时序通过另外一个Altera FPGA控制,配置数据存放在SRAM中,Altera FPGA读出SRAM数据,每

2015-07-16 16:30:47

Xilinx公司的XC5VFX100T型号的FPGA用什么芯片配置,我发现Xilinx公司自己的XCF32P好像存储空间不满足,是否有其他芯片,或者就是XCF32P?

2020-01-15 14:16:09

Xilinx_FPGA下载烧写教程(超详细)Step by step 学习下载配置 Xilinx 之 FPGA配合 Mars-EDA 的 Spartan2 核心板,用图文方式向大家详细讲述如何下载配置 Xilinx的 FPGA。

2017-10-31 12:16:03

BPI模式下配置的,我使用的是同步BPI模式。使用快速启动支持BPI SYNC模式?谢谢以上来自于谷歌翻译以下为原文HiI am design withe Kintex 7 FPGA

2019-04-08 14:00:12

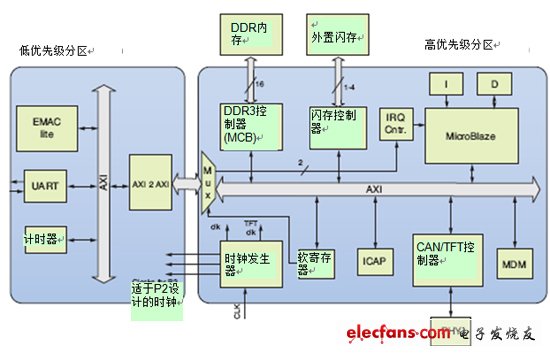

`简介:在《FPGA上的嵌入式系统设计实例(附光盘XILINX大学合作计划指定教材)》的写作过程中,弱化基本概念,强调实验和项目设计,并且突出版本管理的作用。前3章是基本概念的介绍;第4章

2017-12-08 14:30:50

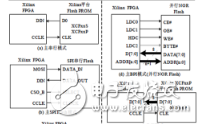

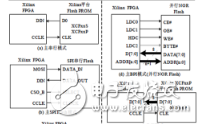

这里要谈的是Xilinx的spartan-3系列FPGA的配置电路。当然了,其它系列的FPGA配置电路都是大同小异的,读者可以类推,重点参考官方提供的datasheet,毕竟那才是最权威的资料。

2019-10-10 06:16:52

取代连接转换器的传统并行LVDS/CMOS接口,并用来实现 JESD204B物理层。本文介绍如何快速在Xilinx® FPGA上实现JESD204B接口,并为FPGA设计人员提供部分应用和调试建议

2018-10-16 06:02:44

我使用外部配置emcclk时钟和闪存PC28F00AP30EFA在BPI-Fast模式下配置了Kintex7 FPGA。我遵循Xilinx AR#44636并定义了Config_Voltage

2020-06-04 12:45:32

嗨,我一直在看这个问题:http://forums.xilinx.com/t5/Xilinx-Boards-and-Kits/spartan6-fpga

2019-08-01 08:17:03

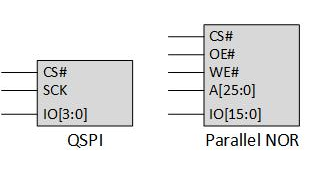

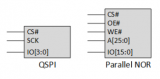

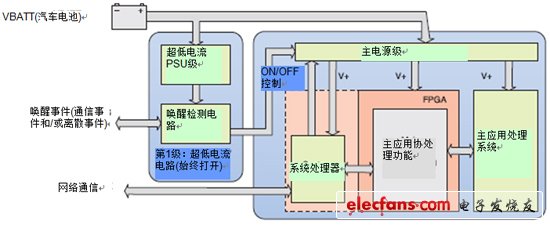

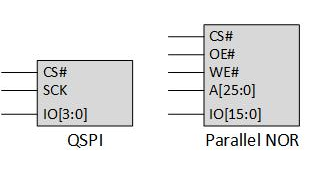

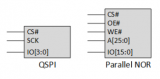

NOR闪存已作为FPGA(现场可编程门列阵)的配置器件被广泛部署。其为FPGA带来的低延迟和高数据吞吐量特性使得FPGA在工业、通信和汽车ADAS(高级驾驶辅助系统)等应用中得到广泛采用。汽车场景中

2019-10-09 08:26:02

我们如何在xilinx FPGA中执行运行时重新配置?

2020-07-16 10:24:37

Xilinx FPGA的配置方式何用PowerPC860实现FPGA配置

2021-04-08 06:46:46

Xilinx的FPGA、SoC、MPSoC、RFSoC和ACAP产品介绍使用Xilinx的FPGA、SoC和ACAP进行设计和开发

2021-01-22 06:38:47

嗨,大家好,我希望使用S70FS01GS或Flash作为Xilinx UllasCal+ FPGA的配置存储器。S70的范围是由FPGA /影响编程工具支持的吗?提前感谢。 以上来自于百度翻译

2019-07-02 11:13:12

Flash来存储我的FPGA配置数据。XAPP058中描述的方法是否可以用于故障安全升级,因为XCF32P只允许XC6SLX100的一个配置文件空间?有没有什么方法可以使用SPI闪存启动选项实现FPGA

2019-05-30 10:05:15

本帖最后由 jfzhangjin 于 2015-1-8 10:48 编辑

之前也一直在做关于Xilinx FPGA各个方面的文章,但是总体而言就显得有些杂,总希望能有人能整理一下便于查阅;另外

2014-11-03 17:15:51

嗨,能否建议我用Xilinx FPGA直接替代智能融合FPGA。目前我的参考设计客户端正在使用智能融合(A2F200M3F-1FGG256I)FPGA。我想用Xilinx FPGA代替。在配置期间,FPGA引脚不应处于浮空状态,FPGA引脚应处于已知状态。这是我项目的严格要求。谢谢,C.一个雷迪。

2020-05-13 08:22:47

NOR闪存已作为FPGA(现场可编程门列阵)的配置器件被广泛部署。其为FPGA带来的低延迟和高数据吞吐量特性使得FPGA在工业、通信和汽车ADAS(高级驾驶辅助系统)等应用中得到广泛采用。汽车场景中

2019-08-02 08:40:33

介绍如何用PowerPC860(MPC860)进行FPGA(Xilinx 的Virtex-II 系列)的配置;给出进行FPGA 配置所需的详细时序图和原理图。本配置基本原理对其它FPGA 的配置也适用。

2009-04-16 14:11:36 18

18 简化Xilinx和Altera FPGA调试过程:通过FPGAViewTM 解决方案,如混合信号示波器(MSO)和逻辑分析仪,您可以在Xilinx 和Altera FPGA 内部迅速移动探点,而无需重新编译设计方案。能够把内部FPGA

2009-11-20 17:46:26 26

26 十分钟学会Xilinx FPGA 设计

Xilinx FPGA设计基础系统地介绍了Xilinx公司FPGA的结构特点和相关开发软件的使用方法,详细描述了VHDL语言的语法和设计方法,并深入讨

2010-03-15 15:09:08 177

177 器件定义

软件工具概述

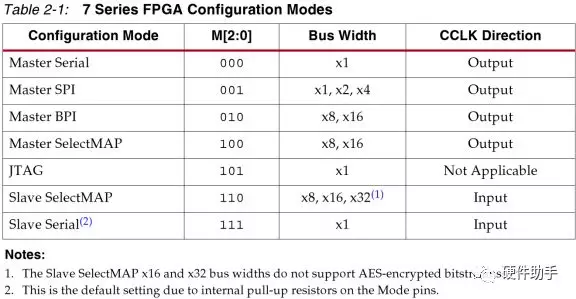

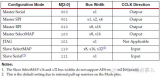

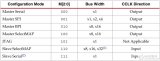

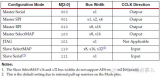

选择配置模式

编程/配置选项

XILINX的通用配置/编程的装置

2010-06-22 16:24:01 78

78 摘要:介绍如何用PowerPC860(MPC860)进行FPGA(Xilinx的Virtex-II系列)的配置;给出进行FPGA配置所需的详细时序图和原理图。本配置基本原理对其它FPGA的配置也适用。

2009-06-20 11:02:38 942

942

安富利推出Xilinx Virtex-6 FPGA DSP开发工具套件安富利公司旗下运营机构安富利电子元件宣布推出Xilinx Virtex -6 FPGA DSP开发工具套件。这套件是为DSP设计而打造,是Xilinx目标设计平

2010-04-24 09:56:31 1331

1331 一、配置Modelsim ISE的Xilinx的仿真库 1、编译仿真库: A、先将Modelsim安装目录C=Modeltech_6.2b下面的modelsim.ini改成存档格式(取消只读模式); B、在DOS环境中,进入Xilinx的根目录,然后依次进入

2011-03-30 10:19:07 307

307 用不同的方法配置Xilinx 的FPGA 和编程CPLD 以及PROM,有助于满足系统设计人员的不同需要。本文档描述了不同的配置模式以帮助设计人员选择适当的配置或编程方法,并提供了用于生产或

2011-11-01 14:40:45 39

39 本文着重介绍了 Xilinx Platform Flash PROM 如何帮助系统和电路板设计人员简化 FPGA 配置设计。用于配置 FPGA 的可选解决方案有很多,但它们通常都需要大量的前期设计工作和时间。Platform

2012-01-17 17:33:20 36

36 一些应用利用 Xilinx FPGA 在每次启动时可改变配置的能力,根据所需来改变 FPGA 的功能。Xilinx Platform Flash XCFxxP PROM 的设计修订 (Design Revisioning) 功能,允许用户在单个PROM 中将多种配置存

2012-01-17 17:40:34 43

43 WP374 Xilinx FPGA的部分重配置

2012-03-07 14:34:39 34

34 通过Xilinx Spartan-6 FPGA 的Multiboot特性,允许用户一次将多个配置文件下载入Flash中,根据不同时刻的需求,在不掉电重启的情况下,从中选择一个来重配置FPGA,实现不同功能,提高器件利用率,增加

2012-03-22 17:18:56 65

65 本书系统地论述了Xilinx FPGA开发方法、开发工具、实际案例及开发技巧,内容涵盖Xilinx器件概述、Verilog HDL开发基础与进阶、Xilinx FPGA电路原理与系统设计

2012-07-31 16:20:42 11268

11268

本文是关于 xilinx公司的7系列FPGA应用指南。xilinx公司的7系列FPGA包括3个子系列,Artix-7、 Kintex-7和Virtex-7。本资料就是对这3各系列芯片的介绍。 下表是xilinx公司的7系列FPGA芯片容量对比表

2012-08-07 17:22:55 201

201 本文着重介绍了 Xilinx Platform Flash PROM 如何帮助系统和电路板设计人员简化 FPGA 配置设计。用于配置 FPGA 的可选解决方案有很多,但它们通常都需要大量的前期设计工作和时间。Platform

2013-03-14 15:18:22 64

64 Xilinx FPGA设计进阶(提高篇)

有需要的下来看看

2015-12-29 15:45:48 12

12 在Xilinx FPGA上快速实现 JESD204B

2016-01-04 18:03:06 0

0 Xilinx FPGA系列入门教程(二)——Xilinx FPAG开发环境的配置

2016-01-18 15:30:20 32

32 Xilinx FPGA系列入门教程(一)——如何搭建Xilinx FPGA开发环境

2016-01-18 15:30:32 45

45 Xilinx FPGA工程例子源码:Xilinx 的IP:1024点FFT快速傅立叶变换

2016-06-07 15:07:45 51

51 Xilinx FPGA工程例子源码:基于XILINX的XC3系列FPGA的VGA控制器的VHDL源程序

2016-06-07 15:07:45 12

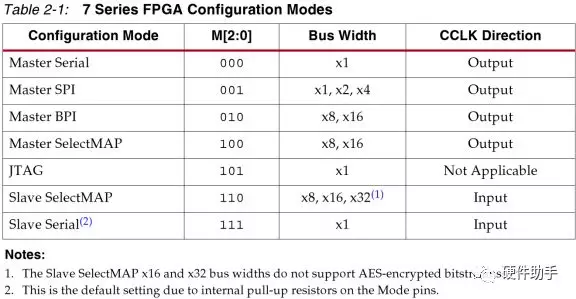

12 的PCIe设备,需要reboot服务器。众所周知,FPGA芯片规模越来越大,那么如何做才能满足PCIe设备的启动时间的要求呢? 7系列FPGA常见的配置模式如下图所示: SelectMAP和Master

2017-02-07 20:55:41 2914

2914

这篇blog想弄清楚FPGA上电配置后程序引导和启动的整个流程是怎么样的,不是谈论如何编写bootloader。

2017-02-11 05:55:06 1985

1985 文档内容包含基于Xilinx FPGA的开发板代码及原路图,供网友参考。

2017-09-01 11:09:24 20

20 FPGAs have changed dramatically since Xilinx first introduced them just 15 years ago. In the ast

2017-09-20 18:41:55 14

14 Xilinx FPGA的Maxim参考设计

2017-10-31 09:59:24 23

23 通过SELECTMAP32接口配置和回读XILINX公司生产的V5系列SRAM型FPGA,被配置的FPGA以下简称DUT,产生配置时序的FPGA简称配置FPGA。首先硬件上应将M[2:0]接成110

2017-11-17 10:16:01 8730

8730 随着FPGA的广泛应用, 其实现的功能也越来越多, FPGA 的动态重构设计就显得愈发重要。在分析Xilinx Vertex II Pro系列FPGA配置流程、时序要求的基础上, 设计了基于CPLD

2017-11-22 07:55:01 937

937

本节旨在通过给定的工程实例“按键开关控制LED”来熟悉Xilinx ISE软件的基本操作、设计、编译及仿真流程。同时使用基于Xilinx FPGA的开发板将该实例进行下载、验证及调试,完成工程设计的硬件实现,熟悉Xilinx FPGA开发板的使用及配置方式。

2017-11-22 15:31:49 6203

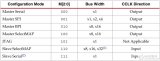

6203 FPGA配置方式灵活多样,根据芯片是否能够自己主动加载配置数据分为主模式、从模式以及JTAG模式。典型的主模式都是加载片外非易失( 断电不丢数据) 性存储器中的配置比特流,配置所需的时钟信号( 称为

2017-11-26 08:12:51 7889

7889

JESD204B协议是目前高速AD,DA通用的协议。对于基带使用FPGA用户来说,Xilinx品牌的FPGA使用更为常见。Xilinx提供了JESD204的IP core,设计起来比较方便。

2018-07-04 10:12:00 3977

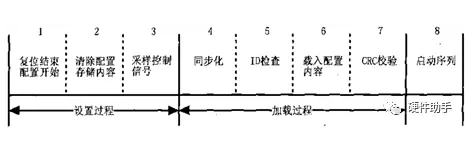

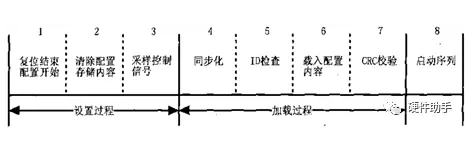

3977 尽管FPGA的配置模式各不相同,但整个配置过程中FPGA的工作流程是一致的,分为三个部分:设置、加载、启动。

2018-08-01 15:32:54 4736

4736

FPGA本身是有专门的时钟cell的,以xilinx FPGA为例,就是primitive库中的BUFG。

2018-12-22 15:33:59 1588

1588 Xilinx FPGA是支持OpenStack的第一个(也是目前唯一的)FPGA。

该视频快速介绍了如何在小型集群中部署Xilinx FPGA卡,以便在Xilinx SC16展台上运行每个演示,并使用OpenStack进行配置和管理。

2018-11-23 06:14:00 3322

3322 从19到32Gb / s的互连宽度正在迅速扩大。

了解Xilinx UltraScale +™FPGA和MPSoC如何直接使用这些互连,以及KCU116和VCU118评估套件如何快速启动您的设计。

2018-11-22 07:21:00 2875

2875 NOR闪存已作为FPGA(现场可编程门列阵)的配置器件被广泛部署。其为FPGA带来的低延迟和高数据吞吐量特性使得FPGA在工业、通信和汽车ADAS(高级驾驶辅助系统)等应用中得到广泛采用。汽车

2019-02-21 17:01:30 4488

4488

NOR闪存已作为FPGA(现场可编程门列阵)的配置器件被广泛部署。其为FPGA带来的低延迟和高数据吞吐量特性使得FPGA在工业、通信和汽车ADAS(高级驾驶辅助系统)等应用中得到广泛采用。汽车

2019-02-23 10:43:59 3020

3020

今天咱们聊聊xilinx7系列FPGA配置的相关内容。总所周知FPGA上电后,其工作的逻辑代码需要从外部写入FPGA,FPGA掉电后其逻辑代码就丢失,因此FPGA可以被无限次的配置不同的逻辑代码

2019-10-20 09:02:00 2769

2769

本文主要介绍Xilinx FPGA的FMC接口。

2020-01-28 17:52:00 5120

5120 Xilinx 7系列FPGA概览 文章目录 Xilinx 7系列FPGA概览 1.Xilinx的四个工艺级别 2.Virtex、Kintex、Artix和Spartan 3.7系列特点 4.7系列

2020-11-13 18:03:30 14065

14065 SRL(移位寄存器)资源,在FPGA中都有,不过是叫不同的名字。Xilinx FPGA内部的LUT有个特殊功能,就是可以配置成可变长度SRL。

2020-12-31 16:45:35 8

8 AD5933 pmod Xilinx FPGA参考设计

2021-04-21 18:41:19 3

3 AD7780 pmod Xilinx FPGA参考设计

2021-04-22 13:35:23 11

11 ADXL362 pmod Xilinx FPGA参考设计

2021-05-11 10:44:18 9

9 ADXL345 pmod Xilinx FPGA参考设计

2021-05-16 19:45:16 8

8 AD5628 pmod Xilinx FPGA参考设计

2021-05-19 14:34:17 4

4 AD5541A pmod Xilinx FPGA参考设计

2021-05-19 15:15:19 11

11 AD7193 pmod Xilinx FPGA参考设计

2021-05-19 15:18:13 2

2 AD7091R pmod Xilinx FPGA参考设计

2021-05-19 18:31:59 7

7 AD7156 pmod Xilinx FPGA参考设计

2021-05-20 12:32:16 10

10 AD7991 pmod Xilinx FPGA参考设计

2021-05-20 12:37:26 12

12 AD5781 pmod Xilinx FPGA参考设计

2021-05-24 10:29:20 17

17 Xilinx FPGA开发实用教程资料包免费下载。

2022-04-18 09:43:46 24

24 尽管FPGA的配置模式各不相同,但整个配置过程中FPGA的工作流程是一致的,分为三个部分:设置、加载、启动。

2022-10-10 14:37:57 1272

1272 在无 JTAG 的模式下,Zynq 是通过片上CPU完成对芯片的配置,也就是PS和PL的配置是通过 PS 处理器 ARM 核来实现的。需要注意的是,与传统的 Xilinx 7 系列 FPGA 芯片不同,Zynq 是不支持从 PL 端进行直接启动配置的,一定要通过 PS 部分来完成。

2022-10-19 09:11:55 986

986 总结Xilinx FPGA 的上电模式可以分为以下4类型: 主模式 从模式 JTAG模式(调试模式) 系统模式(多片配置模式) 1、主模式 典型的主模式都是加载片外非易失( 断电不丢数据

2023-03-29 14:50:06 535

535 Xilinx FPGA pcb设计

2023-05-29 09:11:36 0

0 )等应用中得到广泛采用。汽车场景中摄像头系统的快速启动时间要求就是很好的一个例子——车辆启动后后视图像在仪表板显示屏上的显示速度是最为突出的设计挑战。 上电后,FPGA立即加载存储于NOR器件中的配置比特流。传输完成后,FPGA转换为活动(已配置)状态。FP

2023-08-15 13:55:02 331

331

罗彻斯特电子携手AMD/Xilinx,为Xilinx传统FPGA和相关配置PROM产品提供供货支持。

2023-11-07 09:04:42 250

250 电子发烧友网站提供《适用于 Xilinx® MPSoC 和 FPGA 的可配置多轨PMU TPS650864数据表.pdf》资料免费下载

2024-03-06 17:07:17 0

0 Xilinx FPGA芯片拥有多个系列和型号,以满足不同应用领域的需求。以下是一些主要的Xilinx FPGA芯片系列及其特点。

2024-03-14 16:24:41 215

215

正在加载...

电子发烧友App

电子发烧友App

评论