在FPGA 上设计一个高性能、灵活的、面积小的通信体系结构是一项巨大的挑战。大多数基于FPGA 的片上网络都是运行在一个单一时钟下。随着FPGA 技术的发展,Xilinx 公司推出了Virtex-4 平台

2011-10-21 16:13:51 1270

1270

01、如何决定FPGA中需要什么样的时钟速率 设计中最快的时钟将确定 FPGA 必须能处理的时钟速率。最快时钟速率由设计中两个触发器之间一个信号的传输时间 P 来决定,如果 P 大于时钟周期

2020-11-23 13:08:24 3565

3565

一般的FPGA的数据传输接送接口不都是用USB的么,我想用蓝牙无线的接口,想买响应的蓝牙模块,有没有能和Spartan-3 FPGA 系列 相匹配的蓝牙模块呢?

2019-08-14 16:33:55

一般的FPGA的数据传输接送接口不都是用USB的么,我想用蓝牙无线的接口,想买响应的蓝牙模块,有没有能和Spartan-6 FPGA 系列 相匹配的蓝牙模块呢?

2019-08-13 17:03:34

即可。

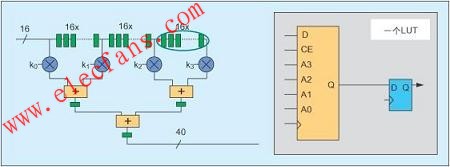

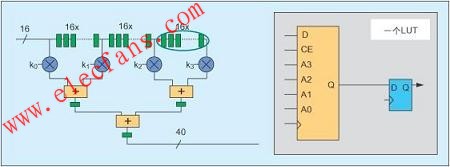

下面是一个4输入与门的例子。

二、基于查找表(LUT)的FPGA的结构

我们看一看Xilinx Spartan-II的内部结构,如下图:

Spartan-II主要包括CLBs

2023-11-03 11:18:38

FPGA 实现大型设计时,可能需要FPGA 具有以多个时钟运行的多重数据通路,这种多时钟FPGA 设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数据关系。设计过程中

2012-10-26 17:26:43

本帖最后由 lee_st 于 2017-10-31 08:58 编辑

FPGA多时钟设计

2017-10-21 20:28:45

跨时钟域处理是FPGA设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个FPGA初学者的必修课。如果是还在校生,跨时钟域处理也是面试中经常常被问到的一个问题。这里主要介绍三种跨时钟域

2021-03-04 09:22:51

利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数据关系。设计过程中最重要的一步是确定要用多少个不同的时钟,以及如何进行布线?

2019-08-30 08:31:41

(LUT)的FPGA的结构我们看一看xilinx Spartan-II的内部结构,如下图: xilinx Spartan-II 芯片内部结构Slices结构Spartan-II主要包括CLBs,I

2012-04-28 14:57:28

FPGA的多时钟系统设计 Multiple Clock System Design Clk1and Clk2are the clock which running at different frequency[/hide]

2009-12-17 15:46:09

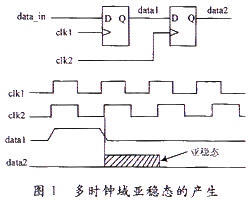

FPGA设计中有多个时钟域时如何处理?跨时钟域的基本设计方法是:(1)对于单个信号,使用双D触发器在不同时钟域间同步。来源于时钟域1的信号对于时钟域2来说是一个异步信号。异步信号进入时钟域2后,首先

2012-02-24 15:47:57

[size=11.818181991577148px]FPGA开发中,遇到的最多的就是异步时钟域了。[size=11.818181991577148px]检查初学者的代码,发现最多的就是这类

2014-08-13 15:36:55

(10)FPGA跨时钟域处理1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA跨时钟域处理5)结语1.2 FPGA简介FPGA(Field Programmable

2022-02-23 07:47:50

的Spartan-3A的Spartan-3ESpartan-3系列的Spartan-IIE的Spartan-II谢谢&问候。以上来自于谷歌翻译以下为原文Sir/ Madam, In our

2019-05-08 14:52:17

Spartan-II 应用指南XAPP058 -利用嵌入式微控制器进行Xilinx在系统(In-System)编程Xilinx 高性能CPLD、FPGA和可配置的PROM系列提供了在系统

2021-08-12 07:39:42

本帖最后由 lpc2292 于 2013-2-27 20:24 编辑

“部分 I: 用 Spartan-3 系列 FPGA 进行设计”第 1 章 “概述”第 2 章 “使用全局时钟资源”第 3

2013-02-27 20:20:10

00000000000001000010....0...01111111111 二.基于查找表(LUT)的FPGA的结构 我们看一看xilinx Spartan-II的内部结构,如下图:xilinx

2008-05-20 09:46:10

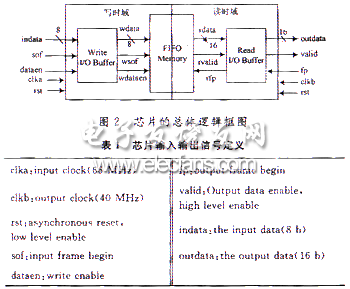

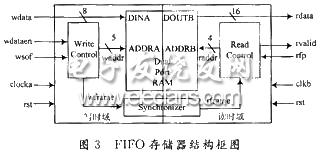

采用FPGA来设计一款广泛应用于计算机、Modem、数据终端以及许多其他数字设备之间的数据传输的专用异步并行通信接口芯片,实现了某一时钟域(如66 MHz)的8位并行数据到另一低时钟域(如40 MHz)16

2011-09-07 09:16:40

出现问题,来自快时钟域的控制信号必须宽于较慢时钟的周期。否则如下图所示,快时钟域的控制信号无法被采样到慢时钟域。3、在时钟域之间同步数据的两种常用方法将数据从一个时钟域传递到另一个时钟域类似于传递多个

2022-04-11 17:06:57

HDL与VHDL的比较附录C Virtex-II 和Spartan-II E的管脚####################################booklab1-resource包括附录D

2013-06-02 10:13:17

组来定义策略。在多个时钟域之间传递控制信号时,尝试使用同步器的策略。尝试使用FIFO和缓存的数据路径同步器来提高数据完整性。现在讨论重要的跨时钟处理问题与策略及其在多时钟域设计中的使用。多时钟域设计有

2022-06-24 16:54:26

大家好:最近在做基于FPGA 的以太网数据通信,现在遇到的问题是利用nios i和以太网芯片通信已经实现,但是niosII 读取的以太网传递的数据怎么传递到FPGA 顶层模块,用硬件逻辑设计语言实现进一步处理,请大家指点,小弟不胜感激!

2016-07-13 15:59:26

双口RAM如何实现跨时钟域通信啊?怎么在quartus ii仿真???

2017-05-02 21:51:39

利用 FPGA 实现大型设计时,可能需要FPGA 具有以多个时钟运行的多重数据通路,这种多时钟 FPGA 设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数据关系

2012-03-05 14:42:09

跨越时钟域FPGA设计中可以使用多个时钟。每个时钟形成一个FPGA内部时钟域“,如果需要在另一个时钟域的时钟域产生一个信号,需要特别小心。隧道四部分第1部分:过路处。第2部分:道口标志第3部分:穿越

2012-03-19 15:16:20

跨时钟域处理是FPGA设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个FPGA初学者的必修课。如果是还在校生,跨时钟域处理也是面试中经常常被问到的一个问题。这里主要介绍三种跨时钟域

2021-02-21 07:00:00

跨时钟域处理是FPGA设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个FPGA初学者的必修课。如果是还在校生,跨时钟域处理也是面试中经常常被问到的一个问题。 这里主要介绍三种跨

2021-01-08 16:55:23

嗨,在阅读了大量文件和无数次尝试之后,我不得不向你寻求指导。我有一个安装了Spartan XCS1400A FPGA的ZESTET1以太网板。该板具有1 Gbps以太网接口和TCP-IP卸载引擎。我

2019-06-12 13:30:44

。像Spartan 6 XC6SLX9FPGA这样的低端FPGA是否足以实现这种数据速度?我应该使用哪个记忆时间? 如果不是,任何想法?非常感谢您的关注。

2020-03-26 09:31:54

labview生成安装程序(里面数据传递用共享变量) 在本电脑上可以传递数据,安装到其他电脑上无法传递数据,何解?

2016-07-08 13:57:24

关于异步时钟域的理解的问题: 这里面的count[25]、和count[14]和count[1]算是多时钟域吧?大侠帮解决下我的心结呀,我这样的理解对吗?

2012-02-27 15:50:12

你好,我在Viv 2016.4上使用AC701板。我需要同步从一个时钟域到另一个时钟域的多位信号(33位)。对我来说,这个多位信号的3阶段流水线应该足够了。如果将所有触发器放在同一个相同的切片

2020-08-17 07:48:54

平台。该平台支持同一时间内32 个时钟运行,也就是说每个片上网络的内核可以在一个独立的时钟下运行, 从而使每个路由器和IP 核都运行在最佳频率上。因此适用于设计多时钟片上网络,实现高性能分组交换片上网络。

2019-08-21 06:47:43

AD接口:时钟对齐、根据帧同步实现串转并数据对齐.本人非常熟悉Virtex-5/Virtex-6/7 Series FPGA的内置SERDES模块,包括ISERDES,OSERDES,IODELAY

2014-03-01 18:47:47

本帖最后由 mingzhezhang 于 2012-5-23 20:05 编辑

大型设计中FPGA的多时钟设计策略 利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据

2012-05-23 19:59:34

利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数据关系。设计过程中

2015-05-22 17:19:26

嗨, 我正在使用Saturn Spartan6 numato板。我在董事会中实现了一个非常简单的要求版本。现在我想将数据传输到FPGA或从FPGA传输到PC。请提出一些建议。谢谢。

2019-07-31 10:36:37

时钟域转换中亚稳态是怎样产生的?多时钟域数据传递的FPGA实现

2021-04-30 06:06:32

:int main (void){各种初始化while(1){ 触摸屏 LCD刷新 串口通信 } }就像这个小例子,触摸屏按键的操作和串口的数据要显示在LCD上。换做u/cos II的话,就是建立3个任务,然后之间再有一些数据传递就可以了?

2019-04-04 06:36:23

跨时钟域处理是 FPGA 设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个 FPGA 初学者的必修课。如果是还在校生,跨时钟域处理也是面试中经常常被问到的一个问题。这里主要介绍三种跨

2020-09-22 10:24:55

跨时钟域处理是FPGA设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个FPGA初学者的必修课。如果是还是在校的学生,跨时钟域处理也是面试中经常常被问到的一个问题。在本篇文章中,主要

2021-07-29 06:19:11

跨时钟域处理是什么意思?如何处理好跨时钟域间的数据呢?有哪几种跨时钟域处理的方法呢?

2021-11-01 07:44:59

我无法访问WebCase网站。如何获得HW-USB-II-G平台USB II和XC3S250E-4PQG208C Spartan FPGA的波动性声明?谢谢。以上来自于谷歌翻译以下为原文I am

2019-04-28 13:29:42

对多时钟系统的同步问题进行了讨论å提出了亚稳态的概念及其产生机理和危害;叙述了控制信号和数据通路在多时钟域之间的传递õ讨论了控制信号的输出次序对同步技术的不同要求,重点论述了常用的数据通路同步技术----用FIFO实现同步的原理及其实现思路

2012-05-23 19:54:32

亲爱的朋友们, 我有一个多锁设计。时钟为50MHz,200MHz和400Mhz。如果仅使用400MHz时钟并使用时钟使能产生200Mhz和50Mhz时钟域。现在我需要将信号从一个时钟域传递到另一个

2019-03-11 08:55:24

跨时钟域处理是 FPGA 设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个 FPGA 初学者的必修课。如果是还在校生,跨时钟域处理也是面试中经常常被问到的一个问题。这里主要介绍三种跨

2020-10-20 09:27:37

大型设计中FPGA的多时钟设计策略利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟

2020-04-26 07:00:00

实现数据传递需要做些什么?需要用到什么?怎么才能让数据传递到另一端?服务端客户端

2022-03-02 07:15:44

。虽然这样可以简化时序分析以及减少很多与多时钟域有关的问题,但是由于FPGA外各种系统限制,只使用一个时钟常常又不现实。FPGA时常需要在两个不同时钟频率系统之间交换数据,在系统之间通过多I/O接口接收

2022-10-14 15:43:00

FPGA采用spartan 6 系列,现有个技术问题需要咨询:FPGA采集10路串行同步信号,每路一根数据线一对差分时钟线,时钟最快可达40MHz,那么这10对时钟线能否接到FPGA的普通IO上面

2017-12-08 14:52:58

嗨,我是FPGA的新手(也是Xilinx系列FPGA的新手),所以我想知道Xilinx Spartan-II(XC2S100)FPGA板中是否有内置/预编程的Verilog模块或变量。这是因为我正在

2019-06-04 12:36:34

:LX:XC4VLX15,XC4VLX25,XC4VSX25,XC4VFX12Spartan™系列Spartan-II:所有Spartan-IIE:所有Spartan

2020-06-05 09:23:59

你好,我有一个用于VHART开发的SPARTAN II的旧FPGA设计。有没有办法使用当前的设计工具为SPARTAN II开发代码?谢谢tower_dig.vhd 30 KB以上来自于谷歌翻译以下

2019-06-17 09:23:59

`各位高手,请教下如何用队列实现vi之间的数据传递,最好能给出个例子,我是初学者,谢谢`

2017-09-08 11:01:12

减少很多与多时钟域有关的问题,但是由于FPGA外各种系统限制,只使用一个时钟常常又不现实。FPGA时常需要在两个不同时钟频率系统之间交换数据,在系统之间通过多I/O接口接收和发送数据,处理异步信号

2023-06-02 14:26:23

Multiple Clock System Design PLD设计技巧—多时钟系统设计

Information Missing

Max+Plus II does

2008-09-11 09:19:41 25

25 单片机教程九:单片机数据传递类指令

单片机数据传递类指令

(3)以直接地址为目的操作数的指令

MOV direct,A 例: MOV 20H,A

2009-05-15 23:03:11 790

790

大型设计中FPGA的多时钟设计策略

利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率

2009-12-27 13:28:04 645

645

赛灵思Spartan FPGA高清视频参考设计,轻松实现“即插即用”

赛灵思公司(Xilinx)近日推出一款全新的消费视频增强参考设计。该款参考设计基于一个低成本的Xilinx Sparta

2010-01-29 08:51:22 719

719 Spartan-3FPGA能以突破性的价位点实现嵌入式DSP功能。本文阐述了Spartan-3 FPGA针

2010-12-17 11:31:23 675

675

: Spartan-3E (50万门,XC3S500E-4FG320C), CoolRunner-II (XC2C64A-5VQ44C)与Platform Flash (XCF04S-VO20C) 时钟:

2011-01-18 16:23:32 110

110 为利用简单的线缆收发器,实现中等数据率的串行数据传输,提出了一种基于电荷泵式PLL的时钟数据恢复的方法。鉴相器由FPGA实现,用固定延时单元构成一条等间隔的延时链,将输入信号经过每级延时单元后的多个输出用本地的VCO时钟锁存,输入信号的沿变在延时链

2011-03-15 12:39:34 90

90 通过Xilinx Spartan-6 FPGA 的Multiboot特性,允许用户一次将多个配置文件下载入Flash中,根据不同时刻的需求,在不掉电重启的情况下,从中选择一个来重配置FPGA,实现不同功能,提高器件利用率,增加

2012-03-22 17:18:56 65

65 利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数

2012-05-21 11:26:10 1100

1100

NBP16 Xilinx Spartan-II PQ208 Rev1.01

2016-02-17 15:04:39 0

0 Memec Spartan II Demo Board Rev3,好东西,喜欢的朋友可以下载来学习。

2016-02-22 15:54:52 0

0 Spartan 3系列的FPGA原理图,144针引脚

2016-06-03 16:16:53 13

13 时钟设施提供了一系列的低电容、低抖动的互联线,这些互联线非常适合于传输高频信号、最大量减小时钟抖动。这些连线资源可以和DCM、PLL等实现连接。 每一种Spartan-6芯片提供16个高速、低抖动的全局时钟资源用于优化性能。

2018-07-14 07:07:00 6504

6504

Spartan-6 FPGA Data Sheet

2017-10-24 08:39:19 21

21 PicoBlaze是8位微处理器,在Xilinx公司的Virtex、Spartan-II系列以上FPGA与CoolRunner-II系列以上的CPLD器件设计中以IP核的方式提供,使用是免费的 。常见的版本有KCPSM3和KCPSM6。其中KCPSM支持7系列的Xilinx FPGA。

2017-11-17 20:28:01 3437

3437

本演示介绍了 Spartan®-3A 入门套件如何让您立即获得 Spartan-3A FPGA 器件的节能模式,高速 I/O 选项,DDR2 SDRAM 存储器接口,商用闪存配置支持,以及利用 Device DNA 实现的 FPGA/IP 保护等特性。

2018-05-22 13:45:01 2484

2484 了解如何描述Spartan-6 FPGA中的全局和I / O时钟网络,描述时钟缓冲器及其与I / O资源的关系,描述Spartan-6 FPGA中的DCM功能。

2018-11-22 06:10:00 4862

4862 本文档的主要内容详细介绍的是spartan-6 FPGA的时钟资源的用户指南资料免费下载。

2019-02-15 16:39:07 27

27 Spartan-3an FPGA系列将领先、低成本的FPGA的最佳特性与广泛密度范围内的非易失性技术相结合。该系列结合了Spartan-3A FPGA系列的所有功能,以及系统闪存中的领先技术,用于配置和非易失性数据存储。

2019-05-27 08:00:00 1

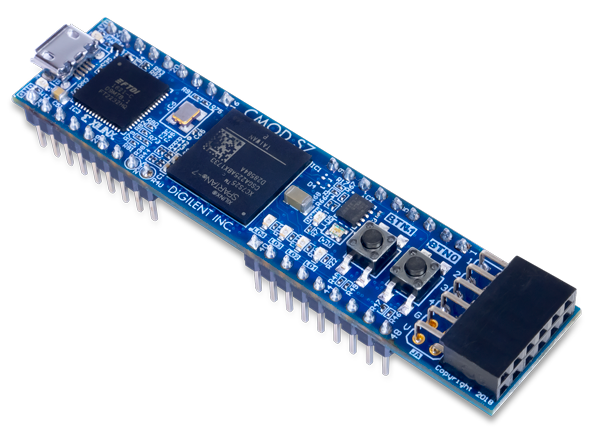

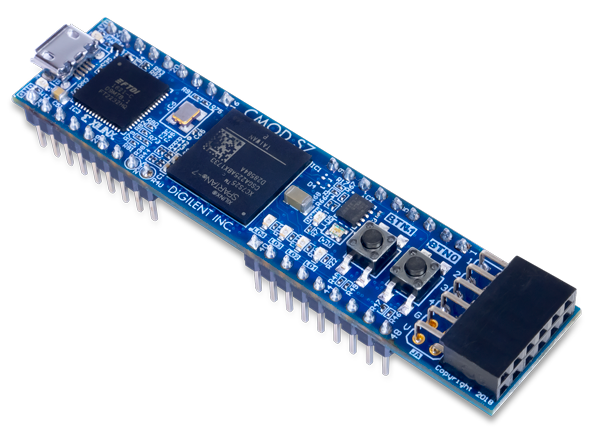

1 ,一个外部电源输入和接地线路连接到100毫英寸间距内,使Cmod S7非常适合与面包板一起使用。它只有0.7英寸×3.05英寸,可以方便的开发嵌入式系统。该板还包括编程ROM,时钟源,USB编程和数据传输电路,电源,LED和按钮。

2019-11-14 15:55:53 2734

2734

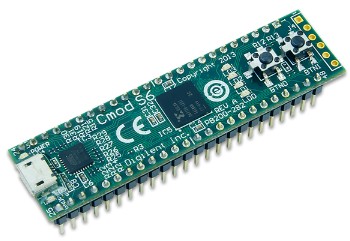

DigilentCmod S6是一款基于Xilinx® Spartan®-6 LX4 FPGA芯片的小型的,48引脚DIP外形因素板。此板包括一个编程ROM,时钟源,USB编程与数据传输电路,电源

2019-11-14 16:18:58 3469

3469

Spartan-6 FPGA 利用CCL 支持布线线路与逻辑单元之间的可配置互联功能。Spartan-6 FPGA 是易失性器件- 电源移除时,不能保留原有配置。为了配置Spartan

2020-01-10 15:28:51 25

25 利用 FPGA 实现大型设计时,可能需要FPGA 具有以多个时钟运行的多重数据通路,这种多时钟FPGA 设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数据关系。设计过程中最重要的一步是确定要用多少个不同的时钟,以及如何进行布线,本文将对这些设计策略深入阐述。

2021-01-15 15:57:00 14

14 减少很多与多时钟域有关的问题,但是由于FPGA外各种系统限制,只使用一个时钟常常又不现实。FPGA时常需要在两个不同时钟频率系统之间交换数据,在系统之间通过多I/O接口接收和发送数据,处理异步信号,以及为带门控时钟的低功耗

2021-09-23 16:39:54 2763

2763 第9课:单片机数据传递类指令 2020/11/17

2021-11-20 11:51:06 0

0 Spartan-II主要包括CLBs,I/O块,RAM块和可编程连线(未表示出)。在spartan-II中,一个CLB包括2个Slices,每个slices包括两个LUT,两个触发器和相关逻辑

2022-09-21 14:34:23 1049

1049 电子发烧友网站提供《在Spartan 6 FPGA上从头开始实现全加器.zip》资料免费下载

2023-06-15 10:13:28 0

0 减少很多与多时钟域有关的问题,但是由于FPGA外各种系统限制,只使用一个时钟常常又不现实。FPGA时常需要在两个不同时钟频率系统之间交换数据,在系统之间通过多I/O接口接收和发送数据,处理异步信号,以及为带门控时钟的低功耗

2023-08-23 16:10:01 336

336 域时,由于时钟频率不同,所以可能会产生元件的不稳定情况,导致传输数据的错误。此时我们需要采取一些特殊的措施,来保证跨时钟域传输的正确性。 FPGA跨时钟域通信的基本实现方法是通过FPGA内部专门的逻辑元件进行数据传输。发送方用一个逻辑电路

2023-10-18 15:23:51 578

578

正在加载...

电子发烧友App

电子发烧友App

评论