最终生产模式:

不外挂存储器,8051代码存储于OTP存储器中,FP配置数据存于OTP或SPI FLASH中。因为OTP存储器是一次性的,所以不能用于调试阶段。一般产品最终定型后再使用OTP存储器可以获得最优的性能和最低的成本。

而当采用OTP 作为8051 代码内存,最高时钟频率可达100MHz。较理想的方法是用锁相环PLL来产生8051 时钟。CKCON SFR的低4位用来控制数据Memory 的等待周期。如果8051时钟频率高于45MHz,最好将value设置为大于等于2,以防止时钟太快,数据还没准备好。

也就是说,OTP方式可以达到51硬核代码运行的最佳性能,甚至于性能的速度瓶颈已经不是代码存取,而是数据存取。

以上三种模式是比较推荐的,但是特权同学从实际工程需要来考虑,简单的说,需要一种调试模式和一种生产模式。生产模式无可厚非的选择OTP烧录,而调试模式有点棘手,如果选择小模式,代码运行量太小,顶多不过2K,基本干不了什么事。而选择外扩SRAM,有限的IO资源不会允许的。所以,有点苦恼,但是还好,还有一种最次的选择——性能低下的第四种模式。

当8051的性能低于1.4MIPS时,可用spi flash作为8051的代码存储器。此模式的运行环境如下:

1. 选用片内 SPI FLASH;

2. FPGA的配置数据和8051代码存放在同一个SPI FLASH 里;

3. 8051 与SPI FLASH 接口大约需要90 个LE cells;

4. 8051 的内核时钟最快为30MHz 左右, 8051 最快运行性能大约为1.4MIPS;

5. 顺序取指需要 8 个时钟周期,跳转取指需要40 个周期;

在尝试SPI FLASH模式的时候,遇到了比较有意思的事。特权同学根据实例做SPI FLASH的运行测试,结果搞不定,也找不到相关的IP核。于是求问FAE,FAE直接告知这个IP核还没有集成到工具中,然后把源代码都发过来了。呵呵,虽然工具不完善,不过服务倒是很周到。

由于基于SPI FLASH的模式是在51硬核与SPI FLASH之间使用FPGA逻辑搭建了一个FLASH读取的模块。所以经过测试,确实这个FLASH读取控制的逻辑模块频率不能太高,过高FLASH就要**了,理论值是30M,而特权同学用了25M。然后使用上一篇手记同样的方法改变硬核的频率进行测试。

|

延时函数 |

EMB模式 |

SPI FLASH模式 |

||

|

50MHz |

100MHz |

50MHz |

100MHz |

|

|

Delay(1) |

5.0us |

2.5us |

20us |

20us |

|

Delay(2) |

6.6us |

3.3us |

27.5us |

27.5us |

|

Delay(3) |

8.3us |

4.2us |

35us |

35us |

|

Delay(4) |

9.9us |

5.0us |

42.5us |

42.5us |

|

i++与i |

约1.63us |

约0.83us |

约7.5us |

约7.5us |

结果证明,51硬核的频率受制于指令的读取速度,那么在SPI FLASH模式下速度性能确实大打折扣。

时序工具

关于时序工具的一些FAE解答:

问:你们的工具是否只提供所有输入输出管脚完全一致的时序约束?如tsu,th,tco,tpd的约束?如果不同管脚可以有不 同约束值,如何设置?

FAE:我们的工具提供的是时序分析功能,尚未提供时序约束功能,也就是说可以根据您输入的值作为参考,计算出当前实现的各种时序信息与参考值的差距,但并不会根据输入的值去做优化,所以也就不存在对不同管脚分别设置约束的功能了。

问:tco是指reg2pin的延时约束,tpd是指pin2pin的约束。而输入管脚约束tsu和th值,具体含义我不是很 明白?比如说我希望输入管脚的pin2reg延时为0-10ns,那么tsu和th如何设置?

FAE:tsu就可以理解为pin2reg的延时,它是信号从pin到FPGA内部第一个reg相对于这个reg的clock的setup time,而th就是相对这个clock的hold time,th一般不会有问题,需要关注的是tsu。

问:我尝试用GUI做了一些时序约束,然后每次做时序分析都报错:Error: T2000: (ice_run_sta) Run sta failed. 这是什么问题?

FAE:您的这个错误一般是sta设置上有什么问题,得具体分析工程。

今天终于拿到了最新3.2版本的软件,安装后,进行编译,长达近10分钟的placement让我眉头紧皱。后来从FAE处得知我拿到的是还未release出来的中间版本,有问题在所难免。不说这个,回到主题上来,其实总感觉有些遗憾。FAE在之前的回答其实已经预示着这个国产FPGA与特权同学缘分已到尽头。

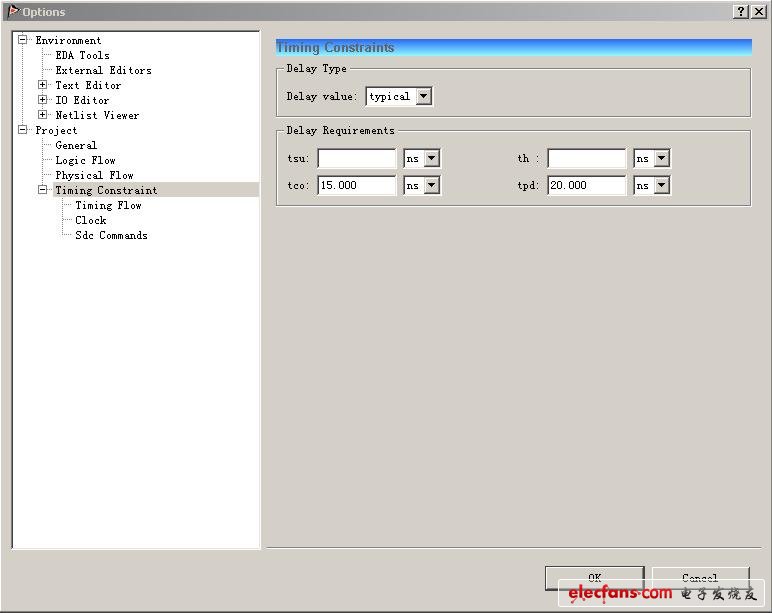

WHY?他们提供的时序分析工具根本算不上真正的时序分析工具,或者这么说,这个所谓的时序分析工具只能提供分析,而无法进行时序的约束和优化。即便他们的工程设置中也提供了如图1的恐怕可以称得上是最简单的“时序约束”,但这个所谓的“时序约束”其实并没有任何“约束”的作用。安装“官方”的说法,它不能够对综合乃至布局布线起到任何影响,而不过是给报告中的路径划了一条水平线,报告中确实能够体现出水平线上或下的状态。

图1

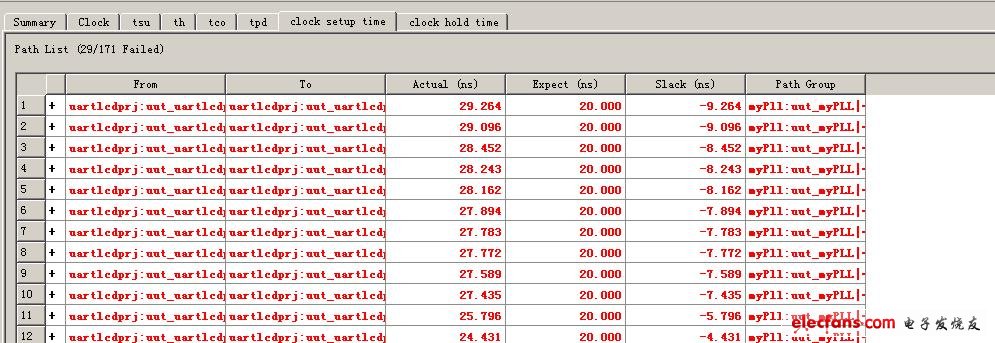

如图2所示,很无奈的只是移植了一个SDRAM控制器外加一些其它逻辑,占去了总共1000个LE中80%的资源,然后只是约束了一个50MHz的工作时钟,结果出来了20条false路径。即便尝试去试试用提供的仅有几个对mapping或palcement&routing设置的优化,结果换来了更多的false。FAE也坦言,目前只能做些简单的逻辑,跑个SDRAM等稍复杂的逻辑也就只能跑个二三十兆的样子。

图2

几天的试用,虽然以国产FPGA的性能问题而告夭折。虽然还显稚嫩的开发工具、差强人意的器件性能多少让人有些失望,但至少从某种程度上让特权同学改变了对国产的一些偏见。其实,如果Agate Logic能够持续这种开发热情,不断的改进,假以时日,相信他们会成为“中国的Altera”、“中国的Xilinx”。

外扩SFR使用

本以为这个国产FPGA的就此夭折,没想到权衡之后,在性能打些折扣的情况下还是重新捡起来了。从刚接触这个器件的时候特权同学就很关心它的硬核可扩展性,Avalone接口用上手了,当然很希望这个51硬核也能够提供类似的强大扩展接口。不过话说回来,毕竟是个8位的核,再强大也不到哪去,但在花了点心思琢磨了这个小玩意的扩展方式后,多少觉得还是有点花头的。

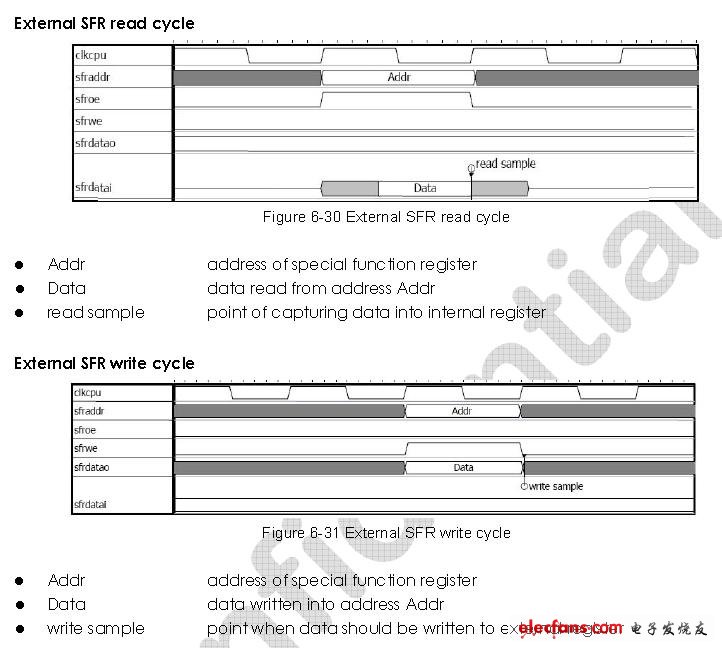

SFR,即特殊功能寄存器。SFR是8051单片机内部用于访问控制各种片上集成外设的主要寄存器,如常见的IO口(P0/P1/P2/P3)读写、IO中断配置、定时器配置、串口外设等。因此,对一般用户而言,玩转8051就是玩转SFR的过程。一般的单芯片8051单片机的SFR接口不对外开放,除了部分寄存器内部使用外,余下地址空间保留。而Astro器件的这颗8051硬核将空置的SFR地址空间开放给用户,提供了专门的对外接口时序。

特权同学将关于Astro器件SFR相关的特性整理如下:

● 可寻址空间0x80~0xff。

● 部分地址空间已被8051内部使用。

● 16个地址空间(能被8整除的地址如0x80、0x88、0x90、…0xf8等)可位寻址。

● 最多支持49个8051核外可用SFRs,除核内已占用的地址,余下地址空间均为用户可用的核外SFRs。

● 外部SFR接口含有等待状态寄存器(主要由sfack信号控制实现),允许8051内核与较慢的外设连接。

● 外部SFR读写时序如图3所示。

图3

为了简单的评估8051硬核的SFR扩展功能的性能,特权同学做了一些测试。

电子发烧友App

电子发烧友App

评论