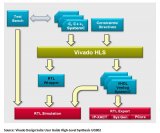

本在生产力方面进行了两大改进。Vivado设计套件2013.1版本新增了一款以IP为中心的设计环境,用以加速系统集成;而其提供的一套完整数据库,则可加速C/C++系统级设计和高层次综合(HLS)。

2013-04-08 15:08:54 902

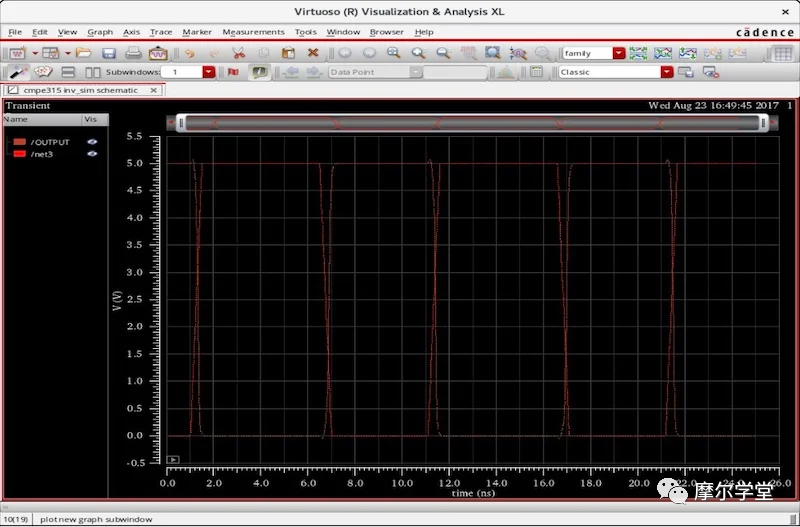

902 作者:Mculover666 1.实验目的 通过例程探索Vivado HLS设计流 用图形用户界面和TCL脚本两种方式创建Vivado HLS项目 用各种HLS指令综合接口 优化Vivado HLS

2020-12-21 16:27:21 3153

3153 综合(Synthesis)是指将RTL设计转换为门级描述。Vivado开发套件中的综合工具是一款时序驱动型、专为内存使用率和性能优化的综合工具,支持System Verilog 2012

2020-12-29 14:07:42 5432

5432 的Zynq 7000, 找了一个HLS的教程,就开始了如下入门实验,体验高级语言综合设计IP。Vivado HLS是Xilinx 推出的高层次综合工具,采用C/C++语言进行FPGA设计。HLS提供了一些

2020-10-14 15:17:19 2881

2881

51单片机是较早使用的了,现在单片机已发展到更高层次的STM32的单片机了。这个51类型的单片机还有发展前景吗?

2021-08-18 09:50:57

SoC器件上快速地加速和集成您的计算机视觉应用。本次研讨会将通过对一个具体案例的流程进行“逐层拆解(Step-by-Step)一个设计案列”的方式,向您介绍如何利用Vivado HLS(高层次综合

2013-12-30 16:09:34

Vivado下的工程能用Synplify综合吗?怎么找不到在综合工具添加的位置呢?

2019-06-04 09:45:16

菜鸟求指教,最近在用vivado 2015.3 做个小项目,遇到问题:代码综合后会报错:'get_property' expects at least one object.错误地址在IP的 clocks.xdc文件中。

2016-08-31 10:42:56

HLS高阶综合(highlevelsynthesis)在被广泛使用之前,作为商业技术其实已经存在了20多年。设计团队对于这项技术可以说呈现出两极化的态度:要么坚信它是先进技术之翘楚,要么对其持谨慎

2021-07-06 08:00:00

Vivado带来一些负面影响,以便在综合或布局布线期间进行性能优化?提前致谢。以上来自于谷歌翻译以下为原文I always see the training documents mentioned "

2019-03-21 12:42:34

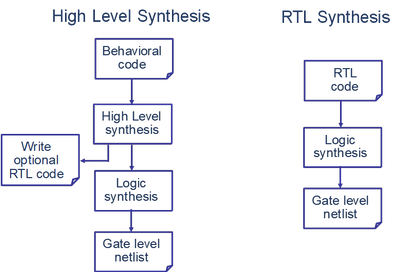

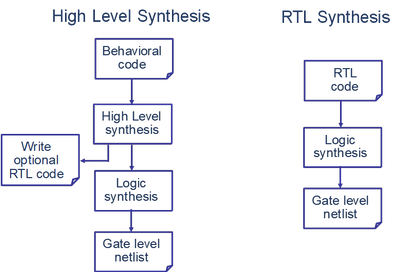

下图揭示了高层次综合工作的基本流程,以及它于传统的RTL综合流程的对比。接下来将对行为描述,行为综合,分析与优化三个主要子流程详细描述。 1、行为描述 当我们把HLS技术的起点立为一种

2021-01-06 17:52:14

高层次综合技术原理浅析

2021-02-01 06:04:00

描述语言(HDL)完成系统行为级设计,最后通过综合器和适配器生成最终的目标器件,这样的设计方法被称为高层次的电子设计方法。下面介绍与EDA基本特征有关的几个概念。

2019-10-08 14:25:32

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

1、HLS最全知识库介绍高层次综合(High-level Synthesis)简称HLS,指的是将高层次语言描述的逻辑结构,自动转换成低抽象级语言描述的电路模型的过程。对于AMD Xilinx而言

2022-09-07 15:21:54

fpga高手经验谈doc文档在数字电路的设计中,时序设计是一个系统性能的主要标志,在高层次设计方法中,对时序控制的抽象度也相应提高,因此在设计中较难把握,但在理解RTL电路时序模型的基础上,采用合理

2012-08-11 11:30:39

和实物控制实验,同时也为了高层次的设计开发实验提供良好的条件。为了结合教学要求,设计过程中参考了国内多种教材,从中...

2021-09-08 07:31:55

目录第1章:高层次生产力设计方法指南第2章:系统设计第3章:shell开发第4章:基于C语言的IP开发第5章:系统集成

2017-12-13 09:50:31

、仿真教学软件、模拟控制实训挂箱、实物与于一体,综合性强、功能齐全。 PLC部分可直观地进行基本指令训练,多个应用广泛的 PLC 实际应用模拟和实物控制训练,同时也为了高层次的设计开发实验实训提供良好

2021-09-03 08:53:06

、应用、后端支持.pdf直播简介:为了解决FPGA的可编程性问题,实现从算法到RTL设计的快速编译,我们引入了基于MLIR(多级别中间表示)的高层次综合框架ScaleHLS,对算法的高层次描述进行多级

2022-11-27 12:43:17

何使用硬件描述语言来完成设计,最终实现PL端LED闪烁的效果。在本章我们同样会通过LED闪烁实验,来讲解如何使用Vivado HLS工具对C语言进行高层次综合,并最终生成RTL级的实现结果,以及在

2020-10-10 16:48:25

1、使用Vitis HLS创建属于自己的IP高层次综合(High-level Synthesis)简称HLS,指的是将高层次语言描述的逻辑结构,自动转换成低抽象级语言描述的电路模型的过程。对于AMD

2022-09-09 16:45:27

嗨, 我们正在尝试将自定义IP连接到vivado的IP集成商中的可用IP。但我们在综合设计时发现了一些问题。请查看附带的截图以获取详细视图。谢谢。

2020-04-09 06:28:36

、sysfs等。中层次指被高层次封装调用的驱动,比如I2C、sdio等等。他们也有可能直接被应用层调用,这样就直接上升为高层驱动了。低层次驱动指被中层次调用封装的驱动,它们可能是platform驱动、GPIO驱动等等。驱动一般还存在混用,比如SDIO+网络驱动等等。那种单纯的简单的字符设备驱动,一

2021-12-24 06:10:40

SDK 2017.4。Xilinx Vivado HLS(High-Level Synthesis,高层次综合)工具支持将C、C++等语言转化成硬件描述语言,同时支持基于OpenCL等框架

2021-11-11 09:38:32

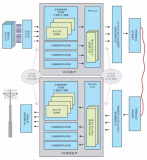

本文运用目前基于FPGA(Field Programmable Gate Array)的SoPC (System on Programmable Chip)技术构建软件无线电平台。大大提高了数字信号处理的能力和速度,并且降低了系统功耗,缩小了系统体积,为更高层次的3G无线通信要求提供了解决方案。

2021-05-06 06:21:24

您好我有一个关于vivado hls的问题。RTL是否来自xivix FPGA的vivado hls onyl?我们可以在Design Compiler上使用它进行综合吗?谢谢

2020-04-13 09:12:32

亲爱的大家,我现在正在使用Vivado 2013.3。我试图将PL结构时钟从1 MHZ更改为500KHZ。 (1 MHZ下没问题)但是,Vivado在运行综合时崩溃了。对我来说减少PL结构时钟非常重要,因为我打算在一个时钟周期内收集更多的XADC数据。我该怎么办?谢谢!

2020-03-25 08:40:07

利用Mentor高层次综合技术快速实现复杂DSP算法摘要:为了满足产品上市时间和功能丰富性的要求,越来越多的先进设计公司开始提高设计的抽象层次进行复杂的D

2010-04-29 14:01:59 34

34 摘要:Mentor公司提供的Catapult SL开发工具,不仅是快速算法验证,也是模块级结构设计和分析的有力工具,能有效地缩短产品的上市时间。本文首先回顾Catapult综合工具开发的基本流程

2010-06-08 08:07:11 11

11 随着半导体制造工艺的持续缩小,在90 纳米及以下的工艺中,时序、面积、功耗以及可制造性的问题都日趋复杂。设计者希望在电子系统级 (ESL) 设计阶段,就能知道他们的设

2010-07-04 11:44:09 13

13 在高层次对系统进行功耗佑算和功耗优化是soc设计的关健技术本文首先给出soc设计的特点和流程,然后综述目前高层次功耗估算和功耗优化的常用方法和技术,重点论述寄存器传输级和

2011-12-27 16:42:38 46

46 为了解决实现的瓶颈,Vivado 工具采用层次化器件编辑器和布局规划器、速度提升 了3 至 15 倍且为 SystemVerilog 提供业界领先支持的逻辑综合工具、速度提升 了4 倍且确定性更高的布局布

2012-04-25 10:54:16 59

59 Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高层次综合 (HLS) 进行 FPGA 设计的简介

2016-01-06 11:32:55 65

65 高层次综合设计最常见的的使用就是为CPU创建一个加速器,将在CPU中执行的代码移动到FPGA可编程逻辑去提高性能。本文展示了如何在Zynq AP SoC设计中使用HLS IP。 在Zynq器件

2017-02-07 18:08:11 3207

3207

最新 UltraFast™ 设计方法指南 和 UltraFast 高层次生产力设计方法指南 查看最新 Vivado QuickTake 视

2017-11-10 14:49:02 887

887 度更高的C语言层面上,加速算法开发;对软件工程师而言,它可以使软件工程师将计算密集型算法采用有别于传统CPU处理器的FPGA上实现。高层次综合可以使工程师在C语言层面上同时进行算法开发和算法验证。 Xilinx提供了另一工具Vivado HLS(Vivado High Level S

2017-02-08 12:39:34 265

265

HLx 版本均包括带有 C/C++ 库的 Vivado 高层次综合 (HLS)、Vivado IP 集成器 (IPI)、LogicCORE™ IP 子系统以及完整的 Vivado 实现工具套件,使主流用户能够方便地采用生产力最高、最

2017-02-08 19:35:06 386

386 高层次综合 (HLS)的增强功能,可实现更大型 IP 构建模块及相关模块的复用,从而有助于加快集成和验证速度,进

2017-02-09 01:15:42 225

225 Luke Miller并非一开始就是HLS(高层次综合)的倡导者。在使用早期的工具版本的时候,他似乎有过一些糟糕的经历。

2017-02-10 18:48:59 3334

3334

本文从程序员的角度对CNTK和TensorFlow做高层次的对比。本文也不属于性能分析,而是编程模型分析。文中会夹杂着大量的代码。 原标题:当TensorFlow遇见CNTK CNTK是微软用于搭建

2017-10-12 14:17:04 0

0 在使用高层次综合,创造高质量的RTL设计时,一个重要部分就是对C代码进行优化。Vivado Hls总是试图最小化loop和function的latency,为了实现这一点,它在loop

2017-11-16 14:44:58 3362

3362 ,有助于应对这种挑战。 我们使用 Vivado® Design Suite 的高层次综合 (HLS) 工具来评估针对 E-UTRA I/Q 数据的开放无线电设备接口 (ORI) 标准压缩方案,以估计其对信号

2017-11-16 20:05:41 1918

1918

使用Xilinx Vivado HLS(Vivado 高层次综合)工具实现浮点复数QRD矩阵分解并提升开发效率。使用VivadoHLS可以快速、高效地基于FPGA实现各种矩阵分解算法,降低开发者

2017-11-17 17:47:43 3293

3293

如果您正在努力开发计算内核,而且采用常规内存访问模式,并且循环迭代间的并行性比较容易提取,这时,Vivado® 设计套件高层次综合(HLS) 工具是创建高性能加速器的极好资源。通过向C 语言高级算法描述中添加一些编译指示,就可以在赛灵思FPGA 上快速实现高吞吐量的处理引擎。

2017-11-17 18:12:01 1647

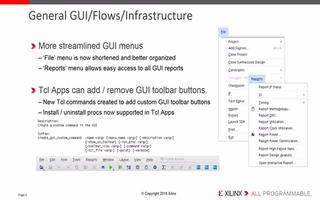

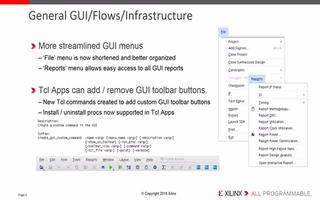

1647 在ISE下,对综合后的网表进行编辑几乎是不可能的事情,但在Vivado下成为可能。Vivado对Tcl的支持,使得Tcl脚本在FPGA设计中有了用武之地。本文通过一个实例演示如何在Vivado下利用Tcl脚本对综合后的网表进行编辑。

2017-11-18 03:16:01 6899

6899

众多应用中的一个,而且创建定制硬件需要花费时间和成本。是不是这样? 最近听说了赛灵思的高层次综合工具Vivado®HLS后,我开始重新思考这一问题。高层次综合工具与Zynq®-7000 All Programmable SoC的结合为设计开辟了新的可能性。

2017-11-18 09:12:24 1192

1192

Vivado的高层次综合功能将帮助您为嵌入式视频应用设计更好的排序网络。从汽车到安全系统再到手持设备,如今采用嵌入式视频功能的应用越来越多。每一代新产品都需要更多的功能和更好的图像质量。但是,对于

2017-11-18 11:02:02 1681

1681 理由一:突破器件密度极限:在单个器件中更快速集成更多功能;理由二:Vivado以可预测的结果提供稳健可靠的性能和低功耗;理由三:Vivado设计套件提供了无与伦比的运行时间和存储器利用率;理由四:使用Vivado高层次综合生成基于C语言的IP。

2017-11-22 08:15:19 1421

1421 使用高层次综合方法设计超大规模集成电路是一项前瞻性的工作。其设计理念旨在保证电路性能的前提下,缩短电路开发周期,让产品更早投入到市场。然而针对高层次综合工具面对算法转换时编译能力存在局限的问题,本文

2017-11-22 10:11:55 1

1 Vivado HLS配合C语言等高级语言能帮助您在FPGA上快速实现算法。 高层次综合(HLS)是指自动综合最初用C、C++或SystemC语言描述的数字设计。工程师之所以对高层次综合如此感兴趣,不仅是因为它能让工程师在较高的抽象层面上工作,而且还因为它能方便地生成多种设计解决方案。

2019-10-06 10:44:00 1178

1178

我们使用 Vivado ®Design Suite 的高层次综合 (HLS) 工具来评估针对 E-UTRA I/Q 数据的开放无线电设备接口 (ORI) 标准压缩方案,以估计其对信号保真度的影响、造成的时延及其实现成本。我们发现赛灵思的 Vivado HLS 平台能够高效评估和实现所选压缩算法。

2018-07-24 09:30:00 1901

1901

Verilog的主要应用包括:

– ASIC和FPGA工程师编写可综合的RTL代码

– 高抽象级系统仿真进行系统结构开发

– 测试工程师用于编写各种层次的测试程序

– 用于ASIC和FPGA单元或更高层次的模块的模型开发

2018-08-09 08:00:00 36

36 、HL 设计版本和 HL WebPACK 版本。所有 HLx 版本均包括带有 C/C++ 库的 Vivado 高层次综合 (HLS)、Vivado IP 集成器 (IPI)、LogicCORE IP

2018-08-17 11:43:00 2677

2677 All Programmable SoC 的生产力带来重大突破。伴随此款最新版Vivado 设计套件推出的还包括其内含的 Vivado 高层次综合(HLS)和IP集成器的增强功能,以及最新性能监控

2018-09-06 16:07:00 1466

1466 达25%,性能提升5%。此外,2014.1版本还在Vivado HLS(高层次综合)中新增了OpenCL内核硬件加速功能。

2018-09-13 16:59:00 1199

1199 新增了一款以IP为中心的设计环境,用以加速系统集成;而其提供的一套完整数据库,则可加速C/C++系统级设计和高层次综合(HLS)。 加速IP创建与集成 为了加速在All Programmable

2018-09-25 09:18:01 275

275 关键词:汽车 中国.玉环首届国际高层次人才创业创新大赛 沈阳分赛区 报名时间:2018年10月11日-10月21日 o立即报名 一、目的和意义 “为深入贯彻省委省政府和市委市政府关于推进“大众创业

2018-10-27 16:24:01 170

170 观看视频,学习如何将 Vivado IP 和第三方综合工具配合使用。 此视频将通过一个设计实例引导您完成创建自定义 IP 的步骤;用第三方综合工具IP黑盒子来审查所需 IP 输出;整合 Vivado IP 网表和第三方综合工具网表的两个方法,即 “网表项目模式” 和 “非项目 Tcl 脚本模式”。

2018-11-21 06:34:00 4811

4811 本视频重点介绍了Vivado设计套件2018.1版本中的新增功能,包括对操作系统以及器件的支持情况,还有高层次增强功能,以及各种功能改进以加速设计集成,实现和验证的过程。

2018-11-20 06:28:00 2254

2254

的需求。客户可在 Zynq® MPSoC 和 UltraScale™ FPGA 芯片平台上使用 Vivado® 高层次综合 (HLS)、 SDSoC™、和 SDAccel™ 软件定义环境。Xilinx

2019-12-26 07:01:00 1409

1409

Xilinx 战略应用高级工程师。专注于 C/C++ 高层次综合,拥有多年利用 Xilinx FPGA 实现数字信号处理算法的经验,对 Xilinx FPGA 的架构、开发工具和设计理念有深入的理解

2019-08-01 15:43:09 3508

3508 从 Vivado 2019.1 版本开始,Vivado 综合引擎就已经可以支持增量流程了。这使用户能够在设计变化较小时减少总的综合运行时间。

2019-07-21 11:02:08 1367

1367 高层次综合(High-level Synthesis)简称 HLS,指的是将高层次语言描述的逻辑结构,自动转换成低抽象级语言描述的电路模型的过程。所谓的高层次语言,包括 C、C++、SystemC

2019-11-21 16:28:56 8888

8888 意见明确,将人工智能纳入“国家关键领域急需高层次人才培养专项招生计划”支持范围,综合考虑有关高校高水平师资、国家级科研平台、重大科研项目和攻关任务,以及产教融合、协同育人成效等情况,安排研究生尤其是博士生招生计划专项增量。

2020-03-05 11:29:17 1635

1635 意见明确,将人工智能纳入“国家关键领域急需高层次人才培养专项招生计划”支持范围,综合考虑有关高校高水平师资、国家级科研平台、重大科研项目和攻关任务,以及产教融合、协同育人成效等情况,安排研究生尤其是博士生招生计划专项增量。

2020-03-07 15:47:47 1819

1819 -flatten_hierarchy full: 综合时将原始设计打平,只保留顶层层次,执行边界优化 none: 综合时完全保留原始设计层次,不执行边界优化 rebuilt: 综合时将原始设计打平

2020-11-25 10:28:49 8164

8164 12月23日,据杭州市人力资源和社会保障局消息,阿里巴巴蒋凡被认定为蒋凡被认定为高层次人才,消息曝光后引发网友热议。

2020-12-30 11:12:34 1969

1969 说起高层次综合技术(High-level synthesis)的概念,现在有很多初学者简单地把它理解为可以自动把c/c++之类地高级语言直接转换成底层硬件描述语言(RTL)的技术。其实更准确的表述

2021-01-14 09:27:28 1848

1848 说起高层次综合技术(High-level synthesis)的概念,现在有很多初学者简单地把它理解为可以自动把c/c++之类地高级语言直接转换成底层硬件描述语言(RTL)的技术。其实更准确的表述是:由更高抽象度的行为描述生产电路的技术。

2022-02-08 17:26:42 7041

7041

作为碧桂园集团旗下的初创型企业,博智林机器人副总裁刘震分享了打造高层次人才队伍布局先进制造业的经验。 建筑行业和农业一样,是信息化、自动化、智能化水平比较低的行业。博智林要做的研发很多。 刘震

2021-01-26 15:22:48 2814

2814 说起高层次综合技术(High-level synthesis)的概念,现在有很多初学者简单地把它理解为可以自动把c/c++之类地高级语言直接转换成底层硬件描述语言(RTL)的技术。其实更准确的表述是:由更高抽象度的行为描述生产电路的技术。

2021-01-28 09:11:08 3

3 在FPGA设计里,设计仿真完成RTL代码设计后便是交给设计套件进行综合及布局布线。在综合过程里,Vivado里提供的参数选项有点儿多,今天闲暇抽空梳理下。 -flatten_hierarchy

2021-06-01 11:20:35 6511

6511 1.实验目的通过例程探索Vivado HLS设计流用图形用户界面和TCL脚本两种方式创建Vivado HLS项目用各种HLS指令综合接口优化Vivado HLS设计来满足各种约束用不用的指令来探索

2021-11-06 09:20:58 6

6 本文将从高层次探讨什么是虚拟内存、它存在的原因以及它是如何工作的。

2022-04-28 17:06:56 1363

1363

Vitis HLS 是一种高层次综合工具,支持将 C、C++ 和 OpenCL 函数硬连线到器件逻辑互连结构和 RAM/DSP 块上。Vitis HLS 可在Vitis 应用加速开发流程中实现硬件

2022-05-25 09:43:36 1930

1930 VitisHLS是一种高层次综合工具,支持将C、C++和OpenCL函数硬连线到器件逻辑互连结构和RAM/DSP块上。

2022-06-14 09:20:51 1946

1946 Vitis 环境开发方法论反应了 Versal ACAP 系统的异构性质,此类系统通常是由 PS、PL 和 AI 引擎功能组成的。您可使用 Vitis 工具来独立开发并验证这些组件,并逐渐将其加以集成以构成最终系统。

2022-06-16 10:23:38 971

971 基于硬件描述语言HDL,抽象出HLS(High-Level Synthesis)(翻译为高层次综合?怎么听起来都沉得别扭)技术,通过高层设计去隐藏很多底层逻辑和细节,让FPGA的开发更加简单。

2022-09-05 09:12:48 704

704 这是一个关于系统构成和芯片架构的高层次描达文件,涉及芯片的高层次操作、引脚分配与定义、软件编程模型、可测性、寄存器定义以及应用模型等。

2022-11-10 20:48:51 10610

10610 这是一个关于系统构成和芯片架构的高层次描达文件,涉及芯片的高层次操作、引脚分配与定义、软件编程模型、可测性、寄存器定义以及应用模型等。

2022-11-10 16:25:15 1256

1256 01 演讲题目 ✦ 开源硬件系列02期: 从PyTorch到RTL - 基于MLIR的高层次综合技术 02 演讲时间 ✦ 2022年11月27日 上午 10:00 03 内容简介 ✦ 为了解

2022-11-24 08:15:03 1379

1379 英特尔® NUC 8 支持更高层次的设计

2022-12-29 10:02:52 619

619

)和连线(wire)息息相关。Verilog便具有将ASM图表和电路框图用计算机语言表达的能力,本文将讲述Vivado综合支持的Verilog硬件描述语言; Verilog提供了行为化和结构化两方面的语言结构,描述设计对象时可以选择高层次或低层次的抽象等级。使用V

2022-12-29 10:30:09 3387

3387 模拟IC设计与数字 IC 设计有很大不同。其中数字IC设计在与确定的栅- /晶体管级放置和路由的具体系统和过程的抽象水平大多进行,模拟IC设计通常涉及更个性化的焦点到每个电路,甚至大小和每个具体晶体管。

2023-03-16 10:36:09 333

333

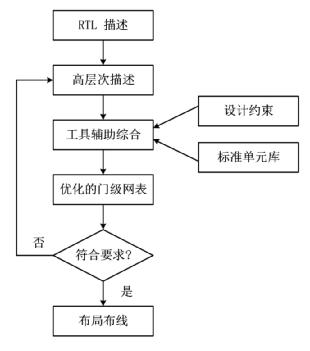

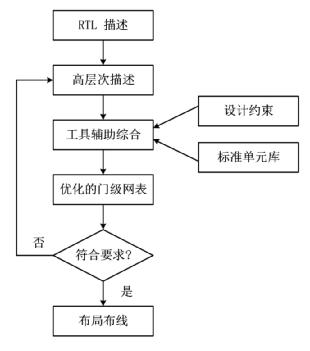

综合,就是在标准单元库和特定的设计约束基础上,把数字设计的高层次描述转换为优化的门级网表的过程。标准单元库对应工艺库,可以包含简单的与门、非门等基本逻辑门单元,也可以包含特殊的宏单元,例如乘法器、特殊的时钟触发器等。设计约束一般包括时序、负载、面积、功耗等方面的约束。

2023-03-30 11:45:49 556

556

“工业控制系统层次模型”是为了解决工业控制系统设计中的复杂性而提出的一种模型。该模型将整个控制系统分为4个层次,即系统层次、任务层次、结构层次和实现层次。

1、系统层次:即控制系统的高层次

2023-04-19 16:41:43 542

542 如果你正在使用Vivado开发套件进行设计,你会发现综合设置中提供了许多综合选项。这些选项对综合结果有着潜在的影响,而且能够提升设计效率。为了更好地利用这些资源,需要仔细研究每一个选项的功能。本文将要介绍一下Vivado的综合参数设置。

2023-05-16 16:45:50 1857

1857

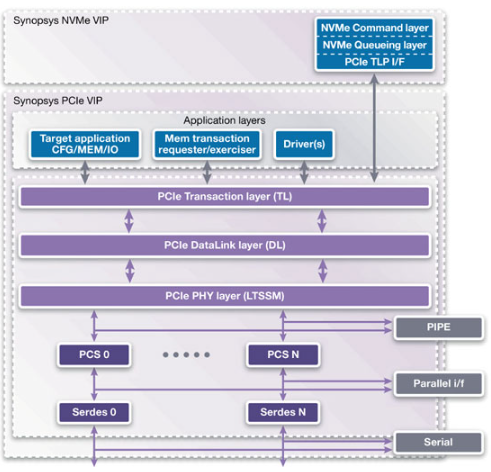

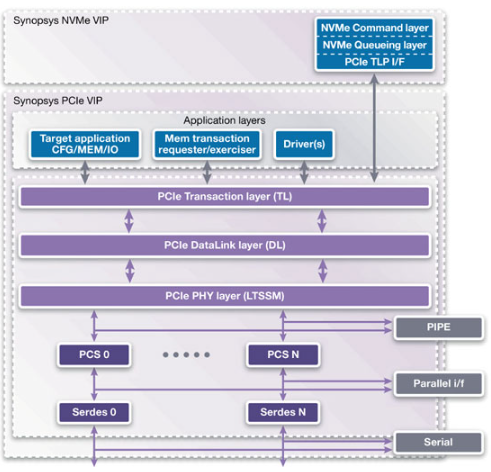

的 Synopsys NVMe 验证 IP (VIP) 是一个综合测试工具,由两个主要子系统组成——第一个是 SVC(系统验证组件),第二个是 SVT(系统验证技术)。

2023-05-26 17:41:20 1080

1080

Vivado综合默认是timing driven模式,除了IO管脚等物理约束,建议添加必要的时序约束,有利于综合逻辑的优化,同时综合后的design里面可以评估时序。

2023-07-03 09:03:19 414

414 这通常需要由工程师团队编写代码(如Verilog、Chisel或C/C++等),然后在电子设计自动化(EDA)工具(如逻辑综合或高层次综合工具)的辅助下生成电路逻辑。

2023-07-03 11:16:48 784

784

电子发烧友网站提供《Vivado Design Suite用户指南:综合.pdf》资料免费下载

2023-09-13 15:47:40 0

0 电子发烧友网站提供《UltraFast高层次生产力设计方法指南.pdf》资料免费下载

2023-09-15 10:41:47 0

0 电子发烧友网站提供《使用Vivado高层次综合(HLS)进行FPGA设计的简介.pdf》资料免费下载

2023-11-16 09:33:36 0

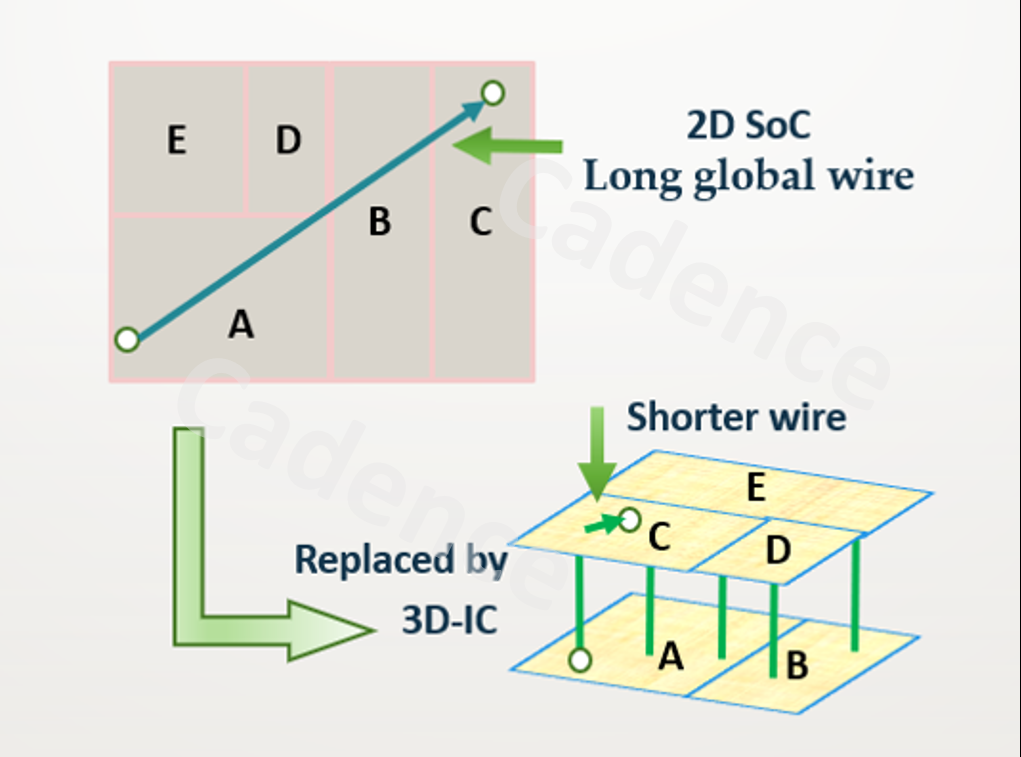

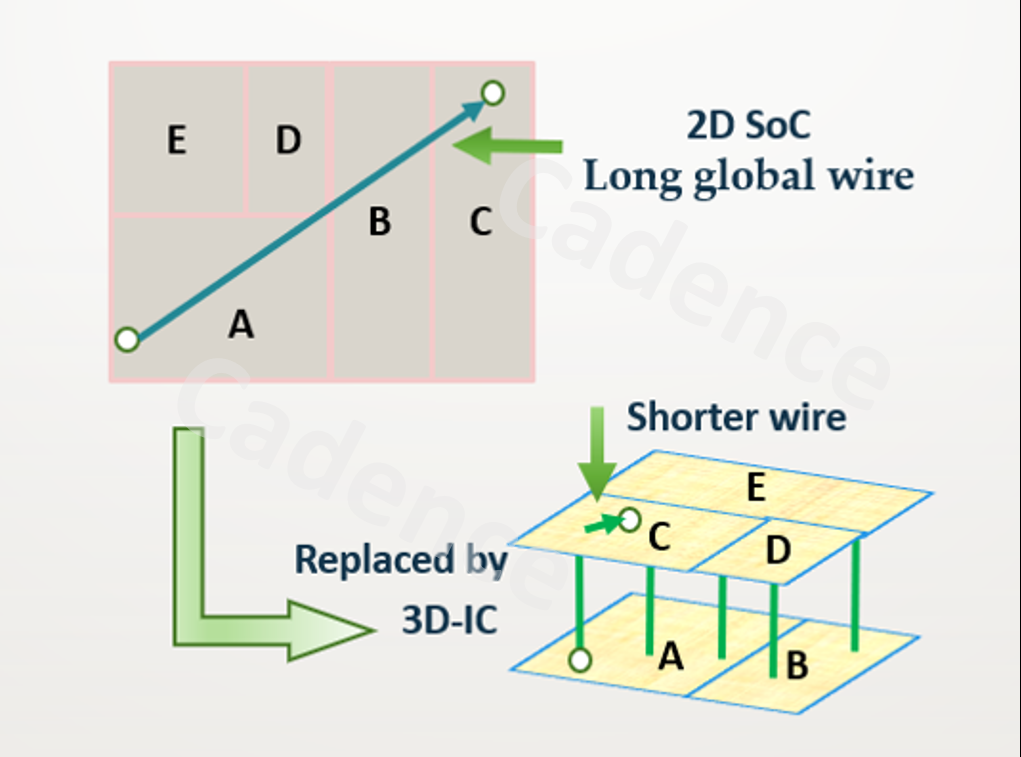

0 3D-IC 设计之早期三维布图综合以及层次化设计方法

2023-12-04 16:53:58 200

200

近日,中共南京市委人才工作领导小组发布了南京市“紫金山英才计划高层次创新创业人才项目”评审结果,宙讯科技董事长周冲成为该项目入选人才。

2024-02-26 09:23:47 376

376

电子发烧友App

电子发烧友App

评论