在FPGA 上设计一个高性能、灵活的、面积小的通信体系结构是一项巨大的挑战。大多数基于FPGA 的片上网络都是运行在一个单一时钟下。随着FPGA 技术的发展,Xilinx 公司推出了Virtex-4 平台

2011-10-21 16:13:51 1270

1270

在多时钟设计中可能需要进行时钟的切换。由于时钟之间可能存在相位、频率等差异,直接切换时钟可能导致产生glitch。

2020-09-24 11:20:38 5317

5317

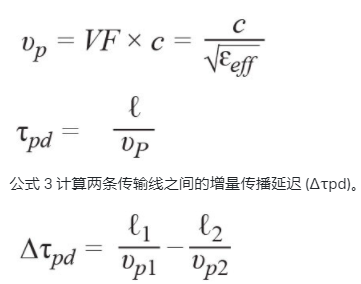

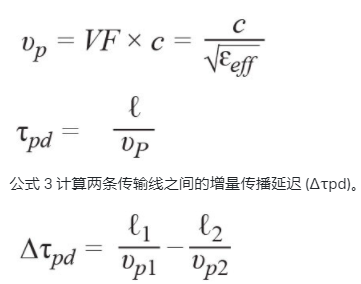

01、如何决定FPGA中需要什么样的时钟速率 设计中最快的时钟将确定 FPGA 必须能处理的时钟速率。最快时钟速率由设计中两个触发器之间一个信号的传输时间 P 来决定,如果 P 大于时钟周期

2020-11-23 13:08:24 3565

3565

把握DCM、PLL、PMCD和MMCM知识是稳健可靠的时钟设计策略的基础。 赛灵思在其FPGA中提供了丰富的时钟资源,大多数设计人员在他们的FPGA设计中或多或少都会用到。不过对FPGA设计新手来说

2021-02-13 17:02:00 2014

2014

。Xilinx FPGA7系列分为全局时钟(Global clock)和局部时钟(Regional clock)资源。目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期

2023-07-24 11:07:04 655

655

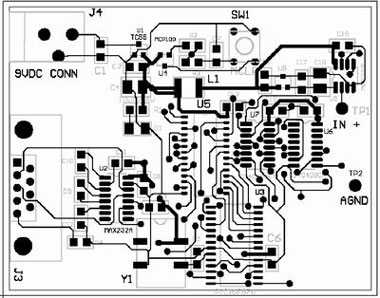

。在本文中,我们将讨论自动布线功能的正确使用和错误使用,有无地平面时电流回路的设计策略,以及对双面板元件布局的建议。

2023-09-26 09:41:54 389

389

有一个有趣的现象,众多数字设计特别是与FPGA设计相关的教科书都特别强调整个设计最好采用唯一的时钟域。

2023-12-22 09:04:46 875

875

本帖最后由 lee_st 于 2017-10-31 08:58 编辑

FPGA多时钟设计

2017-10-21 20:28:45

大型设计中FPGA 的多时钟设计策略Tim Behne 软件与信号处理部经理 Microwave Networks 公司Email: timothyb@microwavenetworks.com利用

2012-10-26 17:26:43

利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数据关系。设计过程中最重要的一步是确定要用多少个不同的时钟,以及如何进行布线?

2019-08-30 08:31:41

摘要:FPGA异步时钟设计中如何避免亚稳态的产生是一个必须考虑的问题。本文介绍了FPGA异步时钟设计中容易产生的亚稳态现象及其可能造成的危害,同时根据实践经验给出了解决这些问题的几种同步策略。关键词

2009-04-21 16:52:37

FPGA的多时钟系统设计 Multiple Clock System Design Clk1and Clk2are the clock which running at different frequency[/hide]

2009-12-17 15:46:09

EDA技术具有什么特征?FPGA是什么原理?FPGA设计应用及优化策略基于VHDL的FPGA系统行为级设计

2021-04-15 06:33:58

采用FPGA来设计一款广泛应用于计算机、Modem、数据终端以及许多其他数字设备之间的数据传输的专用异步并行通信接口芯片,实现了某一时钟域(如66 MHz)的8位并行数据到另一低时钟域(如40 MHz)16

2011-09-07 09:16:40

本帖最后由 mingzhezhang 于 2012-5-23 20:05 编辑

大型设计中FPGA的多时钟设计策略 利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重

2012-05-23 19:59:34

利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数据关系。设计过程中

2015-05-22 17:19:26

人工智能大热之前,Cloud或Data Center已经开始使用FPGA做各种加速了。而随着Deep Learning的爆发,这种需求越来越强劲。本文主要讨论Cloud巨头Amazon和Microsoft的FPGA策略。

2019-08-13 08:37:24

1、IC设计中的多时钟域处理方法简析我们在ASIC或FPGA系统设计中,常常会遇到需要在多个时钟域下交互传输的问题,时序问题也随着系统越复杂而变得更为严重。跨时钟域处理技术是IC设计中非常重要的一个

2022-06-24 16:54:26

利用 FPGA 实现大型设计时,可能需要FPGA 具有以多个时钟运行的多重数据通路,这种多时钟 FPGA 设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数据关系

2012-03-05 14:42:09

跨越时钟域FPGA设计中可以使用多个时钟。每个时钟形成一个FPGA内部时钟域“,如果需要在另一个时钟域的时钟域产生一个信号,需要特别小心。隧道四部分第1部分:过路处。第2部分:道口标志第3部分:穿越

2012-03-19 15:16:20

目前高速PCB的设计在通信、计算机、图形图像处理等领域应用广泛。而在这些领域工程师们用的高速PCB设计策略也不一样。 在电信领域,设计非常复杂,在数据、语音和图像的传输应用中传输速度已经远远

2016-10-16 12:57:06

` 本帖最后由 gk320830 于 2015-3-4 14:11 编辑

世界十大设计团队的经典设计策略`

2013-09-13 19:44:35

本文就以太网保护设计方面提出设计策略以及几种应对的设计思路,正如不同的标准中都有多个级别的防护等级,用户需要根据实际的项目应用场景来选择合适的方案,这包括PCB 设计、器件选择、成本、信号一致性等

2020-12-28 06:35:21

把握DCM、PLL、PMCD和MMCM知识是稳健可靠的时钟设计策略的基础。赛灵思在其FPGA中提供了丰富的时钟资源,大多数设计人员在他们的FPGA设计中或多或少都会用到。不过对FPGA设计新手来说

2020-04-25 07:00:00

在FPGA 上设计一个高性能、灵活的、面积小的通信体系结构是一项巨大的挑战。大多数基于FPGA 的片上网络都是运行在一个单一时钟下。随着FPGA 技术的发展,Xilinx 公司推出了Virtex-4

2019-08-21 06:47:43

把握DCM、PLL、PMCD和MMCM知识是稳健可靠的时钟设计策略的基础。赛灵思在其FPGA中提供了丰富的时钟资源,大多数设计人员在他们的FPGA设计中或多或少都会用到。不过对FPGA设计新手来说,什么时候用DCM、PLL、PMCD和MMCM四大类型中的哪一种,让他们颇为困惑。

2019-09-18 08:26:21

供电的便携嵌入式系统电源设计都是有帮助的。根据本文描述的构造模块,读者可以为特定设计选择合适的器件以及设计策略。

2019-07-26 07:23:19

对多时钟系统的同步问题进行了讨论å提出了亚稳态的概念及其产生机理和危害;叙述了控制信号和数据通路在多时钟域之间的传递õ讨论了控制信号的输出次序对同步技术的不同要求,重点论述了常用的数据通路同步技术----用FIFO实现同步的原理及其实现思路

2012-05-23 19:54:32

大型设计中FPGA的多时钟设计策略利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟

2020-04-26 07:00:00

笔记本电脑的EMI设计策略

2009-08-16 13:39:19

。虽然这样可以简化时序分析以及减少很多与多时钟域有关的问题,但是由于FPGA外各种系统限制,只使用一个时钟常常又不现实。FPGA时常需要在两个不同时钟频率系统之间交换数据,在系统之间通过多I/O接口接收

2022-10-14 15:43:00

目前高速PCB的设计在通信、计算机、图形图像处理等领域应用广泛。而在这些领域工程师们用的高速PCB设计策略也不一样。 在电信领域,设计非常复杂,在数据、语音和图像的传输应用中传输速度已经远远

2018-11-27 10:15:02

Multiple Clock System Design PLD设计技巧—多时钟系统设计

Information Missing

Max+Plus II does

2008-09-11 09:19:41 25

25 通过介绍BOVA 公司的产品设计实践来认识客车产品的形象识别设计策略。关键词: 客车; 产品形象识别; 设计策略Abstract: The article touches upon the bus p roduct identity design strategy th rough

2009-07-27 14:45:37 10

10 单片机系统的低功耗设计策略:摘要嵌入式系统的低功耗设计需要全面分析各方面因素,统筹规划。在设计之初,各个因素往往是相互制约、相互影响的,一个降低系统功耗的措施有

2009-10-27 17:44:03 26

26 DLL在FPGA时钟设计中的应用:在ISE集成开发环境中,用硬件描述语言对FPGA 的内部资源DLL等直接例化,实现其消除时钟的相位偏差、倍频和分频的功能。时钟电路是FPGA开发板设计中的

2009-11-01 15:10:30 33

33 PLC控制系统抗干扰技术设计策略

自动化系统所使用的各种类型PLC中,有的是集中安装在控制室,有的是安装在生产现场和各电机设备上

2009-06-19 14:33:09 297

297 RFID芯片的攻击技术分析及安全设计策略

本文以采用磁耦合和CMOS工艺的RFID产品为例,简要介绍了此类芯片的构成,在列举各种破坏性/非破坏性攻击手段的基础上,从软

2009-12-26 14:41:47 1205

1205 高可靠性嵌入式系统固件设计策略

本文针对如何编写易理解、易维护的优秀代码进行了讨论,为程序员提供了一些非常实用的编程指导。文中指出

2009-12-26 14:42:39 546

546 大型设计中FPGA的多时钟设计策略

利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率

2009-12-27 13:28:04 645

645

便携电子设备的高效电源系统设计策略

对于电池供电的便携设备而言,除了需要突破处理能力的限制外,便携式系统电源的性能也需要不断改进。本文探讨便携嵌入式

2010-03-30 17:28:10 304

304 基于集成温度传感器的有源电子标签设计策略

射频识别RFID(Radio Frequency Identification)技术是近年来开始兴起并逐渐走向成熟的一种自动识

2010-04-20 15:37:31 1045

1045

MSP430F149的无线环境监测传感器系统设计策略

微处理器模块

C

2010-04-20 15:50:18 772

772

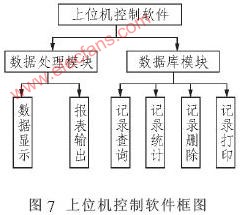

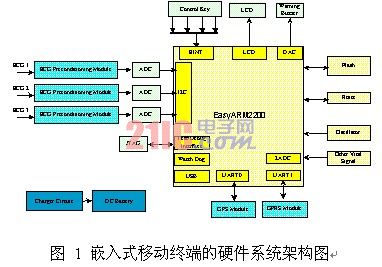

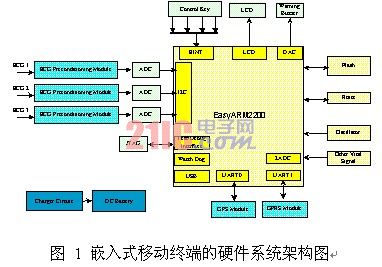

根据高危心脏病人远程实时监护系统设计策略

1 引言 心血管疾病发病往往十分危急,且病情严重、变化迅速,一旦发作就可能给病人带来巨大痛苦、甚至导致晕

2010-04-21 09:46:13 853

853

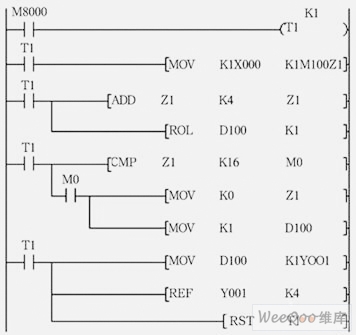

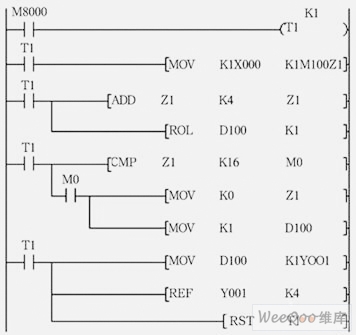

基于组扫描的PLC开关量采集方法设计策略

概 述:针对大量开关量信号输入的问题,以日本三菱公司的fx系列plc为例,本文设计了一种基于组扫描输入的plc开关量

2010-04-21 10:59:25 937

937

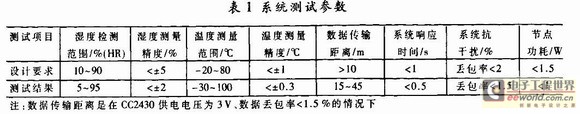

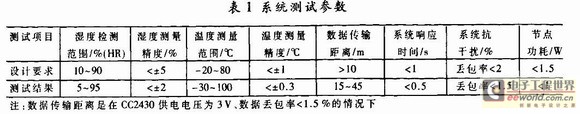

根据ZigBee的汽车空调控制系统设计策略

摘 要: 针对汽车空调系统的实时性要求,提出了一种基于ZigBee技术的汽车空

2010-04-21 16:50:21 864

864

根据TCP/IP的浮标网络通信系统设计策略

水声信道匹配基础研究是建立在水声学、海洋物理声学以及现代信号处理技术基础上的新兴研究领域。为满足研究需要而构建的

2010-04-22 12:38:28 1752

1752

根据ARM的LCD触摸屏系统设计策略

随着嵌入式系统技术的飞速发展,工业设备产品也越来越现代化,普遍要求可视化操作。LCD触摸屏低耗能.散热小,成

2010-04-22 13:55:26 995

995

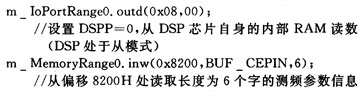

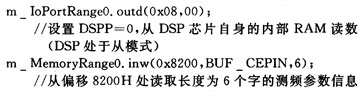

根据PCI总线的实时测频卡WDM驱动程序设计策略

PCI总线是一种与CPU无关的32/64位地址数据复用总线,工作频率为33 MHz/66 MHz,它支持突发传输,具有即插即用、电源管理等

2010-04-23 10:33:38 1269

1269

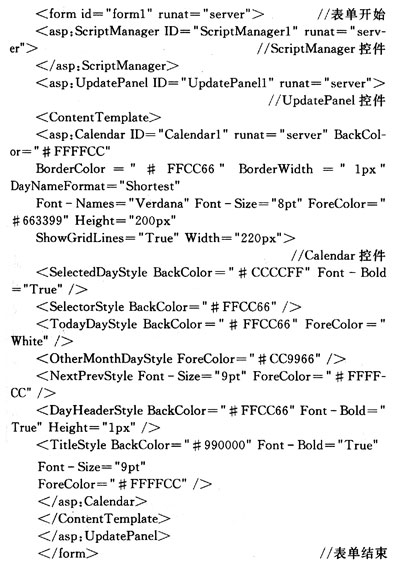

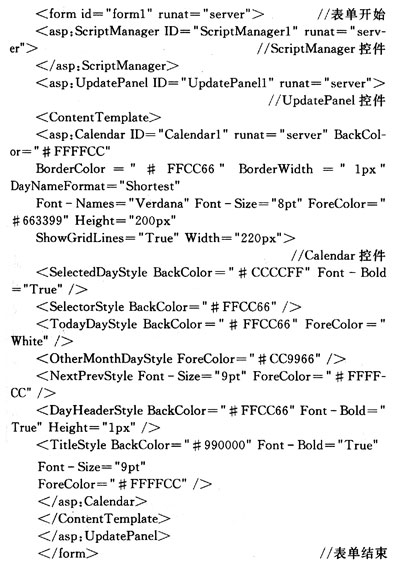

基于ASP.NET AJAX的OA系统设计策略0 引言办公自动化(Office Automation,OA)系统,是指利用计算机技术和网络技术,使办公室部分工作逐步物化于各种现代化设备中,由

2010-04-23 10:38:10 613

613

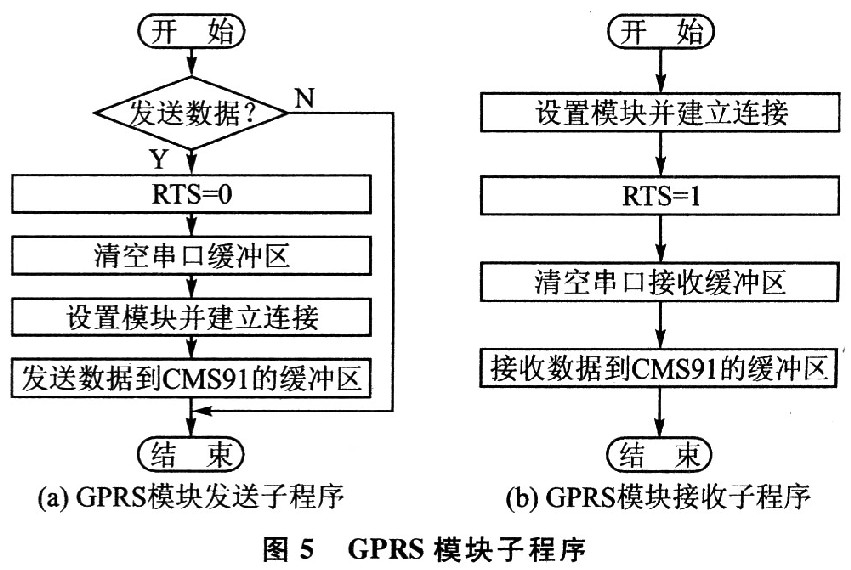

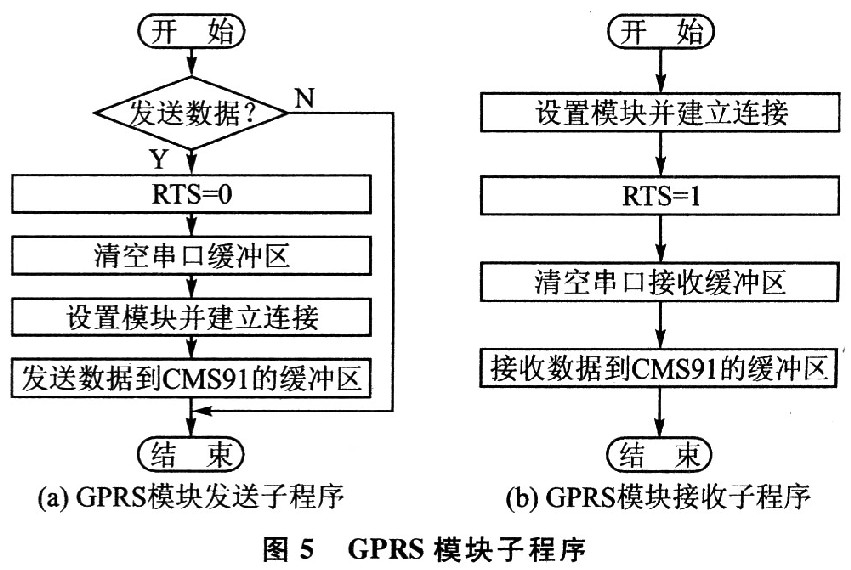

基于GPRS和PLC的远程路灯监控系统设计策略

1 GPRS技术简介 GPRS(General Packet Radio Service,通用分组无线业务)是一种基于第二代移动通信系统GSM的无线分组

2010-04-23 11:29:55 952

952

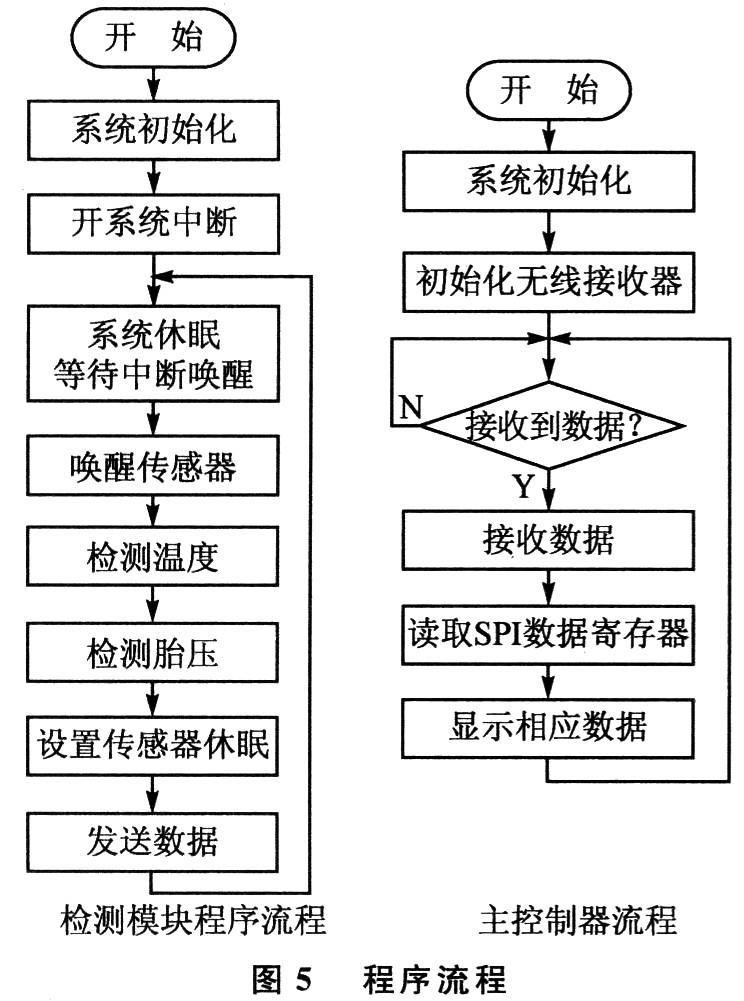

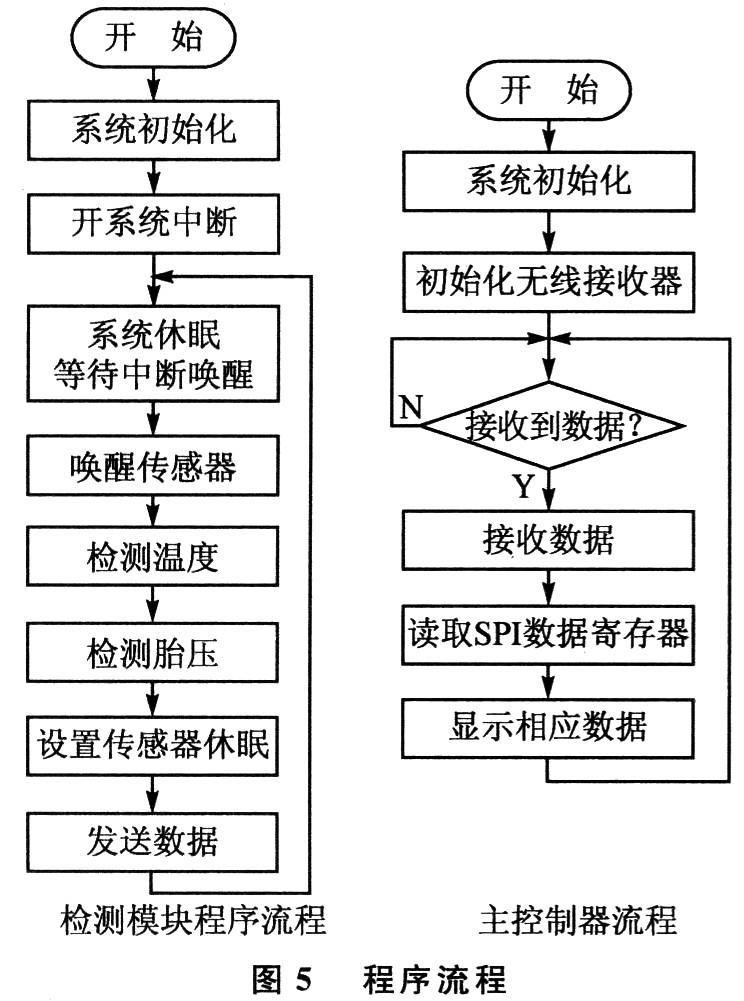

基于智能传感器MPXY8320A的TPMS系统设计策略

1 TPMS系统的发展历史和趋势1.1 TPMS系统的发展历史 国际市场,1997年,通用汽车公司开始使用间接式汽

2010-04-23 11:48:27 1097

1097

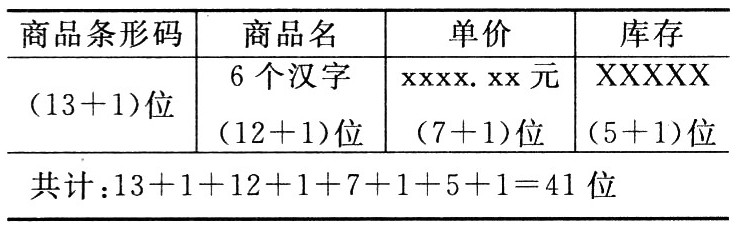

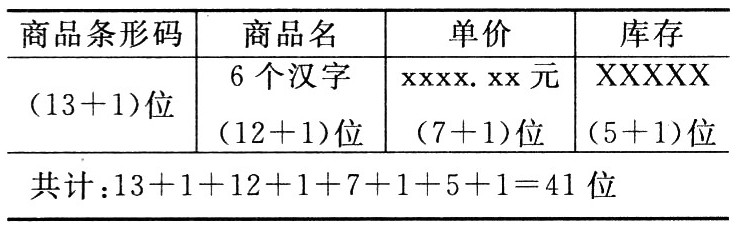

基于LPC2138的超市收银机系统设计策略

ARM7 LPC2138介绍 Philips公司的32位的ARM7 LPC2138微控制器具有强大的存储空间,内嵌32 KB片内静态RAM和512KB的Flash

2010-04-23 11:50:36 3506

3506

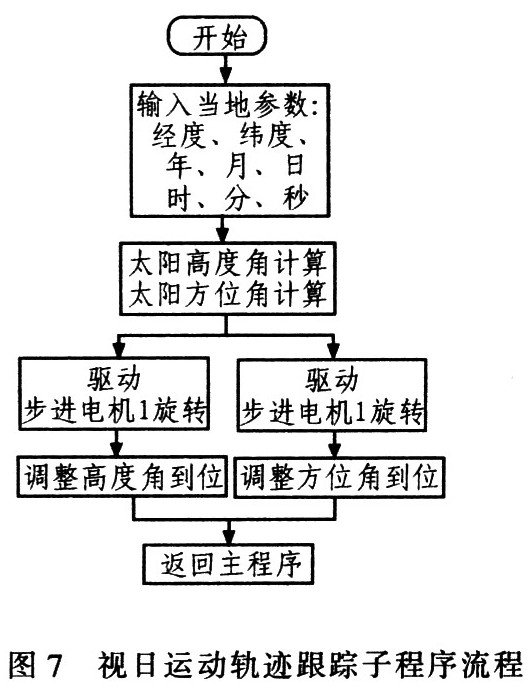

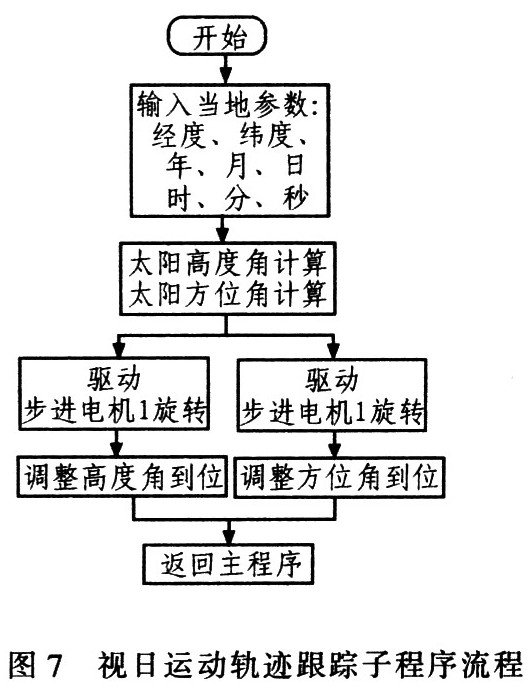

基于ATmega8的双轴太阳跟踪器设计策略

太阳能作为一种清洁能源,倍受人们重视,因此提高太阳能的利用率已成为研究热点。理论分析表明:精确跟踪与非跟踪太

2010-04-23 14:07:01 2606

2606

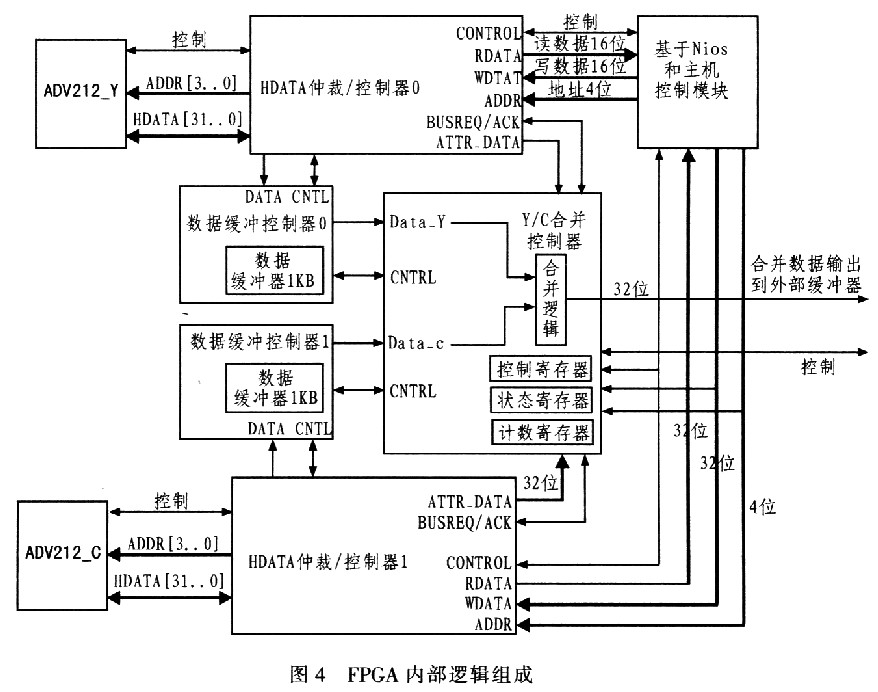

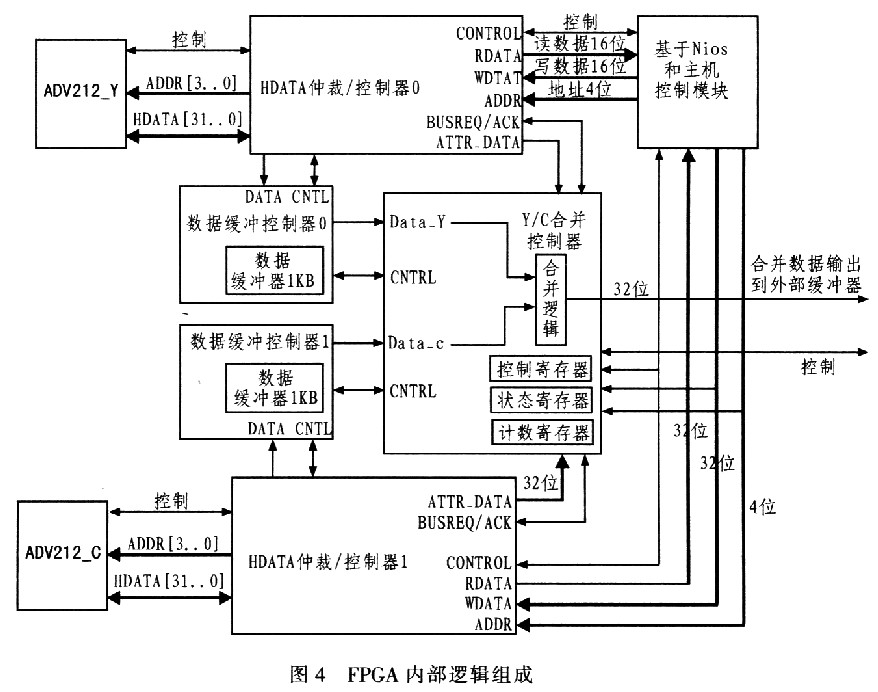

基于ADV212的高清视频压缩系统设计策略

随着社会信息量的增大,人们对多媒体视频压缩的要求越来越高,“高压缩、低比特速率”的高清视频压缩已广泛应用于家用电

2010-04-23 14:15:36 2169

2169

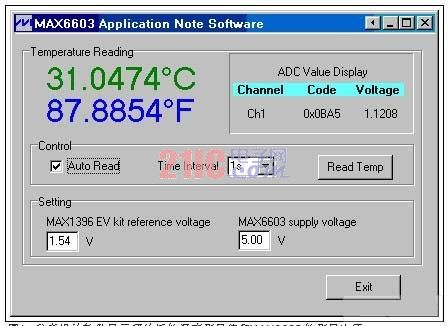

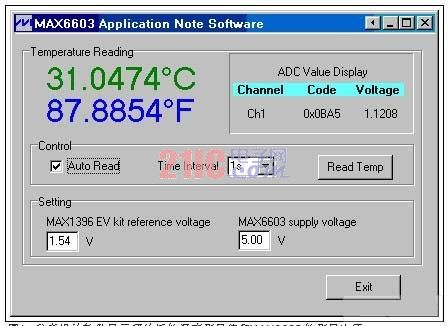

基于PC的温度测量系统参考设计策略

引言

该参考设计提供了一个创建基于PC的温度测量系统的方案,用于*估信号调理器MAX6603。该设计采用两块*估(EV)板:

2010-04-23 14:35:33 791

791

基于嵌入式系统的虚拟仪器的研究与设计策略

以工控计算机和PC为平台的虚拟仪器系统长期以来充当着智能测试系统的平台。随着后PC时代的来临,业界对仪

2010-04-23 14:40:44 1311

1311 安富利“ARM系统设计策略”研讨会亚洲之旅6月28日北京启动,安富利电子元件与ARM通力协作,在亚洲15个城市举办技术培训。

2011-05-12 11:08:10 800

800 安富利全球“ARM系统设计策略”研讨会亚洲之旅日前正式在北京国际会议中心拉开帷幕,共有1000名业内人士参加了此次研讨会,场面盛大,与会者反响热烈,彰显了业界对针对ARM系统的

2011-06-30 08:59:55 612

612 分析了变频调速异步电动机的工作状态和在电机设计中需要考虑的特殊点,提出了变频调速异步电动机的设计策略

2011-08-26 14:24:28 49

49 在FPGA设计中,为了成功地操作,可靠的时钟是非常关键的。设计不良的时钟在极限的温度、电压下将导致错误的行为。在设计PLD/FPGA时通常采用如下四种类型时钟:全局时钟、门控时钟

2011-09-21 18:38:58 3472

3472

基于AD9540产生多时钟输出

2011-11-25 00:02:00 31

31 FPGA 异步时钟设计中如何避免亚稳态的产生是一个必须考虑的问题。本文介绍了FPGA 异步时钟设计中容易产生的亚稳态现象及其可能造成的危害,同时根据实践经验给出了解决这些问题的

2011-12-20 17:08:35 63

63 2014-06-20 10:30:15 21

21 DLL在_FPGA时钟设计中的应用,主要说明DLL的原理,在Xilinx FPGA中是怎么实现的。

2015-10-28 14:25:42 1

1 FPGA学习资料,有兴趣的同学可以下载看看。

2016-04-07 16:33:47 0

0 基于改进模糊卡尔曼滤波的感应电机转速估计策略研究_王鑫博

2017-01-08 11:20:20 1

1 如何正确使用FPGA的时钟资源

2017-01-18 20:39:13 22

22 目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动提出了更高的要求。为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驱动设计的主时钟,以达到最低的时钟抖动和延迟。

2017-02-11 11:34:11 4223

4223 在一个SOC设计中,存在多个、独立的时钟,这已经是一件很平常的事情了。大多数的SOC器件都具有很多个接口,各个接口标准都可能会使用完全不同的时钟频率。

2017-02-11 15:07:11 1047

1047 很大。 在设计PLD/FPGA时通常采用几种时钟类型。时钟可分为如下四种类型:全局时钟、门控时钟、多级逻辑时钟和波动式时钟。多时钟系统能够包括上述四种时钟类型的任意组合。

2017-11-25 09:16:01 3907

3907

基于FPGA的数字系统设计中大都推荐采用同步时序的设计,也就是单时钟系统。但是实际的工程中,纯粹单时钟系统设计的情况很少,特别是设计模块与外围芯片的通信中,跨时钟域的情况经常不可避免。如果对跨时钟

2018-09-01 08:29:21 5302

5302

跨时钟域问题(CDC,Clock Domain Crossing )是多时钟设计中的常见现象。在FPGA领域,互动的异步时钟域的数量急剧增加。通常不止数百个,而是超过一千个时钟域。

2019-08-19 14:52:58 2854

2854 时钟是FPGA设计中最重要的信号,FPGA系统内大部分器件的动作都是在时钟的上升沿或者下降沿进行。

2019-09-20 15:10:18 5065

5065

有一个有趣的现象,众多数字设计特别是与FPGA设计相关的教科书都特别强调整个设计最好采用唯一的时钟域。

2020-09-24 10:20:00 2487

2487

利用 FPGA 实现大型设计时,可能需要FPGA 具有以多个时钟运行的多重数据通路,这种多时钟FPGA 设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数据关系。设计过程中最重要的一步是确定要用多少个不同的时钟,以及如何进行布线,本文将对这些设计策略深入阐述。

2021-01-13 17:00:00 11

11 利用 FPGA 实现大型设计时,可能需要FPGA 具有以多个时钟运行的多重数据通路,这种多时钟FPGA 设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数据关系。设计过程中最重要的一步是确定要用多少个不同的时钟,以及如何进行布线,本文将对这些设计策略深入阐述。

2021-01-15 15:57:00 14

14 AN-769: 基于AD9540产生多时钟输出

2021-03-18 23:03:12 2

2 引言:从本文开始,我们陆续介绍Xilinx 7系列FPGA的时钟资源架构,熟练掌握时钟资源对于FPGA硬件设计工程师及软件设计工程师都非常重要。本章概述7系列FPGA时钟,比较了7系列FPGA时钟

2021-03-22 10:25:27 4326

4326 减少很多与多时钟域有关的问题,但是由于FPGA外各种系统限制,只使用一个时钟常常又不现实。 FPGA时常需要在两个不同时钟频率系统之间交换数据,在系统之间通过多I/O接口接收和发送数据,处理异步信号,以及为带门控时钟的低功耗

2021-05-10 16:51:39 3719

3719

减少很多与多时钟域有关的问题,但是由于FPGA外各种系统限制,只使用一个时钟常常又不现实。FPGA时常需要在两个不同时钟频率系统之间交换数据,在系统之间通过多I/O接口接收和发送数据,处理异步信号,以及为带门控时钟的低功耗

2021-09-23 16:39:54 2763

2763 (29)FPGA原语设计(差分时钟转单端时钟)1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA原语设计(差分时钟转单端时钟)5)结语1.2 FPGA简介FPGA

2021-12-29 19:41:38 5

5 (30)FPGA原语设计(单端时钟转差分时钟)1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA原语设计(单端时钟转差分时钟)5)结语1.2 FPGA简介FPGA

2021-12-29 19:41:48 10

10 xilinx 的 FPGA 时钟结构,7 系列 FPGA 的时钟结构和前面几个系列的时钟结构有了很大的区别,7系列的时钟结构如下图所示。

2022-07-03 17:13:48 2592

2592 本文确定了设计过程、制造过程和应用环境中可能导致 1 ps 或更多时钟偏移的几个关注领域。关于这些关注领域,将提供一些建议、示例和经验法则,以帮助读者直观地了解时钟偏差错误的根本原因和幅度。

2022-07-05 10:17:51 901

901

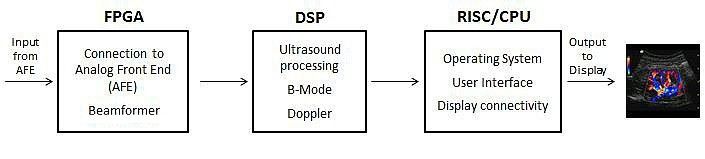

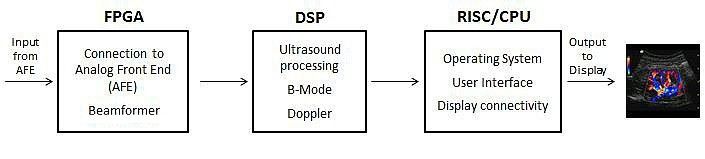

与关注处理器以说明产品其余部分的设计实践类似,终端设备的重点将是便携式医疗成像设备,例如手持式超声设备。与大多数便携式医疗系统相比,这需要更多的处理,但许多设计策略仍然具有相关性。

2022-10-26 15:08:55 801

801

电子发烧友网站提供《大型自调时钟开源分享.zip》资料免费下载

2022-11-01 11:03:32 0

0 大型时钟树通过多个时钟设备、使用多种传输线类型以及跨多个板和同轴电缆路由时钟信号的情况并不少见。即使遵循最佳实践,这些介质中的任何一种都可能引入大于 10 ps 的时钟偏差。但是,在某些应用中,希望

2022-12-22 15:19:31 628

628

减少很多与多时钟域有关的问题,但是由于FPGA外各种系统限制,只使用一个时钟常常又不现实。FPGA时常需要在两个不同时钟频率系统之间交换数据,在系统之间通过多I/O接口接收和发送数据,处理异步信号,以及为带门控时钟的低功耗

2023-08-23 16:10:01 336

336 干货 | 氮化镓GaN驱动器的PCB设计策略概要

2023-09-27 16:13:56 484

484

把握DCM、PLL、PMCD和MMCM知识是稳健可靠的时钟设计策略的基础。赛灵思在其FPGA中提供了丰富的时钟资源,大多数设计人员在他们的FPGA设计中或多或少都会用到。

2023-10-30 11:47:55 523

523

电子发烧友网站提供《大型多GHz时钟树中的相位偏差设计.pdf》资料免费下载

2023-11-22 16:56:01 0

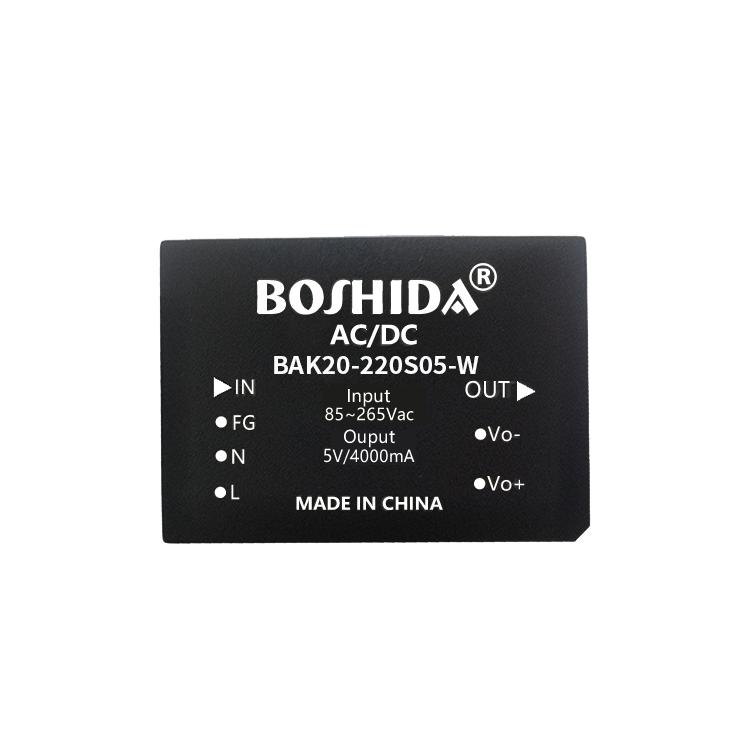

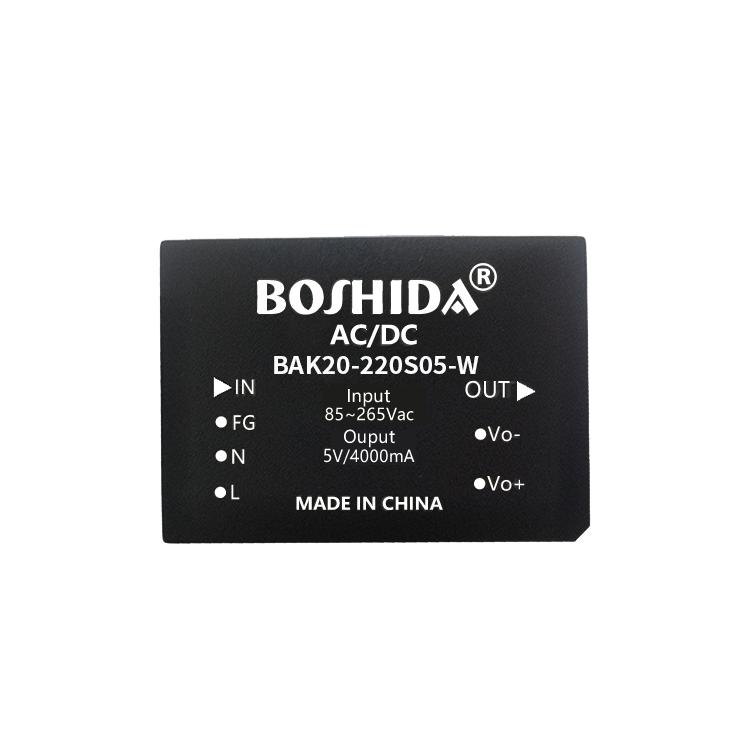

0 BOSHIDA DC电源模块的节能与环保设计策略 DC电源模块的节能与环保设计策略可以从以下几个方面考虑: DC电源模块的节能与环保设计策略 1. 高效率设计:设计高效率的电源转换器可以减少能量损耗

2024-02-18 14:23:17 77

77

正在加载...

电子发烧友App

电子发烧友App

评论