这里将介绍SERDES的基本概念,并介绍SERDES相关的专有名词:眼图(Eye-diagram)、眼图模板、抖动(Jitter)、容忍度(tolerance)、功耗(Power Consumption)、预加重(Pre-emphasis)、均衡(Equalization)、8B/10B编码等。

2018-01-30 08:55:54 22436

22436

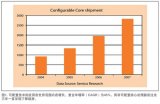

速度最快的SerDes单一通道的带宽已达112Gbps,支持PAM4编码。如此高的速率,使得在整个系统中实现高速信号布线会面临许多许多设计难题。

2020-03-22 15:37:00 3862

3862 Dialog推出了针对12V电机应用的新型可配置混合信号IC(CMIC)SLG47105,该器件提供具有高电压输出的可配置模拟和可配置逻辑,采用2 mm x 3 mm QFN封装。

2020-09-02 16:55:39 3983

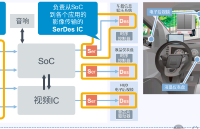

3983 电子发烧友网报道(文/李宁远)SerDes是SERializer串行器和DESerializer解串器的简称,串行器/解串器在发送端将多路低速并行信号被转换成高速串行信号,经过传输媒体,最后在接收

2023-10-12 09:02:14 1624

1624 大家好:

现有6678与一片switch(IDT-cps1848)通信的的情况(6678和1848各一块单板,通过高速接插件相连,已充分做到等长等条件)。6678的参考时钟为156.25MHZ,配置

2018-06-21 02:20:24

串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是独立

2019-05-29 17:52:03

目前我们已经发布了NXP的QorIQLS架构系列的几款平台,包含LS1046A、LS1043A、LS1028A、LS1012A。这几款平台都原生支持网口、PCIE、SATA等高速接口协议,很多

2021-12-20 06:01:37

FPGA发展到今天,SerDes(Serializer-Deserializer)基本上是标配了。从PCI到PCI Express, 从ATA到SATA,从并行ADC接口到JESD204, 从RIO

2021-07-28 07:02:12

SerDes的发送端TX的均衡原理是什么?怎样利用高速接口SerDes去实现芯片间信号的有线传输?

2021-06-17 07:15:16

SERDES结构是怎样构成的?高速SERDES接口在网络方面有哪些应用?

2021-04-28 07:19:38

SerDes/Differential Pair-- The Feature of High Speed Designreference list– reference1:link 应对未来高速

2021-11-12 06:46:26

串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是独立

2019-10-23 07:16:35

Gowin 可配置功能单元(CFU)手册主要描述了可配置功能单元的结构、工作模式和原语。

2022-09-28 08:23:36

我看LS1028的serdes可以配置为2路PCIe3.0x2或1路PCIe3.0x4,请问在哪儿配置,怎么更改配置呢,要改硬件电路吗?没有操作过这个,请版主指点一下,谢谢。

2021-12-31 06:38:27

模式(使用带有 SerDes 协议 0x1133 的 XFI)下运行 PHY。现在我需要在运行时在 1G 和 10G 之间切换。由于我无法在运行时更改 RCW,我尝试重新配置 SerDes 通道,但

2023-04-18 10:32:26

SerDes在93000平台上量产测试。本文将介绍Nautilus UDI方案是如何实现高速SerDes测试的,包括UDI结构,输入时钟设计,Load board设计,socket选型等多个测试环节。

2021-05-10 06:58:55

我想把c6455 srio配置为1P4X的模式,是不是这种模式下只使用一个port,那么我在设置寄存器SERDES_CFGRXn_CNTL和SERDES_CFGTXn_CNTL的时候,只使能

2019-01-21 15:42:20

1#ifndefCONFIG_H_2#defineCONFIG_H_34/*************************************************************************************************/5/****可配置参数...

2021-09-13 09:11:40

摘要针对FFT算法基于FPGA实现可配置的IP核。采用基于流水线结构和快速并行算法实现了蝶形运算和4k点FFT的输入点数、数据位宽、分解基自由配置。使用Verilog语言编写,利用ModelSim

2019-07-03 07:56:53

什么是SerDes?

2021-06-24 07:52:02

数字系统的设计师们面临着许多新的挑战,例如使用采用了串行器/解串器(SERDES)技术的高速串行接口来取代传统的并行总线架构。基于SERDES的设计增加了带宽,减少了信号数量,同时带来了诸如减少布线

2019-05-21 05:00:13

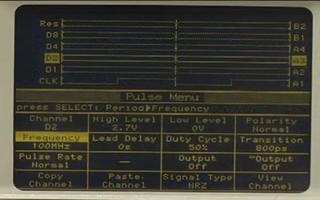

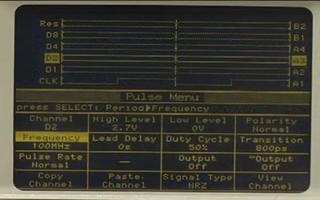

嗨,我想用用户可配置的占空比生成时钟。这意味着用户将实时更改占空比。即没有新的比特流文件。所以我从寄存器定义开始,并配置微控制器。我已经开始为Spartan-6使用PLL_BASE时钟管理组件。我只

2019-06-20 15:02:21

针对高速无线数据通讯的实时性要求,提出采用FPGA来实现可配置均衡器的设计,在设计过程中采用自顶而下划分的设计方式,即方便了设计的需要,同时又满足了性能的要求,在实际项目中收到很好的效果。

2021-04-29 06:48:32

技术所取代,而800G互联技术更已经近在眼前。带宽需求连年暴涨,其底层的高速SerDes技术也因此备受瞩目。 目前,速度最快的SerDes单一通道的带宽已达112Gbps,支持PAM4编码。如此高

2023-04-18 14:52:28

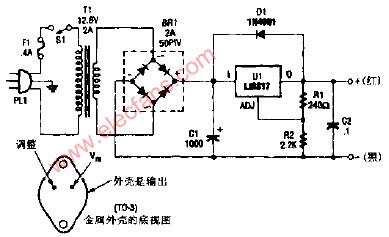

为 EMI 敏感和高速 SERDES 系统供电

2019-05-21 14:34:36

,Artesyn μMP 系列 (MicroMP) 可配置电源支持从 400 W 到 1800 W 的功率需求。 µMP 系列的成本与非可配置电源相当,同时还具有市场领先的密度、效率和可靠性。图 4

2017-04-07 15:06:26

赛灵思 Artix-7 FPGA 是业界唯一的在低端器件上整合了高速收发器的方案,该方案提供了自适应均衡、2D 眼图以及IBIS-AMI仿真模型来简化针对成本敏感型应用的高速串行设计,观看视频,4分钟教您搞定高速SerDes端口设计。

2016-07-27 17:29:59

请教:C6678的PCIE SRIO Hyperlink和SGMII模块的配置中都涉及到对serdes模块的配置,故希望知道以下几个问题:1、这些模块的serdes是同一个,还是各自有各自

2018-08-06 06:17:36

6678中的srio的serdes和以太网的serdes是共用还是各自有自己的serdes?

2018-08-02 06:11:31

STM8可配置时钟输出寄存器

2020-11-10 08:03:29

对于单个SERDES Quad(示例quad 223),我可以为所有四个通道以10 Gbps运行TX,以及以2.5 Gbps(10G / 4)运行4个接收通道吗?我可以在10 Gbps的四核中运行一个serdes,在同一个quad中以2.5 Gbps(10G / 4)运行第二个serdes吗?

2020-04-30 09:15:53

请问超高速SerDes在芯片设计中的挑战是什么?

2021-06-17 08:49:37

的性能比以往的机架式仪器的性能要好。”Aeroflex 测试解决方案部门PXI产品经理Tim Carey指出,“Aeroflex 3000 系列模块化平台具有灵活、高速的特点,这为可配置仪器制定了一个新基准,为用户带来超乎想象的自由度。”

2019-06-28 06:39:18

(PCI Express root complex)标识,不可以配置冲突,举例说SerDes1配置为1163,SerDes2配置为5559,这是不可以的!因为PCIe.1重复了。PCIe.nx4表示4条

2020-10-28 17:15:14

是RC(PCI Express root complex)标识,不可以配置冲突,举例说SerDes1配置为1163,SerDes2配置为5559,这是不可以的!因为PCIe.1重复了。PCIe.nx4

2020-11-01 20:21:02

电路Bandgap/LDO/OSC/PLL/Serdes等的设计和仿真;3. 负责与版图工程师沟通并完成电路的版图设计;4. 制定芯片的测试计划,并在流片后配合芯片测试;5. 负责芯片设计过程中相关

2017-11-13 14:46:14

本文简要介绍了SoC 设计链面临的挑战以及对可配置IP 提出的新的要求。重点分析了如何利用Improv 系统公司开发的VLIW架构和包括Jazz DSP 平台的工具套件进行快速、低成本、高性能的

2009-12-14 10:25:55 14

14 串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。随着系统的带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初

2010-02-25 23:03:44 38

38 一种高速可配置实时总线的开发及其应用:为满足工业生产中对现场总线柔性可重构以及高速实时传输要求,讨论了一种可在线配置高速实时总线的设计与实现.本研究通过对SP

2010-03-18 15:56:36 20

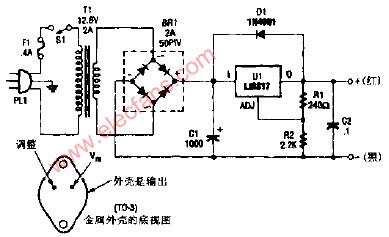

20 可配置电源

如果有必要的话,此可调

2009-09-30 12:07:59 703

703

基于可配置处理器的嵌入式系统ESL设计需求

近年来,越来越多的嵌入式系统和SoC开始转向使用可配置处理器技术,这样既可以缩短产品开发周期,又可使设计更加灵活,

2010-01-14 09:41:51 735

735 Maxim推出6通道闪存可配置的排序器/监测器

Maxim推出闪存可配置的排序器/监测器MAX16067/MAX16068,可简化电源管理和故障诊断。这两款器件集成±1%精度的ADC,用于在要求高

2010-03-05 10:35:32 443

443 可配置振荡器,可配置振荡器结构原理是什么?

可配置振荡器既具备可编程振荡器交付时间短的优势,又避免了其噪声高的缺陷,其内部结构如图2

2010-03-22 14:34:20 769

769 非易失性存储器的可配置性

随着消费者要求新产品定期增加功能或提高应用灵活性,开发人员对修改系统应用功能的快捷性和简便性要求越来越高

2010-05-12 09:56:06 843

843

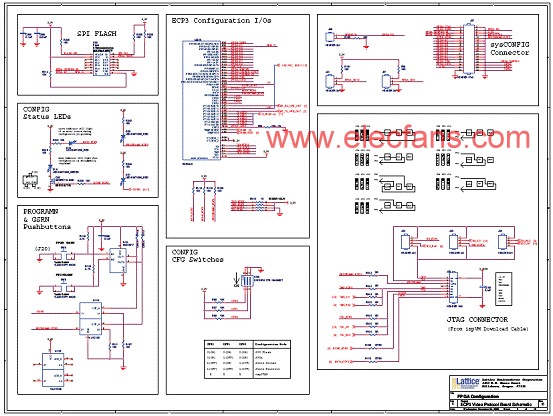

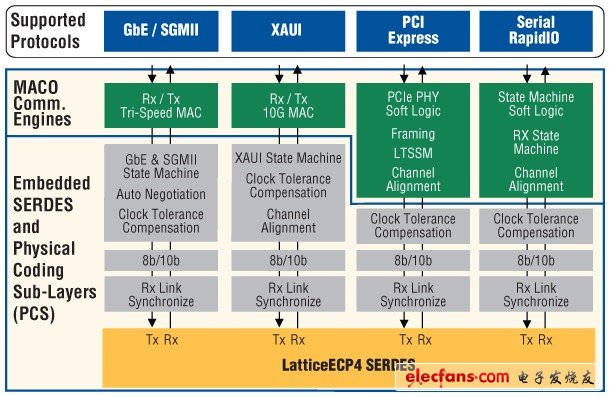

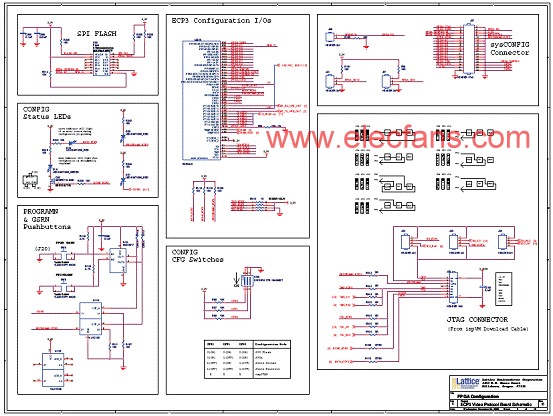

本文介绍了LatticeECP3 FPGA系列主要特性,LatticeECP3-35简化方框图以及LatticeECP3视频协议板主要特性,方框图和详细的电路图。

Lattice 公司的LatticeECP3 FPGA系列能提供高性能的特性

2010-10-15 15:09:04 2457

2457

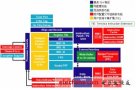

LatticeECP3系列是来自莱迪思半导体公司的第三代高价值的FPGA,在业界拥有SERDES功能的FPGA器件中,它具有最低的功耗和价格

2011-03-23 10:41:36 981

981 Xtensa可配置处理器架构是可配置可扩展的微处理器技术,可以用于片上系统SOC设计。现在的SOC需要更高系统性能、更高输入/输出带宽和更高功耗利用率

2011-04-19 11:51:16 1737

1737

莱迪思半导体公司(NASDAQ: LSCC)今天用宣布推出下一代LatticeECP4™FPGA系列,由其重新定义了低成本,低功耗的中档FPGA市场

2011-12-02 09:02:59 681

681 致力于中端和低密度FPGA产品开发的莱迪思半导体公司日前再推力作下一代LatticeECP4 FPGA系列。其具有6Gbps的SERDES、采用低成本wire-bond封装、功能强大的DSP块和具有基于硬IP的通信引擎,适

2011-12-14 09:58:45 1362

1362 莱迪思半导体公司日前宣布,即可获取增加至非常成功的LatticeECP3 FPGA系列的低功耗、高速和迷你封装器件。

2012-02-03 09:25:38 521

521 莱迪思半导体公司(NASDAQ: LSCC)近日宣布,即可获取增加至非常成功的LatticeECP3™FPGA系列的低功耗、高速和迷你封装器件。

2012-02-04 09:59:34 783

783 LatticeECP4 系列:具有高级通信引擎和强大的 DSP 模块的低成本、低功耗 FPGA 新的LatticeECP4系列是第四代具有高级通信引擎和功能强大的DSP模块的高可靠、低成本、低功耗FPGA。创新的Latt

2012-06-06 09:51:38 1924

1924 一种密钥可配置的DES加密算法的FPGA实现

2016-05-11 11:30:19 11

11 一种可配置的老化预测传感器设计_梁华国

2017-01-07 16:06:32 0

0 传统上,系统级芯片(SoC)设计师必须应对刚性的非可配置核心技术。众所周知,传统的核心工艺在设计或制造过程中是不可配置的,并且不能按多种用途进行定制。

2018-02-08 20:33:58 1324

1324

看看LatticeECP3 FPGA的功耗是多么的低,无论是在实验室中测量,还是利用莱迪思的功耗计算器软件计算。 LatticeECP3是业界最低功耗的配备SERDES的FPGA。

2018-06-15 13:36:00 4990

4990

三步E5可配置片上系统集成在单个设备上,集成了性能增强的加速8051嵌入式微控制器、大块SRAM、高速专用系统总线和可配置逻辑,与处理器和系统总线紧密相连。E5系列是一个高度集成的、完全静态的用于

2018-10-10 08:00:00 4

4 关键词:AMC , ECP3 , FPGA Lattice公司的LatticeECP3 FPGA系列可提供高性能特性如增强的DSP架构,高速SERDES和高速源同步接口。LatticeECP3采用

2019-02-13 17:37:01 563

563 关键词:Lattice , LVDS视频接口 Lattice公司的LatticeECP2 7:1 LVDS视频评估套件采用LatticeECP2 或LatticeXP2 FPGA

2019-03-20 12:50:01 956

956 随着通信技术的飞速发展,高速数据传输系统成为了当前研究的热点,而高速 SERDES 接口芯片的研究则是其中一个重要的组成部分。SERDES 接口芯片的主要功能是将低速的并行信号转换成为高速低压差分信号(LVDS)并通过串行链路发送,同时能够接收串行输入 LVDS 数据并正确的转换为低速并行信号。

2019-06-24 08:00:00 12

12 LatticeECP3 (经济型加第三代)FPGA设备系列经过优化,以在经济的FPGA结构中提供高性能功能,如增强的DSP架构、高速SERDES和高速源同步接口。这种结合是通过器件结构的进步

2020-11-20 08:00:00 0

0 为 EMI 敏感和高速 SERDES 系统供电

2021-03-19 04:23:54 12

12 AD74412R:四通道可配置输入/输出数据表

2021-04-22 15:27:55 2

2 6B21:隔离式现场可配置模拟输入数据表

2021-04-26 12:42:52 0

0 可配置的7通道大功率PMIC

2021-05-08 10:46:21 1

1 带按钮控制的可配置唤醒定时器

2021-05-16 13:40:34 8

8 SerDes/Differential Pair-- The Feature of High Speed Designreference list– reference1:link 应对未来高速

2021-11-07 10:21:00 47

47 电子发烧友网站提供《以STM32为核心的光电隔离可配置多IO板.zip》资料免费下载

2022-07-26 10:23:35 3

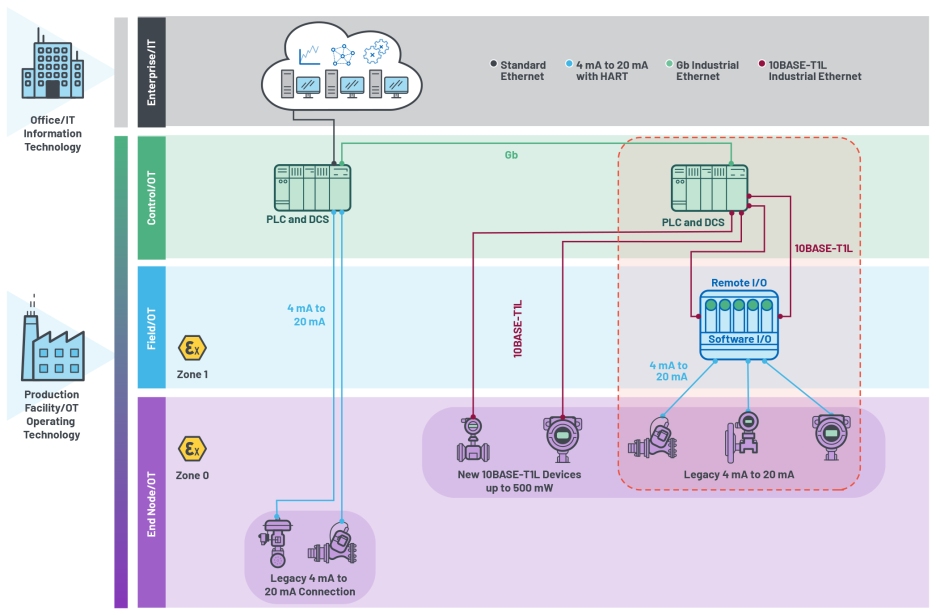

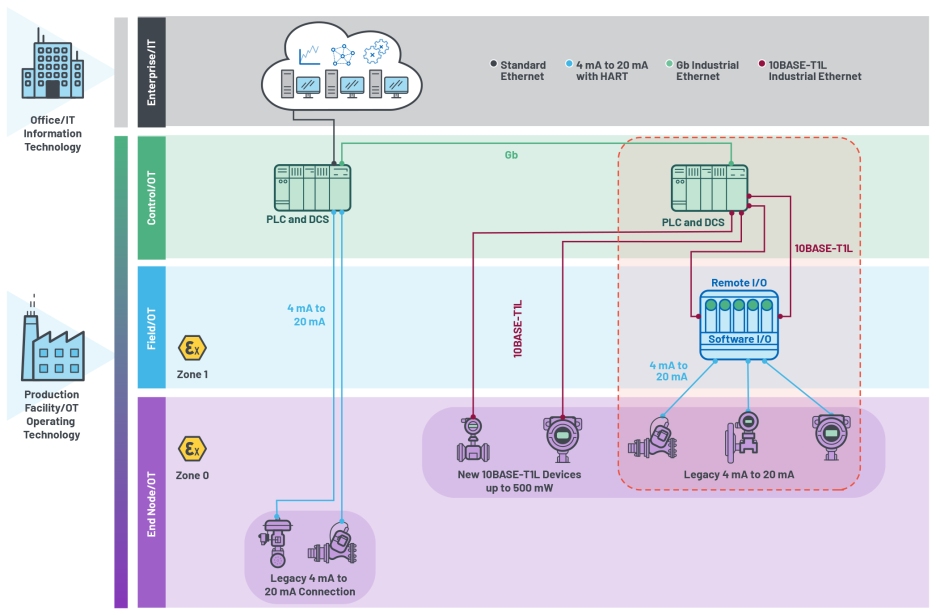

3 软件可配置 I/O 系统提供从传统模拟信号到工业以太网域的无缝过渡。

2022-08-12 15:37:07 374

374

可配置 AFE 改变电力线通信未来

2022-11-04 09:52:20 0

0 低功耗可配置多功能门-74AUP1G97

2023-02-07 19:00:05 0

0 低功耗可配置多功能门-74LVC1G98

2023-02-07 20:11:16 0

0 双电源可配置多功能门-74AXP1T57

2023-02-09 19:24:49 0

0 低功耗可配置多功能门-74AXP1G97

2023-02-10 18:42:39 0

0 低功耗可配置多功能门-74AUP1G58

2023-02-10 19:10:20 0

0 低功耗可配置多功能门-74LVC1G57

2023-02-10 19:15:12 0

0 低功耗可配置多功能门-74LVC1G58

2023-02-10 19:15:37 0

0 低功耗可配置多功能门-74AUP1G98

2023-02-14 18:42:40 0

0 低功耗可配置多功能门-74LVC1G97

2023-02-14 18:44:37 0

0 低功耗可配置多功能门-74AUP1G57

2023-02-14 18:45:09 0

0 低功耗可配置多功能门-74AXP1G58

2023-02-15 19:09:39 0

0 低功耗可配置多功能门-74AXP1G57

2023-02-15 19:09:53 0

0 超可配置的多功能门;三态-74LVC1G99

2023-02-20 19:45:09 0

0 低功耗可配置多功能门-74AXP1G98

2023-03-03 19:28:36 0

0 同时介绍一种采用光电集成技术的,即采用光SerDes而非电SerDes的高速收发器。

2023-04-01 09:28:58 1078

1078 首先我们要了解什么是SerDes,SerDes的应用场景又是什么呢?SerDes又有哪些常见的种类?

2023-06-06 17:03:55 4707

4707

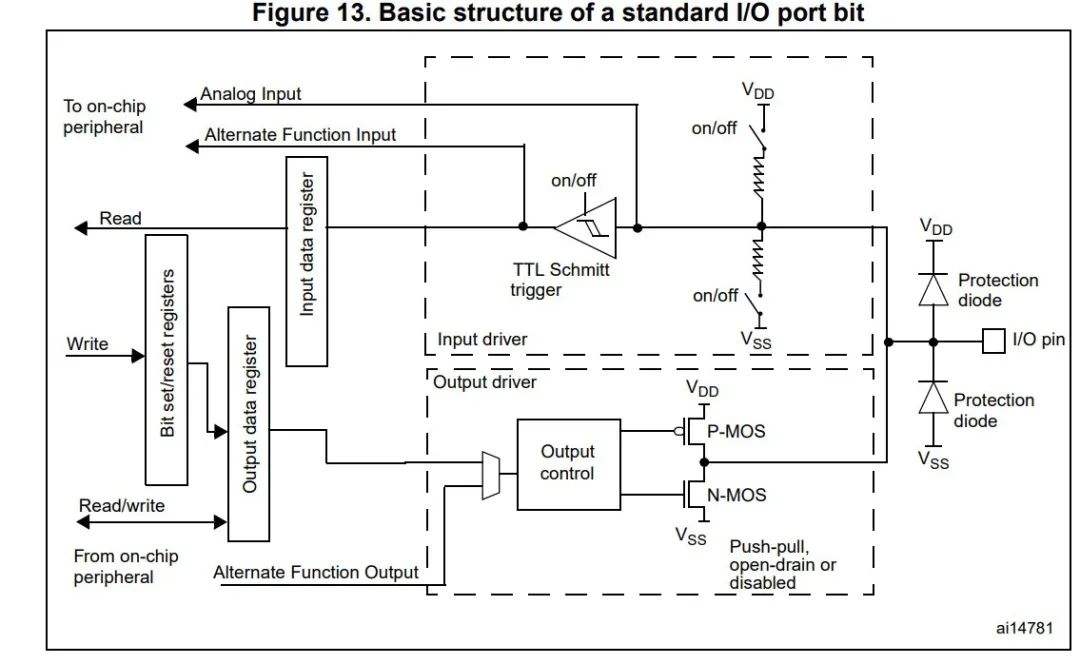

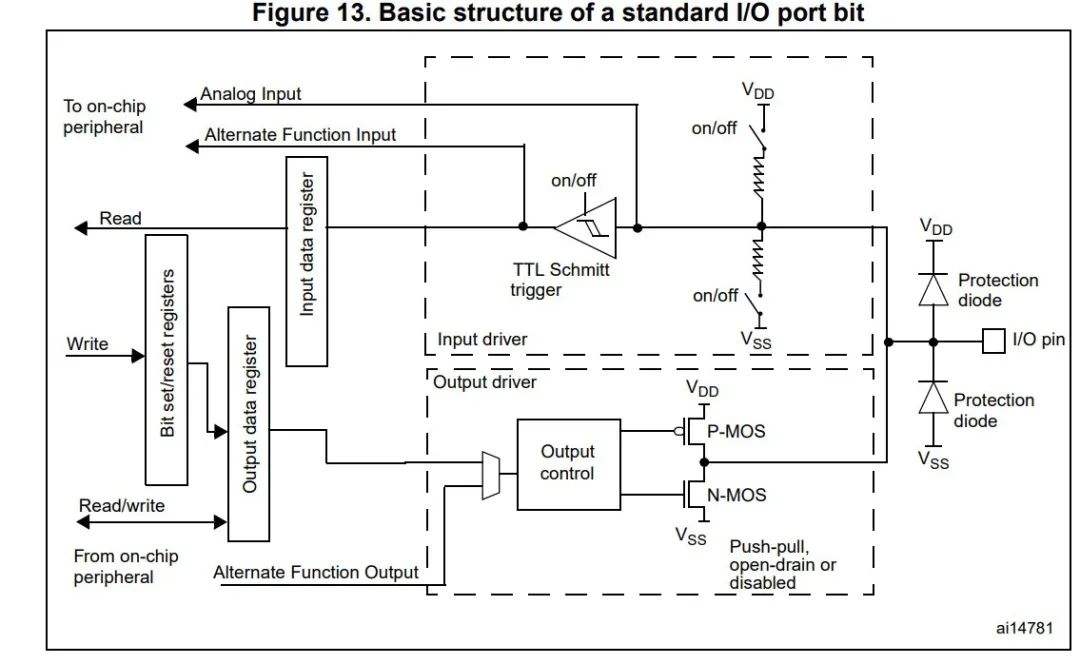

GPIO可配置为三种模式:Output模式、Input模式和Analog模式

2023-07-24 11:27:07 2204

2204

FPGA发展到今天,SerDes(Serializer-Deserializer)基本上是器件的标配了。从PCI发展到PCI-E,从ATA发展到SATA,从并行ADC接口到JESD204,从RIO

2023-10-16 14:50:37 558

558

SerDes,即Serializer(串行器)和Deserializer(解串器)的简称,是一种高速串行数据传输技术。

2024-03-12 14:05:27 592

592

正在加载...

电子发烧友App

电子发烧友App

评论