随着工艺技术的发展与市场需求,超大规模、高速、低功耗的新型现场可编程逻辑器件(FPGA)不断推出,给电路设计带来极大的方便。在采用大规模FPGA的开发系统中,供电模块的设计将直接影响到系统的稳定性,因此设计出高效、稳定的供电模块显得尤为重要。本文以可扩展网络交换调度系统的FPGA验证平台为例,介绍FPGA供电模块的设计方法。

目前,FPGA、DSP等芯片的电源供电方案主要有三种:低压差线性稳压器(LDO)、电源模块和开关稳压电源。其中采用集成FET的称为DC/DC调整器,采用非集成FET的称为DC/DC控制器。

LDO的基本原理是根据负载电阻的变化情况调节自身的内阻,从而保证稳压器输出端的电压不变,因此LDO只适用于降压变换。其具体效果与输入/输出电压比有关,变换效率可以简单地看作输出与输入电压之比。由于采用线性调节原理,瞬态特性好。LDO本质上没有输出纹波,但随着LDO的输入/输出电压差别增大或者输出电流增加,LDO的发热比会成比例增大,所以在散热控制方面要求很高。LDO稳压器为电流输出要求较低的应用提供了体积小且廉价的解决方案。

DC/DC调整器利用了磁场储能,无论升压、降压或是两者同时进行,都可以实现相当高的变换效率。由于变换效率高,因此发热很小,散热处理得以简化,所以DC/DC调整器一般不再需要附加一个成本较高、面积较大的散热器。考虑到DC/DC调整器集成有FET,使用时只需外接一个电感和必不可少的输入电容和输出电容,故可以使整个解决方案的空间利用率大大提高,尤其对于需要大电流的FPGA来说十分理想。由于是开关稳压器电源,与LDO相比,DC/DC调整器输出纹波电压较大、瞬时恢复时间较慢、容易产生电磁干扰(EMI)。要取得低纹波、低EMI、低噪声的电源,关键在于电路设计,尤其是输入/输出电容、输出电感的选择和布局。DC/DC调整器占用面积较大。

DC/DC控制器和DC/DC调整器的差别主要是没有内置的FET。因此,设计者可以选用有特定导通电阻的外接FET晶体管,并根据应用的需要调整电流,使设计具有很大的灵活性,这在需要十几甚至几十安培电流的特大规模FPGA开发系统中非常有用。与DC/DC调整器相比,采用这种方案设计,既要选择适当的输入电容/输出电容、输出电感,又要选择符合要求的FET,增加了设计难度和总成本。此外,由于FET外置,占用空间也相对较大。

电源模块从原理上来说是个开关稳压器,所以它的效率非常高。相对于普通开关稳压器,它的集成度更高,因此外围只需要一个输入电容和一个输出电容即可工作,设计简便,适合要求开发周期非常短的应用。它一般以可插拔的形式给出。由于电源模块上集成了几乎所有可以集成的东西,灵活性相对较差,价格也相对较高。

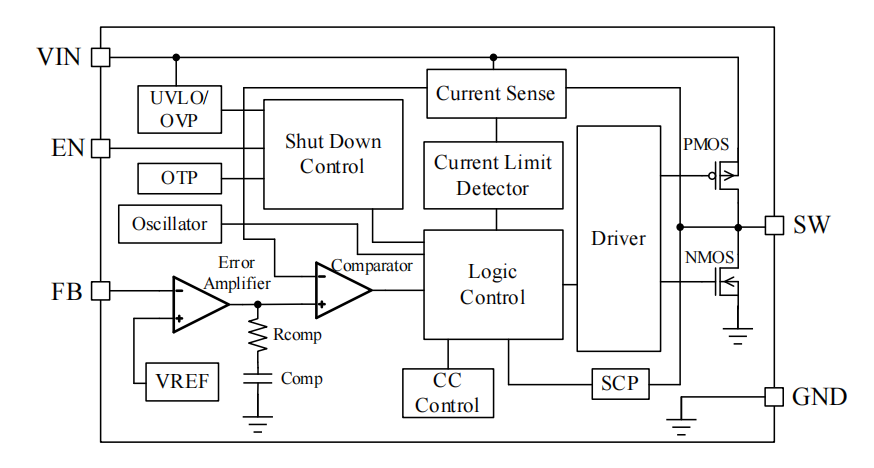

1 器件选型与功能介绍

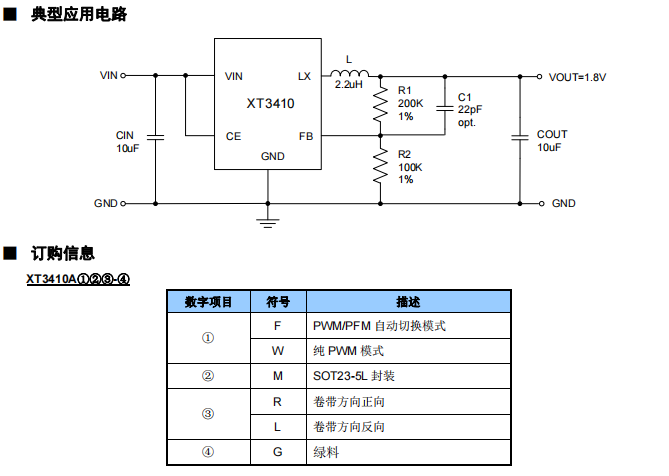

本文中的交换调度系统的FPGA验证平台采用4片Xilinx VirtexII FPGA作为网络包调度器实现可扩展的交换调度功能,其中VirtexII的核心电压VCCINT为1.5V,辅助电压VCCAUX和输出驱动电压VCCO均为3.3V。由于需要对4片FPGA供电,电源板面积较大。为了调试方便,对整个供电电路采用单独设计制板,根据器件和系统的要求,本设计采用DC/DC调整器方案。

采用DC/DC调整器的供电方案虽然有多种,但考虑到每个供电模块需要对两片FPGA供电,而且通过仿真估算出的每片FPGA的最大电流为2A左右,加上一定的裕量,因此需要单个供电模块最大能够提供6A左右的电流。

TPS54610是TI公司专门为DSP、ASIC和FPGA等多芯片系统供电而设计的一款低电压输入、大电流输出的同步降压DC/DC调整器,内含30MΩ、12A峰值电流的MOSFET开关管,最大可输出6A电流。输出电压从0.9V到3.3V可调,误差率为1%。开关频率可固定在350kHz或550kHz,也可以在280kHz到700kHz之间调整。另外,它还具有限流电路、低压闭锁电路和过热关断电路。而且TPS54610的集成化设计又减少了元件数量和体积,因此,可广泛用于低电压输入、大电流输出的分散电源系统中。经过分析,采用两片TPS54610为两片FPGA供电的方案。

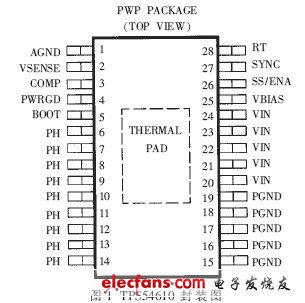

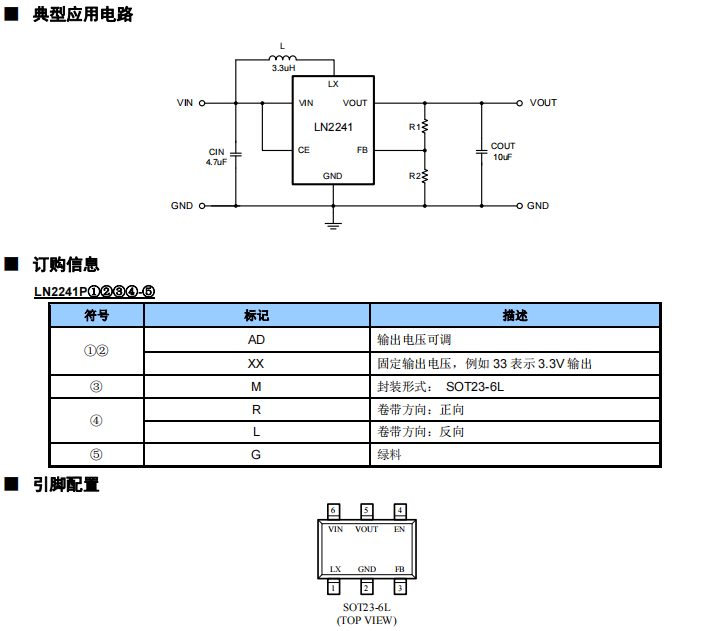

TPS54610采用28脚TSSOP封装,其引脚排列如图1所示。各引脚功能如下:

·AGND(1脚):模拟地。

·VSENSE(2脚):误差放大反馈输入,通过补偿网络/输出分压器连接输出电压。

·COMP(3脚):误差放大器输出,COMP脚与VSENSE脚间应接频率补偿电路。

·PWRGD(4脚):当VSENSE端的电压高于Vref的90%时,输出为高,否则为低。

·BOOT(5脚):自举电路输出,在BOOT脚和PH脚之间应连接0.022μF~0.1μF的电容。

·PH(6~14脚):相输出,功率MOSFET高低端与输出电感的连接点。

·PGND(15~19脚):电源地,使用时应与AGND单点连接。

·VIN(20~24脚):电源输入,与PGND间应连接10μF的电容。

·VBIAS(25脚):内部偏压调节,与AGND引脚间应接一个0.1μF~1μF的陶瓷电容。

·SS/ENA(26脚):软启动/输入输出使能端,可提供控制器允许工作逻辑信号。 该脚的另一个功能是通过外接电容设置软启动时间。

·SYNC(27脚):同步输入,可提供外部振荡器同步逻辑信号,此时要求RT引脚必须连接一个电阻,在内部振荡时用于开关频率的切换。

·RT(28脚):频率设置电阻输入,在RT和AGND间连接一个电阻可以设置开关频率, 当使用SYNC端时, 通过RT设置的频率应稍低于外部振荡器的频率。

2 电路设计

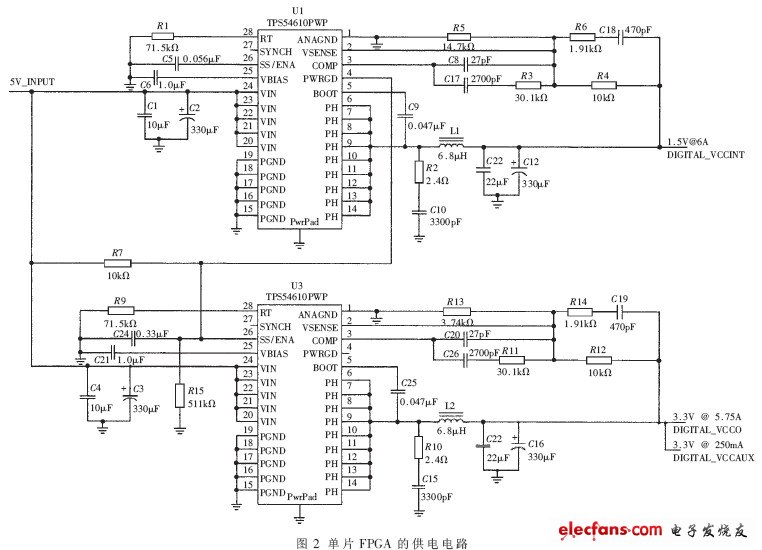

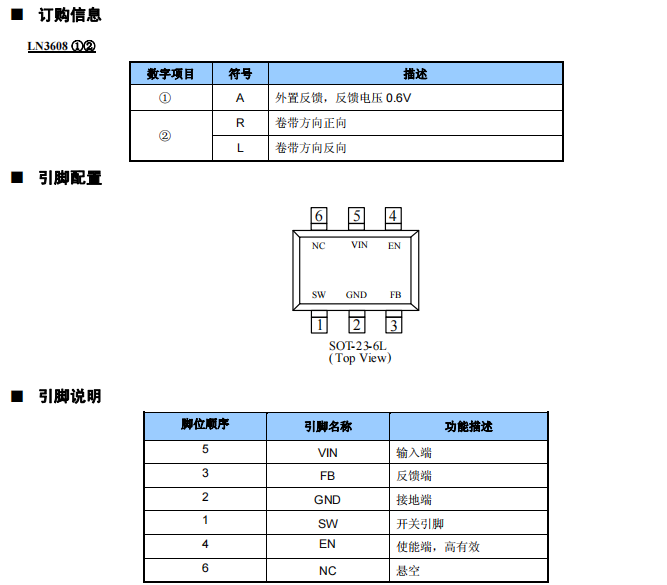

图2所示为两片FPGA的供电电路,其中的一片TPS54610提供两片FPGA的VCCINT电压,另一片TPS54610给两片FPGA的VCCAUX和VCCO供电。设计该电路时主要应考虑输入输出滤波、反馈电路以及开关频率的选择等方面。

2.1 输入输出滤波

电路的输入为5V直源电源,输入滤波电容C2(C3)为330μF,可减少输入波纹电压。输入旁路电容C1(C4)为10μF,可有效地去除输入电压中的高频分量,这几个电容制版时都要尽可能靠近芯片。输出滤波网络由6.8μH的电感L1(L2)与22μF的电容C11(C22)和330μF的电容C12(C16)组成。

2.2 补偿网络

图2中的R4、R5组成的分压网络使输出的VCCINT电压为1.5V,R12、R13组成的分压网络使输出的VCCO电压为3.3V。R4(R12)、R3(R11)、R6(R14)、C8(C20)、C17(C26)与C18(C19)形成了电路的环路补偿网络。这些元器件的选取方法很多,本设计中主要考虑其稳定性和较宽的带宽。补偿电路的设计首先应考虑补偿误差放大器的增益不被限制。其次,补偿误差放大器应将COMP引脚的波纹电压降到100mV左右。另外,电路总的回路串扰频率应小于开关频率的1/8,同时相角裕量至少应为45°。通过图中补偿元件的参数设计可将总的回路响应串扰频率范围限制在10kHz~70kHz之间,相位裕量范围设定在60°~90°之间,同时图中各电阻的偏差应小于1%,电容偏差应小于10%。

2.3 开关频率的选择

TPS54610的开关频率在280kHz~700kHz之间是可调节的。当SYNC引脚接地时,开关频率为350kHz,当SYNC接输入电源电压时,开关频率为550kHz。当RT和AGND之间接180kΩ~68kΩ的电阻时,可以在280kHz~700kHz之间调节开关频率,其中电阻R的计算公式为 ,这时,SYNCH脚应断开。开关频率的选择要考虑转换效率和元件尺寸,较高的工作频率允许使用较低数值的电感和电容,反之,则因减少了内部开关损失而提高效率,但需较大的电感和电容以降低输出纹波。本设计将开关频率选定为最高的700kHz,此时,通过计算可得R1为71.5kΩ。

偏置电容C6和C21采用1.0μF的陶瓷电容,连接到VBIAS脚和AGND脚之间,自举电容C9和C25采用0.047μF的陶瓷电容,连接到BOOT脚和PH脚之间。2.4 软启动及系统使能

SS/ENA脚有两个功能:一是作为使能信号控制芯片的关闭或启动,启动阈值电压大约为1.2V。缺省时,芯片处于关闭状态,直到SS/ENA的电压超过阈值电压时,芯片开始启动。TPS54610内部慢启动时间为3.35ms,反馈到误差放大器的基准电压在3.35ms内从0V线性上升到0.891V,同样地,芯片的输出电压在3.35ms内上升到稳定值。

另一个功能是通过与AGND脚之间连接的一个小电容Css设置启动时延td及软启动时间tss。其中,启动时延td的大小与Css的大小是成比例的,即td=Css×1.2V/5μA,软启动时间即输出电压的上升时间tss的调整是通过公式 tss=Css×0.7V/5μA进行的。

因此,在为VCCINT供电的TPS54610芯片的SS/ENA脚外接一个0.056μF的电容C5,为VCCAUX和VCCO供电的TPS54610芯片的SS/ENA脚接0.33μF的C24后,外加5V电压时,0.013ms后为VCCINT供电的TPS54610芯片开始启动,经过0.0078ms后,输出VCCINT稳定为1.5V。此时,PWRGD引脚输出为高电平,为VCCAUX和VCCO供电的TPS54610芯片SS/ENA脚为高电平,0.079ms后该芯片开始启动,经过0.046ms后,VCCAUX和VCCO的输出达到稳定的3.3V。当VCCINT输出的电压低于1.35V(即正常值的90%)时,PWRGD脚输出为低电平,使得为VCCAUX和VCCO供电的TPS54610芯片的SS/ENA脚为低电平,此时芯片关闭,VCCAUX和VCCO输出为0。

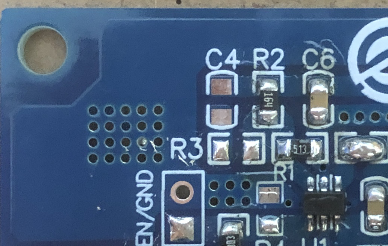

3 PCB设计

该电路的PCB设计采用双层板设计。首先进行整体布局,布局时要考虑PCB的形状和尺寸。通常,电路板的最佳形状为矩形,PCB尺寸过大时,印制线条长,阻抗增加,抗噪声能力下降,成本也增加;而PCB尺寸过小时,散热不好,且邻近线条易受干扰。由于设计的PCB板上有由4片TPS54610 和2片TPS79425组成的两个供电单元,根据芯片尺寸,本次设计的尺寸为149.8mm×70.47mm。

确定了PCB的尺寸后,先要确定特殊元件的位置,再根据电路的功能单元,对电路中的全部元器件进行布局。其中,需注意以下几点:①易受干扰的元器件不能相互挨得太近,输入和输出元件应尽量远离,热敏元件应远离发热元件;②对于电位器、可调电感线圈、可变电容器、微动开关等可调元件应放在印制板上方便于调节的地方;③应留出印制板定位孔及固定支架所占用的位置。在本设计中,输入的+5V电压源插座位于板子的上方,输出插座位于板子的左右两侧,两个供电单元呈中心对称分布,距离适当。布局时需要对所选用元件器及各种插座的规格、尺寸、面积等有完全的了解,对各部件的位置安排作合理、仔细考虑,主要应从电磁场兼容性、抗干扰、走线短、交叉少、电源和地的路径及去耦等方面考虑。位于电路板边缘的元器件与电路板边缘距离一般不小于2mm。

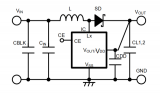

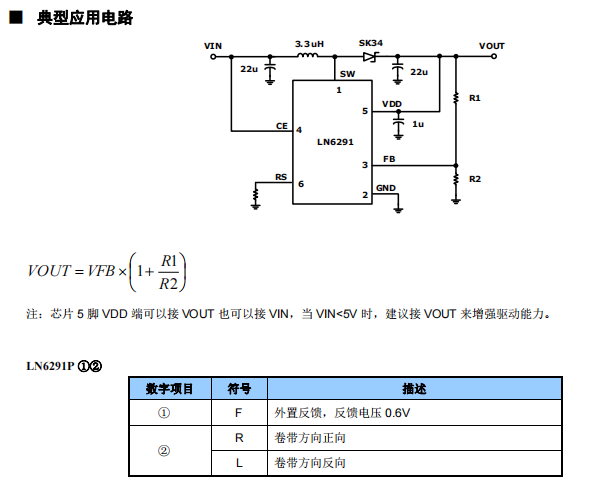

图3所示为TPS54610的PCB线路连接模型。可以看到,输入电压脚VIN都连在一起,通过输入旁路电容C1与PGND(电源地)相连,C1为低等效串联电阻陶瓷电容。为了减少噪声的影响,PCB设计时C1、C2应尽可能靠近VIN和PGND脚。

TPS54610有两个地,即电源地PGND和模拟地AGND。电源地连接嘈杂的功率信号,模拟地连接所有噪声敏感信号。两个地之间一旦注入噪声就会降低TPS54610的性能,还会引起控制信号和偏置出现问题,尤其在高速电路中表现得尤为明显。因此,通常将电源地与模拟地分开布线,并在一点上相连。用一个单独的比较宽的导线作为模拟地,它连接频率设置电阻R1,慢启动电容C3和偏置电容C4的接地端,并与TPS54610的AGND脚相连。

为了解决TPS54610芯片的散热问题,在其底面有一块暴露的PowerPAD区(见图3中的PowerPAD),制作PCB板时应将它与顶层地相接并用过孔将顶层地与PCB的地相连。过孔还可以用在输入和输出滤波电容的接地端。直接连接到电源地上的器件只有输入滤波电容和旁路电容、输出滤波电容和PGND脚。

PH脚与输出电感L1相连,由于连接电路是开关节点,所以L1要尽可能地靠近PH脚。另外,PH脚连接在一起的区域要尽可能小以防止过多的电容耦合。从图中可以看到,PH脚通过C8连接到BOOT脚,布线时C8要尽可能靠近IC,使连线尽可能短。输出滤波电容C9连接在VOUT和PGND间,其输出端、L1的输出端、PH脚和PGND脚之间组成的环路越小越好。

最后要进行布线和敷铜。敷铜时,输入输出信号线应尽量避免相邻平行,最好加线间地线,以免发生反馈耦合;电源和地的导线应尽可能用宽线,印制导线的拐弯处一般取圆弧形;尽量避免使用大面积铜箔,必须用大面积铜箔时,最好用栅格状。

根据上述原则设计出的电路经实际测试,电源各项指标均符合系统要求。其中,输出的核心电压VCCINT为1.5V,电流为6A;辅助电压VCCAUX为3.3V,电流为250mA;输出驱动电压VCCO为3.3V,电流为5.75A。

FPGA供电模块的设计,在选择方案时,要综合考虑系统要求、成本、效率、设计灵活性及封装等众多因素,做出全面的折衷考虑,既满足设计要求,又降低设计复杂度和成本。

电子发烧友App

电子发烧友App

评论