电子发烧友网核心提示:对初级FPGA工程师而言,必须掌握FPGA相关基础知识、精通硬件描述语言、熟练数字电路设计、加强工程项目的实践。应广大初级FPGA工程师/FPGA爱好者之需,电子发烧友网策划整合并隆重推出《FPGA核心基础知识详解》系列技术文章,以后会陆续推出其他章节,敬请广大工程师朋友继续关注和留意。

一、FPGA基础知识

1. 什么是 FPGA?

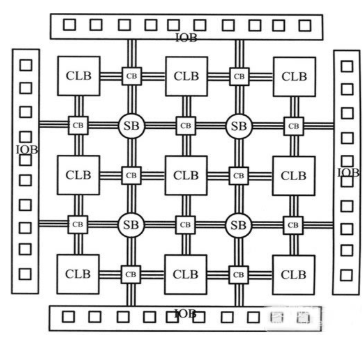

现场可编程门阵列 (FPGA) 是由通过可编程互连连接的可配置逻辑块 (CLB) 矩阵构成的可编程半导体器件。相对于专为特定设计定制构建的专用集成电路 (ASIC) 而言,FPGA 能通过编程来满足应用和功能要求。

虽然市面上也有一次性可编程 (OTP) FPGA,但绝大多数是基于 SRAM 的类型,可随着设计的演化进行重编程。

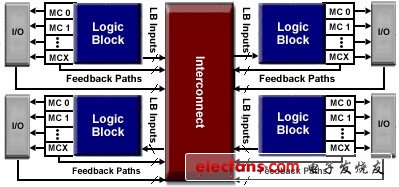

请参考下面的内容来具体了解方框图中的各个突出显示区域。

图1.1 FPGA单元结构

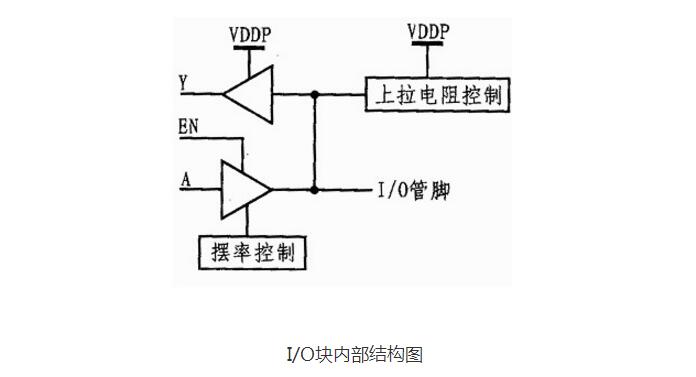

(1)IOB 细节

目前的 FPGA 可支持许多种 I/O 标准,因而为您的系统提供了理想的接口桥接。FPGA 内的 I/O 按 bank 分组 (见下图) ,每个 bank 能独立支持不同的 I/O 标准。 目前最先进的 FPGA 提供了十多个 I/O bank,能够提供灵活的 I/O 支持。

图1.2 FPGA内的 I/O 按bank分组图示

(2)CLB 细节

可配置逻辑块是 FPGA 的基本逻辑单元。实际数量和特性会依器件的不同而改变,但是每个 CLB 都包含一个由 4 或 6 个输入、一些选择电路(多路复用器等)和触发器组成的可配置开关矩阵。开关矩阵具有高度的灵活性,经配置可以处理组合型逻辑、移位寄存器或 RAM。

图1.3高层次的 CLB 简介

(3)DCM 细节

业界大多数 FPGA 均提供数字时钟管理(Xilinx 所有 FPGA 均具有此特性),几乎消除了过去设计者在将全局信号设计到 FPGA 中时不得不面对的歪斜及其它问题。

(4)FPGA 的常见特性

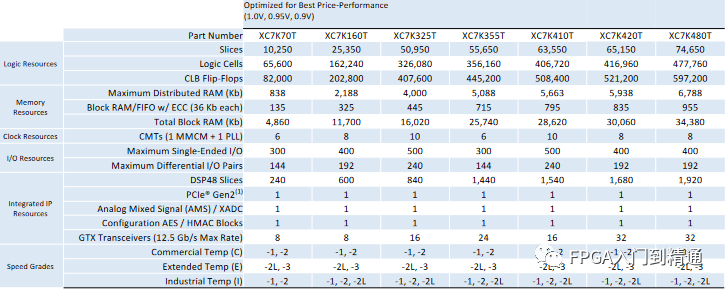

当今的 FPGA 已经远远超出了先前版本的基本性能,并且整合了如 RAM、时钟管理和 DSP 这些常用功能的硬(ASIC 型)块。 FPGA 的基本组件如下。

a.可配置逻辑块 (CLB)

CLB 是 FPGA 的基本逻辑单元。实际数量和特性会依器件的不同而改变,但是每个 CLB 都包含一个由 4 或 6 个输入、一些选择电路(多路复用器等)和触发器组成的可配置开关矩阵。开关矩阵具有高度的灵活性,经配置可以处理组合型逻辑、移位寄存器或 RAM。

b.互连

CLB 提供了逻辑性能,灵活的互连布线则负责在 CLB 和 I/O 之间传递信号。布线有几种类型,从设计用于专门实现 CLB 互连、到器件内的高速水平和垂直长线、再到时钟与其它全局信号的全局低歪斜布线。除非另行说明,否则设计软件会将互连布线任务隐藏起来,用户根本看不到,从而大幅降低了设计复杂性。

c.SelectIO (IOB)

目前的 FPGA 可支持许多种 I/O 标准,因而为您的系统提供了理想的接口桥接。FPGA 内的 I/O 按 bank 分组 (见下图) ,每个 bank 能独立支持不同的 I/O 标准。目前最先进的 FPGA 提供了十多个 I/O bank,能够提供灵活的 I/O 支持。

d.存储器

大多数 FPGA 中都提供嵌入式块 RAM 存储器,这样可以在您的设计中实现片上存储。这些能为您的设计实现片上存储。Xilinx FPGA 提供高达 10 Mbits 的片上存储 (每个区块大小为 36 Kbits),能够支持真正的双端口运行。

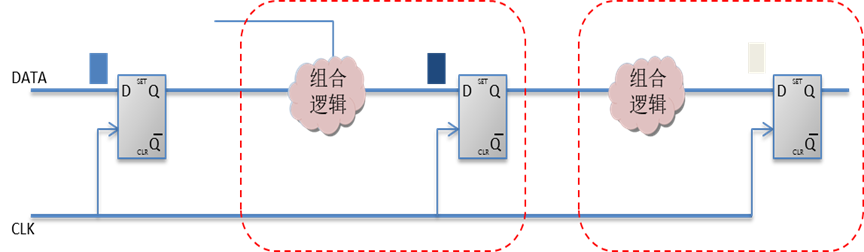

e.完整的时钟管理

业界大多数 FPGA 都提供数字时钟管理(所有 Xilinx FPGA 都具有此特性)Xilinx 推出的最高级 FPGA 提供了数字时钟管理和锁相环锁定功能,不仅提供了精确时钟综合功能,而且能够降低抖动和实现过滤。

(5)FPGA解决方案、应用以及终端市场

由于其自身的可编程特性, FPGA 成为了众多不同的市场的理想选择。Xilinx 作为业界领先公司提供了包含 FPGA 器件、高级软件和可配置即用型 IP 核等在内的全套解决方案,可满足以下市场和应用的需求:

a.应用方案

航空航天和军用产品:用于实现图形处理、波形生成和 SDR 部分重配置的抗辐射 FPGA 与 IP 核。

汽车:用于实现网关与驾驶员辅助系统、舒适性、便捷性、车载信息娱乐的汽车芯片和 IP 解决方案。

广播:在视频和音频被广泛采用(从演播室到生产与传输,再到消费类)的同时,该解决方案也实现了一系列广播链任务。

消费类:高性价比解决方案支持新一代功能齐全的消费类应用,如整合式手持设备、数字平板显示器、信息家电、家庭网络和住宅机顶盒等。

工业/科学/医疗:工业解决方案可以解决工业自动化、电机控制和高端医疗成像领域中的特殊市场需求和挑战。

存储与服务器:针对网络附加存储(NAS)、存储局域网(SAN)、服务器、存储设备等的数据处理解决方案。

无线通信:针对无线设备的RF、基带、连接、传输和网络解决方案,可支持 WCDMA、HSDPA、WiMAX等标准。

有线通信:针对可编程网络线卡包处理、成帧器/MAC、串行背板以及更多其它应用的端对端解决方案

b.技术解决方案

DSP:Xilinx XtremeDSP™ 计划可帮助您开发出高性能定制 DSP 解决方案,以满足航空航天和军用产品、数字通信、多媒体、视频以及成像等行业需求

嵌入式处理:Xilinx 针对您独特的饿嵌入式应用提供了一系列高度灵活的创新型处理解决方案。

二、FPGA与ASIC

1.ASIC 和 FPGA 的优劣势分析

ASIC 和 FPGA 具有不同的价值主张,在作出选择前必须仔细评估。两种种技术对比。这里介绍了 ASIC 和 FPGA 的优势与劣势:

a.FPGA 的设计优势

更快的上市时间——无需布局、掩模和其它制造步骤;

无前期 NRE(非重发性设计成本)—— 与 ASIC 设计有关的成本;

缩短了设计周期——由于软件可以处理很多布线、布局和时序问题;

更加可预测的项目周期——由于消除了可能的重置、晶圆容量等阶段;

现场可重编程能力——可以远程上传的新比特流。

b.ASIC 的设计优势

全定制性能——实现设计,因为器件根据设计规范进行生产;

降低单位成本——用于实现大批量设计;

小型化——因为器件根据设计规范进行生产;

较高的原始内部时钟速度。

过去 FPGA 用于速度/复杂度/容量较低的设计,而当今的 FPGA 则可以轻松突破 500 MHz 的性能障碍。FPGA 能够以更低的价格实现无可比拟的逻辑密度增加和众多其它特性(如嵌入式处理器、DSP 模块、时钟技术和高速串行),现已几乎成为任何设计的首选。

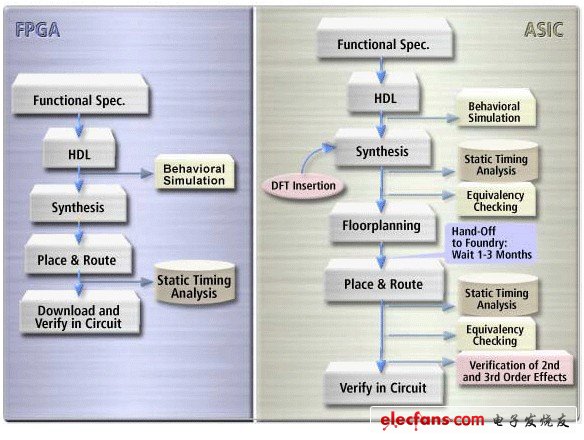

2.FPGA 和ASIC 的设计流程对比

图2.1 FPGA与ASIC的设计流程对比

由于设计逻辑已综合到通过验证的定义好的 FPGA 器件上,这样 FPGA 设计流程就避免了项目中既复杂又耗时的平面规划、布局布线、时间分析以及掩码/项目阶段。

然而,必要时,Xilinx 还能够提供先进的布局规划、层次化设计和时序工具,使用户能够将要求最苛刻的设计的性能最大化

三、CPLD基础知识

1.CPLD 是什么?

CPLD 由完全可编程与/或阵列以及宏单元库构成。 与/或阵列可重编程,能够执行众多逻辑功能。宏单元是执行组合逻辑或时序逻辑的功能块,同时还提供了真值或补码输出和以不同的路径反馈等更高灵活性。

传统上, CPLD 采用模拟传感放大器来提高架构性能。This performance boost came at the cost of very high current requirements. Xilinx推出的CoolRunner™-II CPLD 采用创新型全数字内核,能够以极低的功耗达到同样的性能水平。 这样,设计人员能够采用同一CPLD 架构实现高性能和低功耗两种不同设计。避免采用模拟传感放大器还使架构具有可扩展能力,这样随着工艺技术一代一代的进步,不仅大幅降低了成本,而且还实现了特性增强。

2.为何选用CPLD?

由于其具有独特的功能,CPLD 在系统设计中可完成多种有用的功能

(1)可重编程

可根据需要,立即、随意修改设计,且不会带来任何成本,能构建可重配置系统,修正ASIC错误,随时随地升级系统功能,从而节约时间,降低成本,简化设计。

(2)简单易用

利用 CPLD 进行设计即简单又容易,可轻松适应已有的设计流程;节约时间,降低成本并简化设计。

(3)低成本

不仅可通过重编程来修正系统错误,降低单位成本,而且还可取代 TTL 和 ASSP 解决方案,减少电路板组件数量并提高可靠性;从而降低了设计成本、系统成本和维护成本。

(4)非易失性

断电模式下也能编程,当系统上电时 CPLD 功能立即可用,存储的设计内容几乎不可能被窃取;提高安全性,简化了设计。

3.为何选用Xilinx CPLD?

做为可编程逻辑解决方案的市场领头羊,Xilinx提供完整的解决方案来满足设计人员的 CPLD 需求:

(1)高级芯片

成本优化的芯片设计、高性能、低功耗运行、最大范围的封装选择、高级系统特性,每个宏单元 I/O 数量最多。

(2)功能强大的免费设计工具

ISE WebPACK 设计工具提供了用于开发所有 Xilinx CPLD 产品的最完善、简便易用的桌面软件解决方案。

(3)各种其他支持

免费的参考设计和应用手册,可立即着手设计的完整设计套件, 庞大的分销商网络、销售代表、现场应用工程师和内部技术支持网络,以及大量的在线技术文档。

四、利用CPLD进行设计

1.Xilinx CPLD 带来了极大的设计优势

了解 CPLD 使用的特性与优势, 有助于简化设计、降低开发成本并加速产品上市进程。CPLD 优势概览:简化设计;降低开发成本;实现产品创收增长;缩小板级空间;提高系统可靠性;加速产品上市进程 。

2.利用CPLD 进行设计的4 个简单步骤

第 1 步:选择 CPLD 器件

在为设计选择合适的 CPLD 的过程中,需要考虑以下几个方面(其优先次序依设计的不同而不同):

(1)密度与 I/O

通过将您的设计提交到免费下载的 ISE® WebPACK™ 软件,您可确定您的设计所需要的 Xilinx CPLD 的规模(逻辑密度和 I/O)。

(2)性能

Xilinx CPLD 有多种速度级别,因此您只需购买您所需性能的 CPLD 器件。利用 ISE WebPACK 确定器件的速度级别以满足您系统的时序要求。

(3)电压和功耗

不同的 Xilinx CPLD 系列具有不同的电压(电源和 I/O)和功耗(静态和动态)要求。

(4)封装

Xilinx CPLD 采用廉价的 QFP 封装、超小型芯片级封装, 以及 I/O 数量较多的 BGA 封装等多种封装形式。

(5)Xilinx CPLD 系列

a.CoolRunner™ Series

Xilinx CoolRunner 系列 CPLD 是业界功耗最低、性能最高 的器件。 这些 CPLD 提供了诸如 I/O banking 、高级时钟控制,以及出色的设计安全性等高级功能来支持系统级设计。

b.XC9500 系列

提供 5.0V (XC9500 系列) 和 3.3V (XC9500XL 系列) 版本,这些低成本 CPLD 系列产品提供了当今尖端系统设计所需的高性能、丰富特性集和 灵活性 。

第 2 步:选择软件包

(1)CPLD 和简单的 FGPA 设计

要实现基本的 CPLD 或 FPGA 设计,您需要下载免费的ISE WebPACK 软件工具。

(2)任何 CPLD/ FPGA 设计

除了 ISE WebPACK 软件工具外,Xilinx 还提供了多种软件包,以满足不同的设计要求点击这里来确定最适合您的设计需求的软件包。

第 3 步:实现设计

选好 CPLD 器件并下载了必要的软件后,下一步就是设计的实现。设计实现包括:设计实现包括:

(1)设计输入

(2)对原型进行编程和测试

(3)技术文档

每个 CPLD 产品页面都提供了应用指南、参考设计、开发板、配置工具及其它有用信息的链接,可帮助设计人员快速、轻松地完成设计。

第 4 步:购买 CPLD

有几种购买 Xilinx 解决方案的方法:Xilinx网上商城Xilinx分销商

这两种渠道都提供芯片、软件、编程硬件及其它产品和资源。Xilinx 销售办事处和客户 支持中心可以保证使用 Xilinx CPLD 是一次简单而令人满意的体验。

电子发烧友App

电子发烧友App

评论