移动、网络、服务器和FPGA等诸多应用领域。此次合作非常深入,开始于工艺制造的早期阶段,贯穿于设计分析至设计签收,全面有效解决FinFETs设计存在的问题,从而交付能实现超低功耗、超高性能芯片的设计方案。

2013-04-09 11:00:05 798

798 昨日台积电官方宣布,16nm FinFET Plus(简称16FF+)工艺已经开始风险性试产。16FF+是标准的16nm FinFET的增强版本,同样有立体晶体管技术在内,号称可比20nm SoC平面工艺性能提升最多40%,或者同频功耗降低最多50%。

2014-11-14 09:31:58 2127

2127 All Programmable 技术和器件的全球领先企业赛灵思公司(Xilinx, Inc. (NASDAQ:XLNX))今天宣布其与台积公司( TSMC)已经就7nm工艺和3D IC技术开展合作,共同打造其下一代All Programmable FPGA、MPSoC和3D IC。

2015-05-29 09:09:49 1802

1802 12纳米领先性能(12LP)的FinFET半导体制造工艺。该技术预计将提高当前代14纳米 FinFET产品的密度和性能,同时满足从人工智能、虚拟现实到高端智能手机、网络基础设施等最具计算密集型处理需求的应用。 这项全新的12LP技术与当前市场上的16 /14纳米 FinFET解决方案相比,电路密度提高

2017-09-25 16:12:36 8666

8666 16nm节点上,X公司继续选择台积电。X公司和台积电共同宣布联手推动一项赛灵思称之为“FinFast”的专项计划,采用台积电先进的 16FinFET工艺打造拥有最快上市、最高性能优势的FPGA器件

2013-08-22 14:46:48

: 超高性能Zynq UltraScale+ MPSoC核心平台MYD-CZU3EG开发板基于XILINX 16nm 新一代 ARM+FPGA处理器 XCZU3EG,每瓦性能提升5倍4GB DDR4

2020-05-23 15:36:29

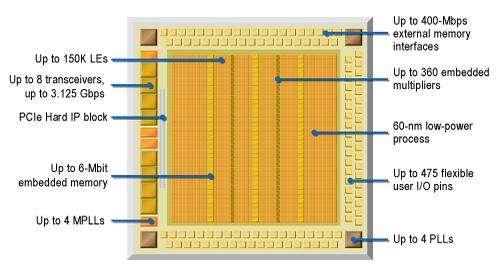

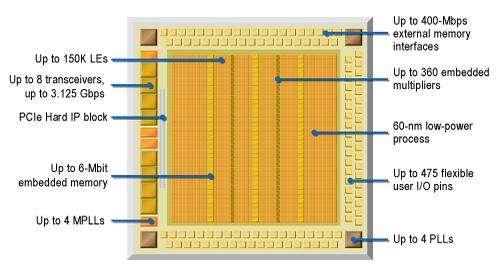

具有200K逻辑单元(LE)、8Mbits存储器,而静态功耗不到1/4瓦,该系列设立了功耗标准。采用台积电(TSMC)的低功耗(LP)工艺技术进行制造,无论是通信设备、手持式消费类产品,还是软件无线电

2015-04-17 12:05:21

FPGA厂商不断采用更先进的工艺来降低器件功耗,提高性能,同时FPGA对供电电源的精度要求也越加苛刻,电压必须维持在非常严格的容限内,如果供电电压范围超出了规范的要求,就有会影响到FPGA的可靠性,甚至导致FPGA失效。

2019-10-08 07:39:47

FPGA器件售价不到10美元(在与门阵列产品相当的批量时)。 性能和功耗 与传统数据处理方法不同,DSP采用了高度流水线化的并行操作。而FPGA结构则可以做得更好,达到更高的性能。FPGA具有

2011-02-17 11:21:37

200K逻辑单元(LE)、8Mbits存储器,而静态功耗不到1/4瓦,该系列设立了功耗标准。采用台积电(TSMC)的低功耗(LP)工艺技术进行制造,无论是通信设备、手持式消费类产品,还是软件无线电设备

2019-04-15 02:21:50

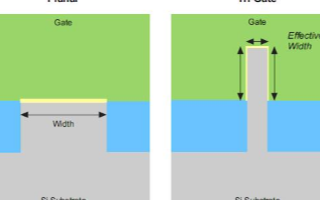

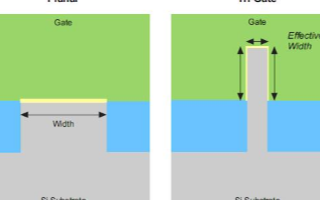

增强;同时也极大地减少了漏电流的产生,这样就可以和以前一样继续进一步减小Gate宽度。目前三星和台积电在其14/16nm这一代工艺都开始采用FinFET技术。图6:Intel(左:22nm)和Samsung(右:14nm)Fin鳍型结构注:图3、图6的图片来于网络。

2017-01-06 14:46:20

。以这一理念作为指导原则,Corsa 将 SDN 定义为简单设计模式。很多其他公司也认同这一基本概念:将软件与硬件分离,通过开放接口进行通信,给予软件所有控制权(大脑)并让硬件(体力)尽可能地高性能

2019-06-20 06:13:19

天生的并行性,拿下高性能计算这块大肥肉自然不在话下。● 片上系统,如Altera公司的SocFPGA和Xilinx公司的Zynq,这类FPGA器件,既有成熟的ARM硬核处理器,又有丰富的FPGA资源

2019-03-22 08:28:31

有没有扩展UltraScale产品系列的计划? 除了采用台积电公司(TSMC)20nm SoC工艺技术构建的Kintex和Virtex UltraScale器件之外,赛灵思还将推出采用台积电16

2013-12-17 11:18:00

描述PMP10555 参考设计提供为移动无线基站应用中的 Xilinx® Ultrascale® 16nm 系列 FPGA/SoC 供电所需的所有电源轨。此设计对内核及两个多输出降压型稳压器 IC

2018-11-19 14:58:25

`描述PMP10555 参考设计提供为移动无线基站应用中的 Xilinx® Ultrascale® 16nm 系列 FPGA/SoC 供电所需的所有电源轨。此设计对内核及两个多输出降压型稳压器 IC

2015-05-11 10:46:35

台积电0.18工艺电源电压分别是多少?是1.8v跟3.3v吗?

2021-06-25 06:32:37

台积电宣布5nm基本完工开始试产:面积缩小45%、性能提升15%.pdf(105.52 KB)

2019-04-24 06:00:42

` 观点:在技术领先的优势下,台积电获得苹果iPhone5芯片追加订单已成事实。然而,在iPhone 5推出后,苹果已朝下一世代A7处理器迈进,台积电凭借技术领先的优势,预估未来1-2年内

2012-09-27 16:48:11

台积电正在大量生产用于苹果iPhone8手机的10nm A11处理器。消息称,苹果可能在下个月初正式发布iPhone 8,但是具体发货日期仍然不确定。 据悉,台积电已经采用10nm FinFET

2017-08-17 11:05:18

全球领先的中文互联网搜索引擎提供商百度正在采用赛灵思FPGA加速其中国数据中心的机器学习应用。两家公司正合作进一步扩大FPGA加速平台的部署规模。新兴应用的快速发展正日渐加重计算工作的负载,数据中心

2016-12-15 17:15:52

检测电路,以适应于不同电机及不同控制方式的要求;同时由于采用了高性能的MCU,更多类型的通信接口可被灵活应用,如:URAT、CAN、RJ45等。

2019-07-09 08:24:02

采用印刷台手工印刷焊膏的工艺看完你就懂了

2021-04-25 07:06:44

文章目录前言微控制器系统(MSS)高性能FPGA可编程模拟前端(AFE)模拟计算引擎(ACE)特点简介设计流程器件选型前言Actel SmartFusion®系列智能型混合信号 FPGA 采用

2021-07-22 09:50:25

随着FPGA制造工艺尺寸持续缩小、设计配置更加灵活,以及采用FPGA的系统的不断发展,原来只采用微处理器和ASIC的应用现在也可以用FPGA来实现了。最近FPGA供应商推出的新型可编程器件进一步缩小

2019-09-20 07:01:40

随着FPGA制造工艺尺寸持续缩小、设计配置更加灵活,以及采用FPGA的系统的不断发展,原来只采用微处理器和ASIC的应用现在也可以用FPGA来实现了。最近FPGA供应商推出的新型可编程器件进一步缩小了FPGA和ASIC之间的性能差别。

2019-09-23 08:34:34

处理器号称是“全球第一个AI汽车超级芯片”,将采用台积电16nm FinFET+工艺制造,集成多达70亿个晶体管,性能方面,Xavier预计可以达到30 DL TOPS,比现在的Drive PX 2平台

2018-07-31 09:56:50

工艺,1.2v内核供电,大容量高性能FPGA。 简评:性能超越Stratix,是未来几年中,Altera在高端FPGA市场中的主力产品。 *StrtratixV为altera目前的高端产品,采用

2018-08-20 09:52:02

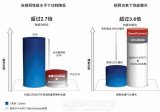

Altera公司近期宣布,开始交付业界第一款高性能28-nm FPGA量产芯片。Stratix V FPGA是唯一使用TSMC 28HP工艺制造的FPGA,比竞争解决方案高出一个速率等级

2012-05-14 12:38:53

GD32E5高性能微控制器,采用台积电低功耗40纳米(40nm)嵌入式闪存工艺构建,具备业界领先的处理能力、功耗效率、连接特性和经济的开发成本。推动嵌入式开发向高精度工业控制领域扩展,解决数字电源

2021-12-16 08:13:14

转自http://www.eet-china.com/ART_8800697889_480201_NT_08124b24.HTM台积电借16nm FinFET Plus及InFO WLP 通吃英特尔

2014-05-07 15:30:16

,未来就要看竞争对手的制程技术能否赶得上脚步。 近期高通与台积电持续紧密合作,业界传出在最先进的7纳米制程技术上,台积电因为技术开发领先三星电子(Samsung Electronics),可望拿回高通7

2017-09-22 11:11:12

产电源管理芯片。高通将使用台积电的BCD工艺(Bipolar-CMOS-DMOS)来生产其新一代电源管理芯片,并将台积电作为其电源管理芯片的主要代工合作伙伴。台积电将于2017年底开始小批量生产高

2017-09-27 09:13:24

合作开发专门针对FPGA要求的工艺。这一新工艺称为TSMC 28nm HPL(高性能低功耗)工艺技术,为Xilinx FPGA的所有市场提供最佳的性能和功耗组合。这实质上意味着需要以高性能运行的设计的功耗

2016-12-21 10:56:25

Xilinx Spartan-6器件系列的全面支持。电子设计人员可针对首选的FPGA(目前,Altium Designer可支持60多款FPGA产品),或各种备选解决方案,采用AltiumDesigner对其性能、功耗以及其它设计参数进行比全文下载

2010-04-24 10:07:11

切换,串口速率最高达921600bps。目前市面上相关产产品支持串口数量较少,且单个串口速率较低,类似支持16 路串口的产品售价至少在2000 元以上;2.高性能。系统方案采用FPGA+全硬件TCP

2014-11-25 16:04:21

有着严格的浪涌电流和稳态工作电流限值要求,因此由总线供电的器件应用经常忽视FPGA,而是更愿意采用性能和灵活性都不及 FPGA 的微控制器解决方案。随着赛灵思低功耗系列器件中最新成员Artix-7

2016-07-27 17:14:50

可满足高性能数字接收机动态性能要求的ADC和射频器件有哪些?

2021-05-28 06:45:13

各类常用工艺库台积电,中芯国际,华润上华

2015-12-17 19:52:34

基于全新Arm® Cortex®-M33内核的GD32E5系列高性能微控制器。这系列MCU采用台积电低功耗40纳米(40nm)嵌入式闪存工艺构建,具备业界领先的处理能力、功耗效率、连接特性和更经济

2021-11-04 08:38:32

通过FPGA来构建一个低成本、高性能、开放架构的数据平面引擎可以为网络安全设备提供性能提高的动力。随着互联网技术的飞速发展,性能成为制约网络处理的一大瓶颈问题。FPGA作为一种高速可编程器件,为网络安全流量处理提供了一条低成本、高性能的解决之道。

2019-08-12 08:13:53

是什么推动着高精度模拟芯片设计?如何利用专用晶圆加工工艺实现高性能模拟IC?

2021-04-07 06:38:35

如何成功实现高性能数字无线电?

2021-05-24 06:25:47

用高性能的FPGA器件设计符合自己需要的DDS电路有什么好的解决办法吗?

2021-04-08 06:23:09

1.工艺节点 首先不管选择什么厂家的产品,都建议在其主流产品中选择合适的芯片。 以上是目前 Xilinx 主流的也是常用的几个 FPGA 产品系列,这里不谈传说中的后两个系列

2020-12-23 17:21:03

巨头,Xilinx和Altera都建议在超声成像的波束生成器(Beam Former)设计中采用具有DSP性能的FPGA。图3:Xilinx的高性能数字波束生成器方案。Xilinx亚太区DSP产品和解

2009-09-17 14:52:33

成功实现高性能数字无线电

2020-12-22 06:59:41

本帖最后由 华强芯城 于 2023-3-17 09:16 编辑

晶圆代工巨头——台积电近日传出涨价20%的消息,业内轰动。这是台积电继2020年底上涨超10%之后,一年之内,又一次的大幅上涨

2021-09-02 09:44:44

,所以只能以旧工艺(16nm制程)制造A10处理器。除此之外,台积电还将独家代工重大变化的2017年版iPhone采用的A11处理器。据称A11芯片将采用10纳米FinFET工艺,最早有望于明年二季度

2016-07-21 17:07:54

的必经前提步骤,而先进的制成工艺可以更好的提高中央处理器的性能,并降低处理器的功耗,另外还可以节省处理器的生产成本。 “芯片门”让台积电备受瞩目 2015年12月份由台积电举办的第十五届供应链管理论

2016-01-25 09:38:11

【来源】:《电子设计工程》2010年02期【摘要】:<正>赛灵思公司与联华电子共同宣布,采用联华电子高性能40nm工艺的Virtex-6FPGA,已经完全通过生产前的验证

2010-04-24 09:06:05

)里程碑式技术突破,为同样追求变革、渴望在激烈的市场竞争中领先的客户带来了一次次惊喜与震撼。全球第一个发货28nm 产品- 与台积电(TSMC)通力协作,创新性地推出高性能低功耗 (HPL) 工艺技术- 在

2012-03-22 15:17:12

描述PMP9335专为使用 TPS84A20 和 TPS84320 的 Xilinx Zynq FPGA 应用而设计。此设计使用外部计时器将开关频率同步到 300 kHz。它还采用受控的加电和断电

2022-09-19 07:37:25

Xilinx®7系列FPGA包括四个FPGA系列,可满足整个系统要求,包括低成本,小尺寸,成本敏感的大批量应用程序,可满足最苛刻的超高端连接带宽,逻辑容量和信号处理能力高性能的应用程序。7系列

2022-11-10 15:11:11

本文介绍一种基于FPGA 和DSP 的高性能PCI 数据采集处理卡的电路原理设计和PCI接口软件设计。该数据采集处理卡主要采用TI 公司的TMS320C6416 数字信号处理器和XILINX公司VIRTEX2 系列的

2009-08-24 10:55:32 34

34 赛灵思高性能40nm Virtex-6 FPGA系列即将转入量产

赛灵思公司(Xilinx, Inc.)与联华电子(UMC)今天共同宣布,采用联华电子高性能40nm工艺的Virtex-6 FPGA,已经完全通过生产前的验

2010-01-26 08:49:17 851

851 统一工艺和架构,赛灵思28纳米FPGA成就高性能和低功耗的完美融合

赛灵思公司(Xilinx)近日宣布,为推进可编程势在必行之必然趋势,正对系统工程师在全球发布赛灵思

2010-03-02 08:48:51 576

576 Synopsys和Xilinx合作出版业界首本基于FPGA的SoC设计原型方法手册。

2011-03-21 10:26:23 810

810 本书系统地论述了Xilinx FPGA开发方法、开发工具、实际案例及开发技巧,内容涵盖Xilinx器件概述、Verilog HDL开发基础与进阶、Xilinx FPGA电路原理与系统设计

2012-07-31 16:20:42 11268

11268

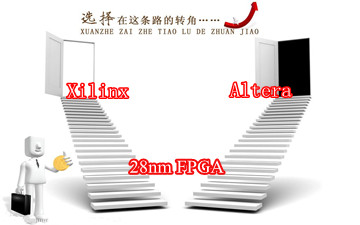

在28nm FPGA战场上,Xilinx和Altera已经展现了两种完全不同的竞争策略:Xilinx选择28nm高性能与低功耗工艺,构建出一个全新的、统一的、可扩展的架构。其优点是未来Virtex

2012-09-21 14:57:10

新思科技公司日前宣布:该公司与三星在FinFET技术上的多年合作已经实现了一个关键性的里程碑,即采用三星的14LPE工艺成功实现了首款测试芯片的流片

2013-01-09 12:11:31 1062

1062 全可编程技术和器件的全球领先企业赛灵思公司 (Xilinx, Inc. (NASDAQ:XLNX))今天宣布,全球领先的中文互联网搜索引擎提供商百度正在采用赛灵思 FPGA 加速其中国数据中心的机器

2017-02-08 03:15:37 199

199 ® UltraScale+™ FPGA 面向首批客户开始发货,这是业界首款采用台积公司(TSMC) 16FF+ 工艺制造的高端 FinFET FPGA。赛灵思在 UltraScale+ 产品系列与设计工具上一直

2017-02-08 18:03:19 248

248 确保连续四代全可编程技术及多节点扩展的领先优势四代先进工艺技术和3D IC以及第四代FinFET技术合作 2015年5月28日, 中国北京 - All Programmable 技术和器件的全球领先

2017-02-09 03:48:04 198

198 作者:Mike Santarini 赛灵思公司赛灵思杂志发行人 mike.santarini@xilinx.com 台积公司的16nm FinFET工艺与赛灵思最新UltraRAM

2017-02-09 06:28:12 1249

1249

作者:Steve Leibson, 赛灵思战略营销与业务规划总监 今天,赛灵思同时推出了基于TSMC全新16FF+ FinFET工艺技术的3款16nm UltraScale+全可编程器件系列。包含

2017-02-09 09:12:38 500

500

2015年,基于FinFET 工艺的IC产品将大量面市,除了英特尔的X86处理器和一些ASIC处理器外,FPGA也正式步入FinFET 3D晶体管时代,2月23日,羊年大年初五,赛灵思率先发布基于16nm FinFET 3D晶体管的FPGA新品,再次创下业界第一,开启了FinFET FPGA的新时代。

2019-10-06 11:57:00 3095

3095 本文介绍设计人员如何采用针对FinFET工艺的IP而克服数据转换器设计的挑战。

2017-09-18 18:55:33 17

17 5月23日早间消息,联发科宣布推出中端芯片Helio P22。Helio P22采用台积电12nm FinFET工艺打造,CPU设计为8核A53,最高主频2.0GHz。GPU采用PowerVR

2018-05-23 14:03:00 2274

2274 合并在一起处理。Xilinx FPGA 的高性能可提供出色的音频性能和质量,能够充分满足大多数应用的需求。

2018-06-22 14:57:02 952

952 电子有限公司延续双方十年之久的战略性晶圆代工合作,将采用三星10纳米FinFET制程工艺打造Qualcomm Technologies最新款顶级处理器——Qualcomm®骁龙™835处理器。

2019-03-15 16:58:48 945

945 赛灵思公司(Xilinx)今天宣布Artix-7 FPGA AC701评估套件正式推出,专门支持开发满足低成本、低功耗应用需求的高性能系统。这款最新评估套件配套提供All Programmable

2018-09-26 16:27:00 2248

2248 赛灵思(Xilinx)昨(1)日宣布,旗下采用台积电最新16纳米制程的最新可编程逻辑芯片(FPGA)VirtexUltraScale+正式出货首家客户采用,并将元件或主机板出货给超过60家客户。

2018-11-08 09:41:33 722

722 该视频重点介绍了Xilinx 16nm Kintex UltraScale +器件中双工作电压的性能,功耗和灵活性。

2018-11-21 06:11:00 4627

4627 在本视频中,了解Xilinx采用高带宽存储器(HBM)和CCIX技术的16nm Virtex UltraScale + FPGA的功能和存储器带宽。

2018-11-27 06:20:00 3624

3624 目前最大的两个FPGA厂商Altera公司和Xilinx公司的FPGA产品都是基于SRAM工艺来实现的。这种工艺的优点是可以用较低的成本来实现较高的密度和较高的性能;缺点是掉电后SRAM会失去所有配置,导致每次上电都需要重新加载。

2019-11-25 09:30:43 4029

4029

2013年2月,Altera公司与Intel公司共同宣布了Altera下一代最高性能FPGA产品的生产将独家采用Intel的14nm 3D Tri-Gate(三栅极)晶体管技术。这使得Altera

2020-03-12 10:30:33 1523

1523

FPGA工艺尺寸的进步和更加灵活的设计配置、以及基于FPGA的系统取得的进步已经使FPGA制造商充满信心地进入了以前由微处理器和ASIC供应商垄断的市场。最近,Xilinx的VirtexTM和Altera的Stratix产品系列分别推出了新器件,进一步缩小了性能差距,再次提高了性能标准。

2020-07-27 18:30:59 363

363 Xilinx 7系列FPGA概览 文章目录 Xilinx 7系列FPGA概览 1.Xilinx的四个工艺级别 2.Virtex、Kintex、Artix和Spartan 3.7系列特点 4.7系列

2020-11-13 18:03:30 14065

14065 Xilinx FPGA的监控器件补充部件指南

2021-04-27 19:28:56 5

5 AMD-Xilinx在20nm & 16nm节点Ultrascale系列器件使用FinFET工艺,FinFET与Planar相比在相同速度条件下功耗低20%-50%。

2022-12-29 14:44:49 1165

1165 负载效应 (loading) 的控制对良率和器件性能有重大影响,并且它会随着 FinFET(鳍式场效应晶体管)器件工艺的持续微缩变得越来越重要[1-2]。当晶圆的局部刻蚀速率取决于现有特征尺寸和局

2023-01-06 10:48:36 644

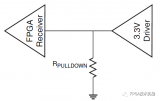

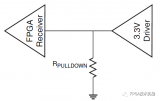

644 Xilinx 7系列FPGA IO Bank分为HP Bank和HR Bank,HP IO接口电压范围为1.2V~1.8V,可以实现高性能,HR IO接口电压范围为1.2V~3.3V。

2023-05-15 09:27:58 2119

2119

是一款基于FPGA的数字信号处理器,其采用了Xilinx Virtex-6 XC6VLX760型号的FPGA。 Xilinx Virtex-6序列是Xilinx公司推出的一款高性能FPGA芯片,采用了

2023-08-16 11:15:40 718

718 电子发烧友网站提供《为新时代高性能航天级Xilinx FPGA供电.pdf》资料免费下载

2023-09-14 11:24:36 0

0 芯片的知识以及特点。 一、7系列芯片的工艺级别 xilinx 7系列FPGA芯片采用的是28nm生产工艺,主要分为Spartan、Artix、Kintex和Virtex四个系列。 Xilinx

2023-11-28 10:20:02 392

392

正在加载...

电子发烧友App

电子发烧友App

评论