Xilinx 20nm All Programmable UltraScale产品系列现已面世

Xilinx将业界最大容量器件翻番,达到创纪录的440万个逻辑单元

1. 赛灵思于2013年12月10日发布什么消息?

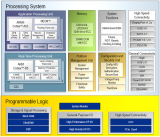

赛灵思今天宣布推出20nm All Programmable UltraScale™产品系列,并配套提供产品技术文档和Vivado®设计套件支持。继2013年11月首款20nm芯片发货后,赛灵思继续积极推动UltraScale器件系列发货进程。该器件系列采用业界唯一的ASIC级可编程架构以及Vivado ASIC增强型设计套件和UltraFast™设计方法,提供了可媲美ASIC级的性能优势。

此外,赛灵思还宣布了一项新纪录,作为UltraScale产品系列之一,赛灵思此次推出的Virtex® VU440® UltraScale™器件,将业界最大容量器件的容量翻番,达到440万个逻辑单元。Virtex VU440 UltraScale器件的推出, 让赛灵思在器件密度方面的优势从28nm的2倍提升到20nm的4倍,容量超过了所有其他任何可编程器件。

2. 赛灵思实现的系统级性能和集成度提升1.5倍到2倍,领先整整一代。这具体是什么含义?

分析赛灵思采用20nm工艺推出的UltraScale器件的特性和功能,我们看到竞争对手需要发展到14nm工艺节点才能与赛灵思目前的水准持平。主要对比如下:

1. ASIC级UltraScale架构能为赛灵思FPGA、3D IC和SoC带来哪些优势?

该架构在布线、类似ASIC时钟分布、逻辑架构以及针对关键路径优化的重要模块级创新等方面具有明显的优势。这些增强功能可以满足客户在海量数据流、I/O带宽以及实时数据包、 DSP和图像处理等方面更高性能设计的要求。UltraScale架构创新技术与Vivado设计套件结合使用,可在不降低性能的前提下实现90%以上的器件利用率。

首批Kintex®和Virtex® UltraScale器件的推出将进一步扩展赛灵思的All Programmable产品系列。

2. UltraScale架构如何应对海量数据流挑战?

新一代布线方案 - UltraScale新一代互连架构与Vivado设计套件进行了协同优化,在可编程逻辑布线方面取得了真正的突破。赛灵思将精力重点放在了解和满足新一代应用对于海量数据流、多Gb智能包处理、多Tb吞吐量以及低时延方面的要求。通过分析得出的结论,就是在这些数据速率下,互连问题已成为影响系统性能的头号瓶颈。UltraScale布线架构可大幅降低高性能高吞吐量设计的布线拥塞问题。结论显而易见:只要设计合适,布局布线就没有问题。

类似ASIC时钟功能 - UltraScale架构通过解决时钟偏移、大量总线布局以及系统功耗管理等基础问题,实现极高的新一代系统速率,有效应对海量数据流挑战。凭借UltraScale类似ASIC的多区域时钟功能,设计人员可以将系统级时钟放置在最佳位置(几乎可以是芯片上的任何位置),使系统级时钟偏移大幅降低达50%。较低的时钟偏移可提高整体系统时序容限,支持更高系统频率。

逻辑基础设施增强 - UltraScale架构提供增强型可配置逻辑块(CLB),能最有效地利用可用资源,从而减少整体互联或线长。现有CLB结构的所有区域都经过分析,探索如何更有效地利用组件。增强功能均支持Vivado软件工具在CLB上放置更多通常不相干的组件,从而打造出一款运行性能高、功耗尽可能低、具有高整体器件利用率的紧凑设计方案。

3. UltraScale产品系列中包含哪些器件?

赛灵思新型UltraScale产品系列的推出扩展了赛灵思市场领先的Kintex、Virtex FPGA和3D IC产品系列。

4. Kintex UltraScale系列有哪些主要特性/优势?

Kintex UltraScale系列产品的主要优势来自于UltraScale在架构上的重要创新,包括:

o 类似ASIC时钟功能,实现可扩展性、高性能和低动态功耗。

o 新一代布线技术支持快速时序收敛。

o 增强型逻辑基础架构最大化性能和器件的利用率。

其他系列特有的功能包括:

o 采用第二代3D IC技术,器件密度多达120万个逻辑单元。

o 8.2 TeraMAC的DSP计算性能。

o 16.3 Gb/s的背板收发器,最低速度级为12.5Gb/s。

o 和支持DDR4的Kintex-7相比,存储器带宽增加2倍。

5. Virtex UltraScale系列有哪些主要特性/优势?

Virtex UltraScale系列产品的主要优势来自于UltraScale在架构上的重要创新包括:

o 类似ASIC时钟功能,实现可扩展性、高性能和低动态功耗。

o 新一代布线技术支持快速时序收敛。

o 增强型逻辑基础架构最大化性能和器件的利用率。

其他系列特有的功能包括:

o 多达440万个逻辑单元、采用20nm工艺以及第二代3D IC技术。

o 33G 芯片至芯片收发器和芯片至光纤收发器,以及28G背板收发器。

o 集成式100G以太网MAC和150G Interlaken内核。

o DDR4存储器,实现最高系统带宽。

6. 有没有扩展UltraScale产品系列的计划?

除了采用台积电公司(TSMC)20nm SoC工艺技术构建的Kintex和Virtex UltraScale器件之外,赛灵思还将推出采用台积电16nm FinFET工艺技术的Virtex UltraScale All Programmable器件,进一步提升系统集成度和系统级单位功耗性能,以满足高端FPGA需求。

7. 赛灵思的堆叠硅片互连技术带给UltraScale 3D IC的附加优势是什么?

Virtex® UltraScale和Kintex® UltraScale系列产品中的连接功能资源数量以及第二代FPGA与3D IC架构中的芯片间带宽都实现了阶梯式增长。布线与带宽以及最新3D IC宽存储器优化接口容量的大幅增加能确保新一代应用以极高的器件利用率实现目标性能。

8. UltraScale架构的目标应用是什么?

基于UltraScale架构的FPGA将满足新一代智能系统 (Smarter System)各种新的高性能架构要求,包括:

o 带智能包处理和流量管理功能的400G OTN

o 带智能波束形成功能的8X8混模LTE和WCDMA无线电

o 带智能图像增强与识别功能的4K2K和8K显示屏

o 用于智能监视与侦查(ISR)的最高性能系统

o 数据中心使用的高性能计算应用

o 赛灵思网站china.xilinx.com 上列出的更多其它应用

9. UltraScale器件对现有的赛灵思产品系列进行哪些补充和扩展?

7系列和Zynq-7000 All Programmable系列在系统性能、能效和成本效率方面都占据行业领先地位。对于很多应用来说,赛灵思28nm产品在未来数年内都将成为客户的最佳解决方案。为了支持更快更智能网络以及智能视觉和智能设备不断增长的大趋势, 将会涌现出一批需要海量数据流的应用,而且其所要求的性能只有通过赛灵思UltraScale架构才能实现。

10. 如何从Kintex UltraScale移植到Virtex UltraScale器件?

采用3种不同封装的Kintex UltraScale可移植到Virtex UltraScale:B1517、A1760、D1924。

11. 通过与Vivado ASIC增强型设计套件协同优化并采用近期推出的UltraFast设计方法有什么优势?

在引领28nm技术的四年中,赛灵思开发出了全新一代设计环境与工具套件,即Vivado设计套件。在20nm和16nm工艺技术方面,赛灵思继续将FPGA、SoC和3D IC与新一代Vivado设计套件实现协同优化。设计人员通过工具、器件和IP的同步构建与优化,可在挖掘芯片最大价值和性能的同时缩短设计与实现流程。

赛灵思不仅推出了设计工具,还包括设计方法。由于产品上市时间和成本很大程度上取决于开发人员如何运用工具解决新一代复杂性问题,因此赛灵思定义了一套All Programmable设计方法。该方法涵盖最佳实践以及一系列项目规划、开发板布局和器件规划的项目表,同时能应对设计创建、实现和配置调试等诸多挑战,从而帮助我们提高了设计生产力与效率,加速了产品上市进程,并提升了结果质量(QoR)。

12. Virtex VU440 UltraScale器件何时开始供货?

首批样片将于2014年第四季度开始供货。

电子发烧友App

电子发烧友App

评论