1.引言

本文针对红外图像处理系统的实时性要求,提出了基于DSP+FPGA+ASIC的图像处理架构。

随着红外焦

2010-07-22 15:18:50 796

796 为了实现激光-水声浅海地形遥感探测中水声信号的实时解调与处理,本文提出了一种基于FPGA的激光多普勒测振计信号采集与处理系统的设计方案。以Cyclone Ⅱ系列FPGA为核心控制模块,结合

2013-10-29 10:10:02 2157

2157

采用以FPGA作为核心处理器实现了对多路DVI视频冗余信号的解码、编码实时处理以及输出显示,并且信号通道增加冗余设计,因而加强了系统的稳定性和可靠性。电路设计简洁,具有较强的灵活性和扩展性。通过实际

2014-03-25 15:03:55 2641

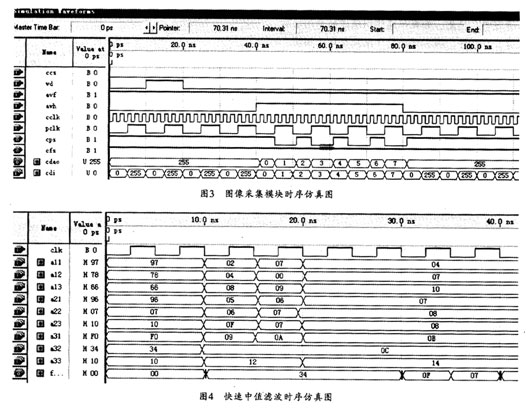

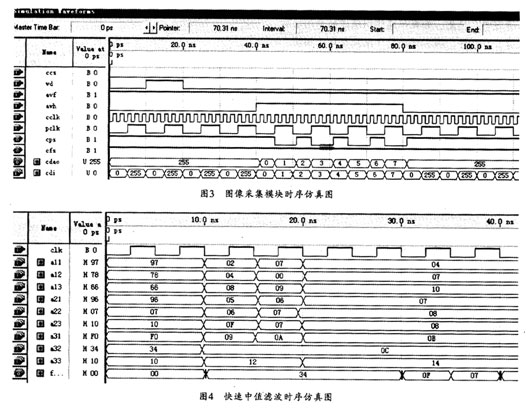

2641 设计了一种基于FPGA的实时视频图像采集处理电路系统。采用FPGA作为整个系统的控制和图像数据处理中心。DDR2 SDRAM为高速储存模块核心器件,CMOS 7670为视频图像采集器件。

2018-02-10 02:43:55 19311

19311

来说,滤除噪声、扩展对比度、锐化以及色彩增强等处理能显著提升视觉效果。这里设计一个基于FPGA的实时视频图像处理系统,包含增强对比度扩展和色饱和度两种处理方法,相比于DSP和ASIC方案来说,FPGA在性能和灵活性方面具有绝对优势,应用FPGA设计视频通信系统更普遍。

2019-08-22 08:22:29

什么是DSP图像处理系统?DSP图像处理系统中信号完整性的问题是什么?有哪些解决方案?

2021-06-01 06:40:35

系统整体方案及硬件设计 系统要求在FPGA片内利用SoPC技术实现便携式的图像采集与处理。它通过对原始图像的扫描,经数字图像处理与识别后即可将得到的大容量的承载信息(包括文字、头像、指纹等个人信息)在

2018-10-31 16:54:52

无法设计出具有自主知识产权的产品。随着网络技术、大规模,超太规模集成电路(ASIC)以及现场可编程门阵列(FPGA)的发展,它们在图像领域的应用越来越广泛,同时,图像处理设计也正朝着速度快、容量大、体积小、重量轻的方向发展,这也为图像处理系统的设计和实现提供了新的方法和思路。

2019-07-05 07:05:13

分享的是基于ARM和CPLD的嵌入式数字图像处理系统设计方案。嵌入式数字图像处理系统概述:本文介绍的是一种嵌入式数字图象处理平台的实现方案,通过ARM和CPLD技术,构造一个具有通用性、可扩充性、灵活

2019-12-10 17:55:03

本文以星载测控系统为背景,提出了一种基于 Actel Flash FPGA的高可靠设计方案。采用不易发生单粒子翻转的 flash FPGA芯片,结合 FPGA内部的改进型三模冗余、分区设计和降级重构,实现了高实时、高可靠的系统。

2021-05-10 06:58:47

为解决高速数字图像处理系统和实时性相冲突的要求,设计了以多DSP(数字信号处理器TMS320C6416)和现场可编程门阵列(FPGA)相结合的实时图像处理系统。重点介绍了该系统的硬件资源选择、基本组

2021-04-28 06:14:48

单片FPGA图像预处理系统的设计与实现采用单片FPGA设计与实现图像处理系统的方法,并对系统硬件进行了分析和设计,对FPGA内电路模块进行了VHDL建模,在FPGA开发平台ISE4.1上实现了

2009-09-19 09:26:14

图像数据处理的工作原理是什么?基于FPGA+DSP的图像处理系统待如何去设计?

2021-06-02 06:54:28

三维图像信息处理一直是图像视频处理领域的热点和难点,目前国内外成熟的三维信息处理系统不多,已有的系统主要依赖高性能通用PC完成图像采集、预处理、重建、构型等囊括底层和高层的处理工作。三维图像处理

2019-06-24 06:11:03

本系统采用基于FPGA与DSP协同工作进行视频处理的方案,实现视频采集、处理到传输的整个过程。 实时视频图像处理中,低层的预处理算法处理的数据量大,对处理速度要求高,但算法相对比较简单,适合于

2019-06-19 06:12:05

有自主知识产权的产品。随着网络技术、大规模,超太规模集成电路(ASIC)以及现场可编程门阵列(FPGA)的发展,它们在图像领域的应用越来越广泛,同时,图像处理设计也正朝着速度快、容量大、体积小、重量轻的方向发展,这也为图像处理系统的设计和实现提供了新的方法和思路。

2019-11-04 08:19:44

功能。其原理图如图4所示。综上基本内容电子论坛提出了一种基于FPGA技术的多路模拟量、数字量采集与处理系统,设计了相应的外围硬件电路和系统处理软件。在仿真和综合调试成功的基础上,本系统成功用于某重点预研项目的控制系统试验中。试验结果表明,本系统成功地完成了对多路模拟量、数字量的采集处理任务。

2011-08-23 10:15:34

本帖最后由 lee_st 于 2017-10-31 08:26 编辑

基于FPGA的视频图像处理系统

2017-10-30 17:26:16

基于FPGA的视频图像处理系统

2015-05-27 20:34:49

基于FPGA的视频图像处理系统。

2015-05-23 12:18:23

图像信息的获取和传输是图像处理系统的重要组成部分,直接影响图像处理系统的性能。

2019-10-17 07:30:20

基于fpga的实时视频处理系统难点在哪,解决方案,谁能帮下忙

2014-04-08 19:03:45

介绍了基于浮点DSP处理器与双CMOS头的数字图像采集处理系统,探讨了系统的基本原理和设计方法,并给出了系统的实现方案。在该系统中,数据采集由两个相互独立的CMOS摄像头完成,并由DSP进行图像处理

2014-11-05 14:44:51

基于DSP的图像处理系统的应用研究摘要 本文介绍了一种基于FPGA+DSP结构的具有通用性、可扩充性的高速数字图像处理系统硬件平台。重点介绍了以高速数字信号处理器TMS320DM642

2012-12-19 11:05:08

图像跟踪系统。一方面,采用双DSP体系结构实现系统任务的并行划分使本系统具备极高的运算处理速度;另一方面,现场可编程逻辑器件FPGA的引入使系统的灵活性也得到极大的提高。而将两者结合可使本系统充分体现新一代机载实时图像跟踪系统更快速、更精确、更灵活的特点。

2019-07-02 06:57:27

随着红外探测技术迅猛的发展,当今红外实时图像处理系统所要处理的数据量越来越大,速度要求也越来越快,利用目前主流的单DSP+ FPGA硬件架构进行较为复杂的图像处理算法运算时,有时就显得有些捉襟见肘了

2019-11-08 06:31:26

随着图像处理技术及传感器技术的不断发展,高清数字图像取代模拟图像成为一种趋势。设计了一种基于HD-SDI技术的高清图像处理系统,可通过FPGA+DSP架构对1080P全高清图像进行采集和字符叠加,并

2021-06-01 07:03:16

随着红外探测技术迅猛的发展,当今红外实时图像处理系统所要处理的数据量越来越大,速度要求也越来越快,利用目前主流的单DSP+ FPGA硬件架构进行较为复杂的图像处理算法运算时,有时就显得有些捉襟见肘了

2019-08-23 08:29:27

请问怎样去设计一种图像预处理系统?

2021-05-06 10:31:43

有偿求一份Xilinx的FPGA的图像采集和处理系统的代码,最好是你曾经做过的,别处下来的不能跑的不要。要能在开发板上跑动,我想做二次开发。联系企鹅:39 6 5 8 1 2 7 2{:23:}

2014-04-14 15:20:03

求一种多路模拟数字采集与处理系统的设计方案

2021-04-28 07:04:52

怎样去设计音频处理系统的硬件部分?怎样去设计音频处理系统的软件部分?

2021-06-02 06:50:18

传统的航空机载陀螺仪测试系统采用分立仪器搭建,具有成本高、自动化程度低、扩展性差的缺点,因此,这里提出一种基于虚拟仪器技术的航空机载陀螺仪自动测试系统的设计方案。

2021-05-11 06:15:04

浅谈大数据视频图像处理系统技术近年来,随着计算机、网络以及图像处理、传输技术的飞速发展,视频监控系统正向着高清化、智能化和网络化方向发展。视频监控系统的高清化、智能化和网络化为视频监控图像处理技术

2013-09-24 15:22:25

怎么设计一个基于FPGA的实时视频图像处理系统?

2021-05-06 08:21:45

介绍了一种用单片FPGA实现的实时、多任务、高速图像处理系统。该系统承担着提高信噪比、压缩数据量、Stokes参数观测和仪器及观测模式控制等任务。针对一个星载系统,采用了

2008-11-20 11:57:08 15

15 基于FPGA的小型微光视频图像增强处理系统Mini Low-level-light Video Image Enhancement Processing System Based on FPGA

摘要:为微光视频图像的实时增强设计了一套可应用于空间狭小环境中

2009-01-11 12:11:18 34

34 根据电力监控系统的要求,提出一种基于FPGA技术的多路交流信号采集与处理系统的设计方法。分析整个系统的结构,并讨论FPGA内部硬件资源的划分和软件的设计方案,以及各个功能

2009-05-16 14:47:58 27

27 介绍一种基于ADSP21060和Virtex II的星载图像处理系统。分析了图像处理系统的功能和任务,给出了处理系统的硬件结构、FPGA的功能模块、DSP的软件框架和模块。通过地面原理样机开发

2010-07-16 15:14:20 15

15 本文设计方案仿生眼嵌入式机载视频图像处理系统使用ti公司tms320dm642高性能数字多媒体处理器作为核心处理器,系统解决方案了实时收集图像,实时处理图像,实时输出目标资料,

2010-09-10 10:17:46 33

33 为解决机载高分辨率图像的实时压缩问题,提出了一个基于FPGA+PowerPC的高分辨率图像实时压缩系统的设计方案。本系统主控采用PowerPC 处理器,压缩芯片采用ADV202,用FPGA实现图像数

2010-09-15 11:45:25 40

40 摘要:提出一种基于FPGA技术的多路模拟量、数字量采集与处理系统的设计方案,分析整个系统的结构,并讨论FPGA内部硬件资源的划分和软件的设计方案等。本设计

2009-06-20 15:05:11 1543

1543 基于FPGA玻璃缺陷图像采集处理系统

引 言 玻璃缺陷检测是玻璃生产过程中一个相当重要课题。玻璃缺陷(气泡、结石、锡点等)妨碍了它在重大技术

2009-11-13 09:53:08 670

670

基于FPGA的远程图像采集系统设计

图像信息的获取和传输是图像处理系统的重要组成部分,直接影响图像处理系统的性能。图像信息的采集包括对图

2009-11-23 21:03:25 1177

1177

基于双DSP的实时图像处理系统

介绍了基于双DSP的实时图像处理系统。该系统通过两片TMS320C6201作为系统计算中心,通过可重构成的FPGA计算系统获得系

2009-12-08 14:25:35 1009

1009

基于DSP+FPGA+ASIC的实时图像处理系统

1.引言

随着红外焦平面阵列技术的快速发展,红外成像系统实现了高帧频、高分辨率、高可靠性及微型化,在目标跟踪

2010-01-13 10:39:49 1115

1115

基于FPGA和MB86S02的数字图像处理系统设计

0引言图像处理技术是信息科学中近十年来发展最为迅速的学科之一。目前,数字图像处理技术巳被广泛应用于航空航天

2010-02-04 09:59:50 981

981

摘要:以开发的实际系统为背景,论述了基于PCI总线和DSP的实时图像采集与处理系统的硬件及软件设计方案和实现方法。系统以数字CCD相机为图像采集设备,利用PCI总线的高速数据传输能力和DSP强大的数据处理能力,实现了图像的实时采集、处理和传输。 关键词:C

2011-02-25 23:24:41 40

40 本文设计了基于FPGA的LCoS驱动代码及图像的FFT变换系统,为计算全息三维显示图像处理和显示提供了硬件平台

2011-06-28 09:36:46 1824

1824

文中在介绍DDR2的工作原理的基础上,给出了一个用VHDL语言设计的DDR2 SDRAM控制器的方法,并且提出了一种在高速图像处理系统中DDR2 SDRAM的应用方案,同时在Virtex-5系列的FPGA上得到了实现

2011-07-23 10:03:16 5102

5102 介绍了一种用于数字化双功能多普勒超声成像仪中以单片FPGA 实现的实时、多任务、高速信号处理系统,该系统承担着动态滤波、多普勒解调、包络检波、FFT 变换、数据压缩、数据选通等

2011-09-14 15:18:43 143

143 针对图像处理要求运行复杂灵活的图像处理算法和大数据量的数据传输处理的要求,提出了一种基于DSP和FPGA架构的嵌入式图像处理系统,简要介绍了系统的工作原理,详细介绍了系统硬

2011-12-05 14:12:28 62

62 本文介绍了一种基于FPGA的网络图像处理系统设计和实现方法。系统主要包括图像采集模块、RAM控制模块、JPEG编码器3部分逻辑。在单片FPGA上实现图像的采集、裁剪、缓存和JPEG编码,构建

2012-02-08 14:41:59 1731

1731

基于FPGA的雷达信号处理系统设计的论文

2015-10-30 10:38:12 6

6 基于FPGA的视频后处理系统--的技术论文

2015-10-30 10:38:26 0

0 基于FPGA的嵌入式图像处理系统设计基于FPGA的嵌入式图像处理系统设计

2015-11-04 16:31:54 3

3 机载图像无损近无损压缩方案及其FPGA实现

2016-08-29 15:02:03 5

5 基于FPGA的玻璃缺陷图像采集预处理系统设计

2016-08-30 15:10:14 13

13 一种基于FPGA和PCI总线的天文图像实时采集与处理系统的设计,感兴趣的小伙伴们可以看一看。

2016-09-14 17:17:07 8

8 一种CCD图像相关处理系统的FPGADSP实现,感兴趣的小伙伴们可以看一看。

2016-09-14 17:17:07 25

25 基于FPGA+DSP实时图像采集处理系统设计

2017-01-03 11:41:35 9

9 高效机载SAR实时成像处理系统设计_杨磊

2017-01-07 16:00:43 1

1 基于FPGA的视频图像处理系统设计_李莲

2017-03-19 11:38:26 21

21 基于双DSP和双FPGA的高速图像处理系统设计_吴雷

2017-03-16 09:28:51 2

2 基于FPGA的软硬件协同实时纸病图像处理系统_齐璐

2017-03-19 19:07:17 0

0 、便携性等是目前该领域研究的重要课题。高速大容量低功耗FPGA的出现,为电子内窥镜图像处理系统的设计提供了新的思路和方案。本文以Actel独特的低功耗Flash FPGA芯片为核心,对电子内窥镜图像处理系统进行研究和设计。

2017-08-31 08:57:24 11

11 图像处理技术是信息科学中近几十年来发展最为迅速的学科之一.目前,数字图像处理技术被广泛应用于航空航体、通信、医学及工业生产领域中。图像处理系统的硬件实现一般来讲有三种方式:专用的图像处理器件主要有

2017-08-31 10:37:24 12

12 基于FPGA和DSP的高速图像处理系统

2017-10-19 13:43:31 19

19 基于DSP和FPGA的模块化实时图像处理系统设计

2017-10-23 14:09:42 9

9 所处理的数据量少,算法结构复杂,适于运算速度快,寻址灵活的DSP数字信号处理器进行处理。这里提出了一种FPGA+DSP相结合的实时图像处理系统,并应用于传像光线束传递图像。CMOS实际采集的是光线束的出端图像,FPGA将CMOS采集的Bayer格式的

2017-10-26 15:44:56 2

2 随着红外探测技术迅猛的发展,当今红外实时图像处理系统所要处理的数据量越来越大,速度要求也越来越快,利用目前主流的单DSP+ FPGA硬件架构进行较为复杂的图像处理算法运算时,有时就显得有些捉襟见肘

2017-10-31 11:02:41 0

0 本文提出了一种实时图像采集和处理系统的设计方法,该系统以TMS320DM642[1-2]为核心,结合视频解码芯片SAA7115H和OSD FPGA构成实时图像采集和处理系统电路。 1 系统总体设计

2017-10-31 16:56:33 7

7 所处理的数据量少,算法结构复杂,适于运算速度快,寻址灵活的DSP数字信号处理器进行处理。这里提出了一种FPGA+DSP相结合的实时图像处理系统,并应用于传像光线束传递图像。CMOS实际采集的是光线束的出端图像,FPGA将CMOS采集的Bayer格式的

2017-10-31 17:00:34 12

12 为解决高速数字图像处理系统和实时性相冲突的要求,设计了以多DSP(数字信号处理器TMS320C6416)和现场可编程门阵列(FPGA)相结合的实时图像处理系统。重点介绍了该系统的硬件资源选择、基本组

2017-11-18 12:34:02 4034

4034

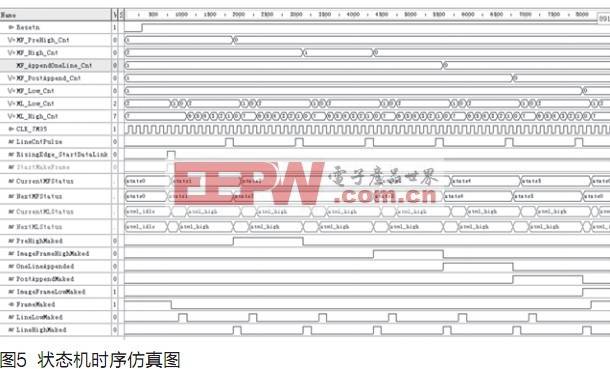

通过研究视频图像处理和视频图像帧格式以及FIF0缓存技术,提出了基于FPGA的视频图像处理系统设计。该设计运用帧间差分法、同步FIF0缓存设计,有效避免了图像处理系统设计中亚稳态和异步信号处理等时序

2017-11-22 09:13:03 4629

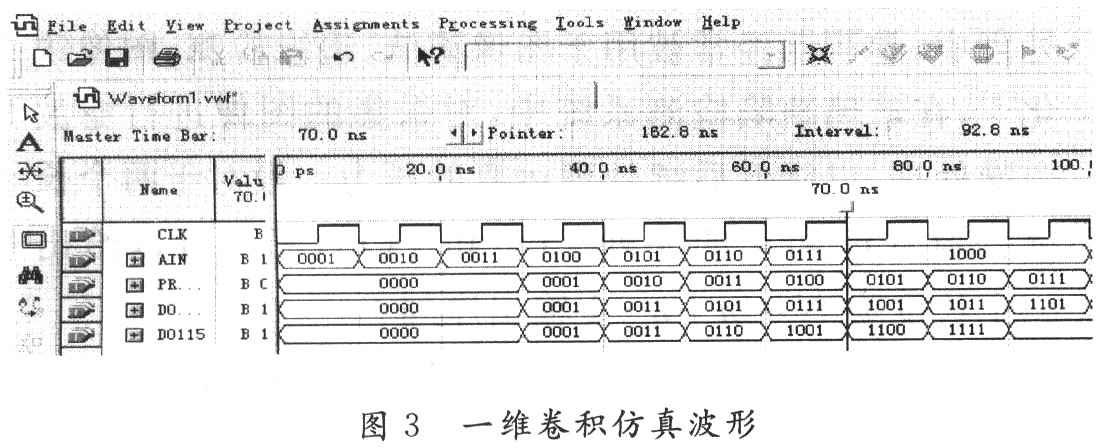

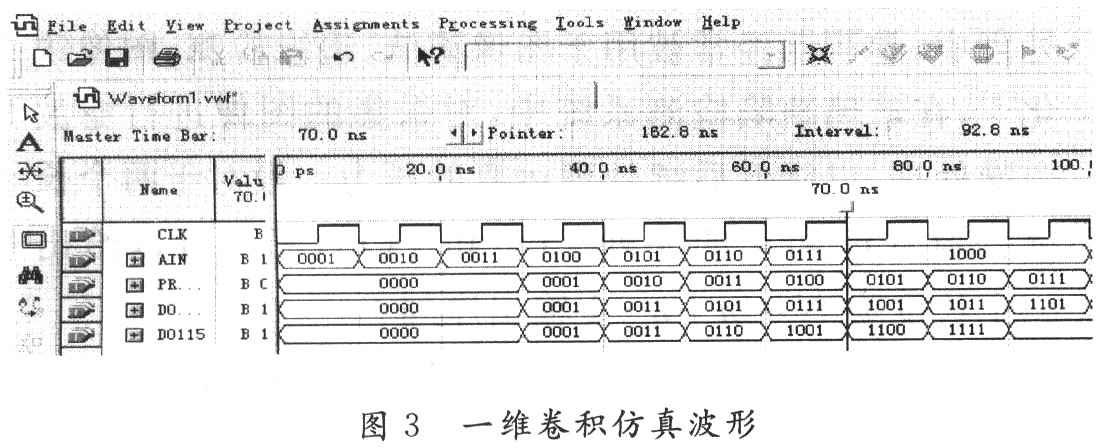

4629 缺陷在线检测系统方案,利用FPGA 实时、高速、可重构的特点,并对玻璃缺陷图像进行的预处理(卷积运算),从而大大降低了后期数据处理的压力,使得图像处理系统运算速度快,具有很好的适应性。

2018-07-16 11:48:00 788

788

结合系统需求,确定系统的总体设计方案为:以Xilinx公司的Virtex-5 XC5VFX70T FPGA为核心处理器,利用其强大逻辑资源和丰富的IP核,配以相应的外部电路,构建出一个灵活、简洁

2018-08-18 09:53:16 2075

2075

提出一种基于FPGA技术的多路模拟量、数字量采集与处理系统的设计方案,分析整个系统的结构,并讨论FPGA内部硬件资源的划分和软件的设计方案等。本设计方案外部电路结构简单可靠,特别适用于多路检测系统中,而且可以根据需要容易地对系统进行扩展,对于检测系统来讲具有一定的通用性

2018-09-07 15:39:25 13

13 介绍了一种用单片FPGA实现的实时、多任务、高速图像处理系统。该系统承担着提高信噪比、压缩数据量、Stokes参数观测和仪器及观测模式控制等任务。针对一个星载系统,采用了核心逻辑片内冗余、设计了相应

2018-09-21 17:00:26 6

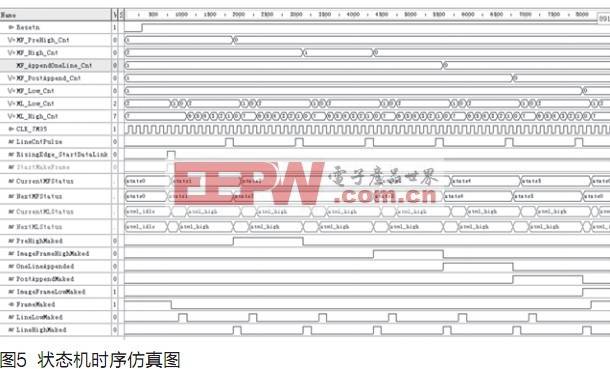

6 介绍了一种基于FPGA的高速多路数据采集系统的设计方案,描述了系统的主要组成及FPGA的实现方法,并用v∞L语言设计的状态杌在Qmr啮Ⅱ开发软件中进行仿真。该系统在通用数据采集系统的基础上,增加数

2018-10-12 16:15:09 13

13 构建数字视频图像处理系统的优势:,4、设计实例:基于FPGA的MPEG4AVC/H.264视频编码器核心算法;,5、设计基于FPGA高速数字信号处理系统的技巧

2019-03-29 16:53:50 15

15 提出了一种基于FPGA的实时、多分辨率图像采集系统的控制逻辑设计方案;并对其中的图像数据预处理和帧存乒乓刷新机制这两个关键技术进行了阐述;为了验证图像采集系统在整个图像处理系统中所起的作用,还对图像

2021-02-03 14:46:00 9

9 为解决机载高分辨率图像的实时压缩问题,提出了一个基于FPGA+PowerPC的高分辨率图像实时压缩系统的设计方案。本系统主控采用PowerPC处理器,压缩芯片采用ADV202,用FPGA实现图像数据流程中各个环节控制,最终输出数据为高性能的静止图像压缩标准JPEG2000格式。

2021-02-05 15:22:49 8

8 ,使用~tera的Quartus II软件,完成了其中的核心模块——F盯算法的硬件实现,提高了处理速度;并运用DSP处理器,设计了一个基于FPGA的实时数字图像处理系统.文中给出了系统的硬件电路和软件算法模块.仿真和调试结果表明:用FPGA与高速数字信

2021-02-05 15:54:00 139

139 基于FPGA的嵌入式信号处理系统设计方案

2021-06-02 11:04:33 0

0 基于FPGA的嵌入式信号处理系统设计方案

2021-06-02 11:04:33 0

0 嵌入式图像处理系统的设计与实现(嵌入式开发需要学哪些算法)-文档为嵌入式图像处理系统的设计与实现总结文档,是一份不错的参考资料,感兴趣的可以下载看看,,,,,,,,,,,,,

2021-08-04 15:19:18 9

9 图像处理系统设计注意点:1.将算法开发和FPGA实现分离用软件的图像处理环境可以使用大批量的图像样本进行测试及调试算法,再将算法映射到硬件上,这样大大节省了硬件调试周期。 2.算法的精度图像

2023-03-21 19:40:02 377

377

正在加载...

电子发烧友App

电子发烧友App

评论