多道脉冲幅度分析器不仅能自动获取能谱数据,而且一次测量就能得到整个能谱,因此可大大减少数据采集时间,与此同时,其测量精度也显着提高。自从20世纪50年代以来,

2010-09-25 09:26:13 2083

2083

为了研究数字化γ能谱仪,本文提出一种基于FPGA的数字核脉冲分析器硬件设计方案,该方案采用现场可编程逻辑部件(FPGA),完成数字多道脉冲幅度分析仪的硬件设计。用QuartusⅡ软件在FPGA平台上完成了数字核脉冲的幅度提取并生成能谱。

2013-11-21 10:57:26 1948

1948

基于FPGA 的数字核脉冲分析器硬件设计方案,该方案采用现场可编程逻辑部件(FPGA),完成数字多道脉冲幅度分析仪的硬件设计。

2015-02-03 09:55:05 1870

1870

1645A数据错误分析器操作和维护手册

2018-12-06 16:19:57

16500C逻辑分析系统的状态和时序分析器

2019-02-28 13:26:11

我用的是xinlinx spartan6 FPGA,我想知道它的IP核RAM是与FPGA独立的,只是集成在了一起呢,还是占用了FPGA的资源来形成一个RAM?如果我以ROM的形式调用该IP核,在

2013-01-10 17:19:11

,整板硬件包括FPGA电路, DDR3电路,外围接口电路,加上时钟和控制逻辑等辅助电路,形成一个完整的、一体化的数字系统硬件平台。能够快速接入FC-AE网络,实现光纤总线终端的数据通讯。课程提供项目

2021-11-17 23:12:06

转成电路连接,从最基本的逻辑门层面上连接成电路(参见数字电路书上那些全加器触发器什么的)。应该说,虽然看起来像一块CPU,其实是完全硬件实现的。后来因为写代码麻烦,对控制部分比较薄弱,本来跟其他CPU

2020-10-22 11:28:52

如题,小弟最近做一个用FPGA驱动电机的板子,用STM32把FPGA需要发出的脉冲的宽度和个数都计算好,然后用8位的并口,通过一个时钟上升沿写进FPGA,在FPGA内部进行运算之后发出脉冲,刚开始

2019-01-28 00:41:02

分析了抖动偏频激光陀螺信号的解调原理,提出了一种利用数字信号处理技术并采用FPGA实现的抖动解调方法;通过对激光陀螺脉冲计数值高速采样并采用数字滤波器滤波处理,可以有效消除抖动引起的信号噪声,得到

2018-08-30 09:21:12

, 节约将近90% 的逻辑资源。 软核(Soft IP Core) : 软核在EDA 设计领域指的是综合之前的寄存器传输级(RTL) 模型;具体在FPGA 设计中指的是对电路的硬件语言描述,包括逻辑描述

2018-09-03 11:03:27

数据传输效率低,这将严重影响产品的性能;而如果采用高速并口,则占用管脚多,硬件成本将会增加。为解决这一痛点,各大芯片公司陆续推出了兼具A核和M核的多核异构处理器,如NXP的i.MX8系列、瑞萨的RZ

2022-11-23 15:09:45

B4620A软件分析器工具集

2019-03-18 16:53:37

,LED在PIC32芯片上被点亮,这表明它正在运行,但是在MCP2515上没有LED灯,这是正常的吗?而且,我发现CAN分析器不接收PIC32发送的测试消息,这表明CAN分析仪和MCP2515

2020-03-26 10:45:52

专家好,

CCS调试程序过程中,需要分析下各函数的执行时间,CCS中提供了性能分析器profile

Q1:性能分析器profile是否只能在Simulator下才能使用,Emulator下没有这个功能?

Q2:性能分析器profile的使用方法是否有相应的教程参考?

谢谢

NanShan

2018-06-21 19:20:12

我使用的是Microchip CAN总线分析仪,版本2.3软件。我用最新的固件对这两个UC进行了编程。我正在运行一个1MIT的CAN网络,分析器似乎丢失/混淆了消息。请参阅附加屏幕截图。注意,有时

2018-10-09 11:05:18

OmniBER OTN 2.5 Gb/s通信性能分析器

2019-07-10 16:45:53

OmniBER OTN J7230B 10G通信性能分析器,配置指南

2019-09-03 07:07:28

技术10.4.2 基于FPGA的千兆以太网MAC控制器实现方案10.4.3 Xilinx 千兆以太网MAC IP Core10.5 本章小结第11章时序分析原理以及时序分析器的使用11.1 时序分析的作用

2012-04-24 09:23:33

项目名称:FPGA上的处理器核原型设计试用计划:申请理由及项目计划:本人西安某高校学生,对数字IC感兴趣,学习过FPGA与处理器相关知识,用过quartus和vivado,ISE,看过水头一寿

2017-07-25 18:02:36

国内谱仪技术多年来一直停留在模拟技术水平上,数字化能谱测量技术仍处于方法研究阶段。为了满足不断增长的高性能能谱仪需求,迫切需要研制一种数字化γ能谱仪。通过核脉冲分析仪显示在显示器上的核能谱帮助人们了解核物质的放射性的程度。

2019-07-03 07:35:52

主流四核移动处理器解析

2012-08-20 13:01:36

刚刚接触antlr词法分析器只略看了些基本理论知识,关于做实例就完全不懂了,我想知道他需要什么样的环境和软件,以及软件的下载地址.多谢各位了

2014-11-12 16:29:39

分享一个好的工具 单片机C语言流程图分析器,可以分析整理程序的流程对看懂别人的程序非常管用!

2014-02-08 14:45:59

描述Pico NWT–贫穷无线电爱好者分析仪到了21世纪,你家里还没有NWT吗?这个项目的目标是创建一个尽可能简单的RF分析器。它的设计和调整非常简单,即使是初学者也可以使用,应用的零件可以在任

2022-08-02 06:11:06

反应堆仪表和控制系统(I&C)的数字化发展方向成为趋势,反应堆堆外核测量系统的数字化势在必行。传统脉冲周期监测装置通常采用模拟电路设计,但是,周期测量稳定性较差,统计涨落带来的测量误差较大

2011-03-04 16:49:54

嗨,我们正在尝试使用Vivado工具链手动路由FPGA,并想知道应该使用什么工具来手动路由Virtex 7 FPGA。还可以在Vivado时序分析器工具中指定温度和电压值来估算设计时序吗?我们将如

2018-10-25 15:20:50

图形分析器是一个帮助OpenGL ES和Vulkan开发人员通过API级别的分析来充分利用其应用程序的工具。

该工具允许您观察API调用参数和返回值,并与正在运行的目标应用程序交互,以调查单个API

2023-08-09 06:08:14

描述图形音频分析器 16x32

2022-08-24 06:38:03

,减少了硬件资源的占用。该方案在Cyclone II FPGA 芯片EP2C35F484 上实现,占用 20 070 个逻辑单元(少于60% 的资源),系统最高时钟达到100 MHz 。与传统的128 位数据路径设计相比,更方便与处理器进行接口。

2012-08-11 11:53:10

基于FPGA的数字脉冲压缩技术1.数字脉冲压缩实现原理2.电路设计2.1APEX2OKE系列FPGA 简介2.2 基于FPGA 的算法研究及实现 2.3 脉冲压缩在FPGA 上的实现

2011-03-02 09:41:50

使用。 本文基于快速傅里叶IP核可复用和重配置的特点,实现一种频域的FPGA数字脉压处理器,能够完成正交输入的可变点LFM信号脉冲压缩,具有设计灵活,调试方便,可扩展性强的特点。 1 系统功能硬件

2018-11-09 15:53:22

中从电子设计的外围器件逐渐演变为数字系统的核心。伴随着半导体工艺技术的进步,FPGA器件的设计技术取得了飞跃发展及突破。分频器通常用来对某个给定的时钟频率进行分频,以得到所需的时钟频率。在设计数字

2019-10-08 10:08:10

此提供了新的解决方案。IP核(IP Core)是具有特定电路功能的硬件描述语言程序,可较方便地进行修改和定制,以提高设计效率[3]。本文研究了基于FPGA的数据采集控制器IP 核的设计方案和实现方法,该IP核既可以应用在独立IC芯片上,还可作为合成系统的子模块直接调用,实现IP核的复用。

2019-07-09 07:23:09

Programmable Gate Array,现场可编程门阵列)基于查找表的结构和全硬件并行执行的特性,如何用FPGA 来实现高速FIR 数字滤波器成了近年来数字信号处理领域研究的热点。目前,全球两大PLD 器件供应商都提供了加速FPGA 开发的IP(IntelligentProperty,知识产权)核。

2019-09-05 07:21:15

,不同的寄存器在时钟脉冲的激励下相互配合完成特定的功能,所以要保证不同的寄存器在同一时刻的时钟脉冲激励下协同工作,就需要进行时序分析,通过分析得结果对FPGA进行约束,以保证不同寄存器间的时序要求

2017-02-26 09:42:48

有什么方法可以使用从 cubeIDE 中的 IAR Eclipse 插件生成的 MAP 文件来构建分析器吗?

2022-12-27 06:26:38

本文利用先进的EDA软件,用VHDL硬件描述语言采用自顶向下的模块化设计方法,完成了具有相序自适应功能的双脉冲数字移相触发器的IP软核设计。

2021-04-28 06:39:00

亲爱的大家,我使用的是MPLABX3.13的IDE。在分析器中使用PWM模拟器时,我可以在分析器屏幕上获得PWM波形。但是我不知道如何在分析器窗口进行以下设置:1。如何设置PWM脉冲的NO在X轴上

2019-09-20 08:36:02

多道脉冲幅度分析器结构由那几部组成基于LPC2134的多道脉冲幅度分析器设计

2021-04-09 06:44:29

现在需要做1nS脉冲发生器,FPGA可以做出来吗?1,据说FPGA主频达不到1GHz,那通过PLL或MCMM可以吗?如果主频到了,FPGA的普通IO口可以胜任这么高频吗?2,可不可以用FPGA内部

2018-03-05 20:03:59

现在需要做1nS脉冲发生器,FPGA可以做出来吗?1,据说FPGA主频达不到1GHz,那通过PLL或MCMM可以吗?如果主频到了,FPGA的普通IO口可以胜任这么高频吗?2,可不可以用FPGA内部

2021-09-10 10:39:13

我无法弄清楚这一点,所以我希望你能提供帮助。在频谱分析仪上,我可以保存迹线,然后在仪器上调用它,并使用标记进行一些后期分析。我无法破解有关如何使用网络分析器执行此操作的代码。任何帮助,将不

2018-09-26 15:09:26

dimond抓取内部信号工具有:插入器,分析器。插入器生产后缀文件为rvl,分析器后缀为rva。FPGA每次断电后,需要重拔插USB 口才可烧写(软件bug)。FPGA每次断电后,需要找到对应文件夹

2018-12-03 09:00:37

核的分类和特点有哪些?在FPGA设计中的核分为哪几种?核基FPGA是如何设计的?软核的设计及使用是什么?

2021-04-14 06:25:39

我可以将EVSPIN32F0251S1与电机分析器一起使用吗?

2023-01-05 07:14:55

多道脉冲幅度分析器的结构是怎样设计的?多道脉冲幅度分析器的硬件是如何设计的?怎样去设计多道脉冲幅度分析器的相关软件?怎样对多道脉冲幅度分析器的硬件电路进行仿真测试?

2021-04-14 06:31:11

提出了采用Verilog HDL 设计I2C 总线分析器的方法,该I2C 总线分析器支持三种不同的工作模式:被动、主机和从机模式,并提供了嵌入式系统设计接口。通过硬件总体框架分析,分

2009-08-10 15:32:18 40

40 VPGE(Visual Parser Generation Environment)是一个可视化语法分析器集成开发环境,除了具有良好的界面和强大的调试功能,其LALR(1)分析器的生成速度达到并超过公认的分析器生成速度最快

2009-08-29 10:04:13 16

16 Rosemount分析器基于Raman的激光技术,在对二甲苯纯化过程中通过减少给料的变化,帮助工厂达到99.7%的产品纯度。本文中的案例讲述了如何在生产线中应用Raman分析器

2009-12-08 16:39:33 11

11 HG/T20516-2000自动分析器室设计规定

本规定适用于化工装置自动分析器室的设计。执行本规定时,尚应符合国家现行的有关标准的规定。

2010-02-24 14:25:51 7

7 转换到TimeQuest时序分析器教程(电子书)

2010-03-23 16:49:43 0

0 本文介绍一种采用电池供电的ADc和袖珍计算机Pc一1500通过接口电路组成的256道脉冲幅度分析器。其分析范围为0.1—5V,微分非线性好于±2.5%,耗电约180mw,连续工作24小时道位漂移不

2010-05-19 09:12:18 30

30 摘要:通过对高精度脉冲幅度分析器的电路分析,得出了在使用过程中,采用高精度和低温系数的电压基准集成块,可保证该脉冲幅度分析器比传统脉冲幅度分析器灵敏度高、稳定

2010-05-25 08:39:59 29

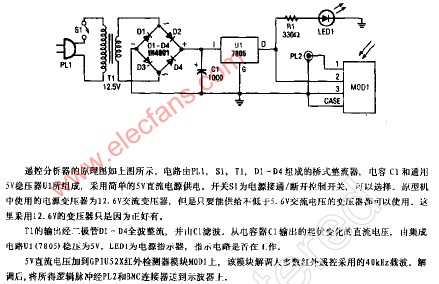

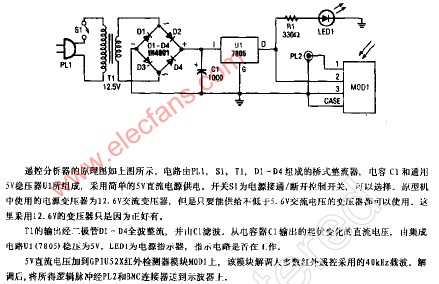

29 遥控分析器

2009-09-18 14:14:38 456

456

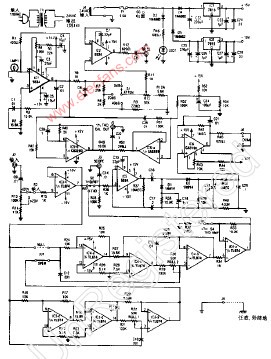

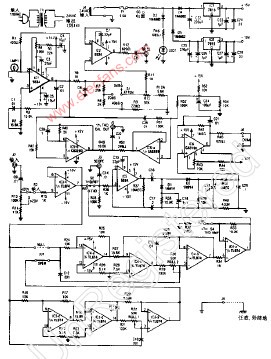

谐波失真分析器

电路包括一个1KHZ的低失真

2009-09-23 14:34:24 757

757

网络分析器,网络分析器原理是什么?

网络分析器

具有发现并解决各种故障特性的硬件或软件设备

2010-03-22 11:25:21 993

993 协议分析器在WLAN中的应用

协议分析器广泛应用于有线网络,成为一类极有用的测试和维护工具。然而,在WLAN领域,这个问题很有可

2010-03-29 17:11:30 483

483 虚拟声谱分析器软件详细介绍 此软件操作方便快捷

2011-02-11 15:53:54 97

97 摘要:介绍一种以数字信号处理器(DSP)为核心的多道脉冲幅度分析器,它能够进行核信号的采集\处理以及传输,然后经过上位机的处理实现对射线的能量和强度的分析.DSP的采用保证了信号处理的实时性. 关键词:DSP MCA A/D转换 D/A转换 探测器 高压

2011-02-27 13:33:23 34

34 Fortify的静态代码分析器(Static Code Analyzer,SCA)是组成Fortify 360的三个分析器之一。SCA工作在开发阶段,以用于分析应用程序的源代码是否存在安全漏洞。这种类型的分析与程序跟踪分析

2011-04-07 20:32:46 22

22 用大多数FPGA都可以实现一个数字UWB(超宽带)脉冲发生器。本设计可以创建一个两倍于FPGA时钟频率的脉冲信号(

2011-09-06 11:59:48 5280

5280

多道脉冲幅度分析器不仅能自动获取能谱数据,而且一次测量就能得到整个能谱,因此可大大减少数据采集时间,与此同时,其测量精度也显着提高。

2011-10-13 12:01:13 4325

4325

本文将重点介绍“交换端口分析器(SPAN)”的工作原理及配置方法。

2012-02-03 14:09:03 909

909 电子发烧友网: 本文主要分析了多道脉冲幅度分析器忙时间的形成特点,设计出来一套能减小系统忙时间的方案,从而大大地减少由于忙时间造成的脉冲漏计数。同时分析了改进后系统

2012-06-11 08:47:26 37

37 电感储能型脉冲电源系统的半解析参数分析_丁健民

2017-01-04 16:45:45 0

0 基于LPC1764的多道脉冲幅度分析器的电路设计

2017-09-25 11:45:51 4

4 基于CPLD_ARM的多道脉冲幅度分析器设计

2017-09-25 12:55:06 8

8 核分析能谱测量所用的多道脉冲幅度分析器,在进行模数转换时需要一定的时间,会使分析器产生漏计数,给测量分析带来误差,需要对死时间进行修正。针对这种情况,探讨了两种有效的死时间修正方法。核分析能谱测量

2018-04-09 11:11:45 12

12 本文介绍一种采用电池供电的ADC和袖珍计算机PC-1500通过接口电路组成的256道脉冲幅度分析器。

2018-04-09 11:19:24 9

9 针对当前对多道脉冲幅度分析器的高处理速度、高集成度、友好人机交互的要求,采用三星公司生产的S3C2410芯片设计并实现了一种便携式的核数据采集系统设计方案。对传统的多道脉冲幅度分析器进行改进和简化

2018-04-09 11:51:32 6

6 英特尔®图形性能分析器的Geometry Viewer快速提示

2018-11-12 06:48:00 2579

2579 Seth为DirectX提供了图形帧分析器。

了解这款功能强大的分析仪的基本特性和功能。

2018-11-12 06:35:00 1838

1838 Seth为OpenGL提供了图形帧分析器。

了解这款功能强大的分析仪的基本特性和功能。

2018-11-09 06:25:00 2597

2597 在英特尔®视频专业分析器中预览易于使用的GUI:

2018-11-09 06:07:00 1803

1803 Seth提供图形监视器,系统分析器和HUD。

这些组件构成了英特尔图形性能分析器中的实时分析工具。

2018-11-07 06:53:00 4770

4770 英特尔®跟踪分析器中新的性能助理图表概述。

2018-11-07 06:15:00 2239

2239 开源网络协议分析器WireShark软件下载

2021-07-23 09:22:08 14

14 电子发烧友网站提供《图形音频分析器开源设计.zip》资料免费下载

2022-08-02 15:18:04 0

0 如您所知,HostMonitor能够将测试结果记录到日志文件中。日志分析器是一个可视化日志数据的图形工具。它解析日志文件的内容并将数据呈现为各种图表,代表不同的测试统计数据。

2022-08-24 15:19:37 811

811 实时数据分析器用户手册 产品规格书.实时数据分析器是,可应用生产现场的数据执行离线分析与实时诊断的边缘应用程序。

2022-08-26 11:50:34 0

0 LogAnalyzer(日志分析器)是HostMonitor的一个辅助应用程序,它包含在高级主机监视器软件包中。

2022-09-14 09:56:39 1561

1561 LogAnalyzer(日志分析器)是HostMonitor的一个辅助应用程序,它包含在高级主机监视器软件包中。

2022-10-13 15:42:31 1232

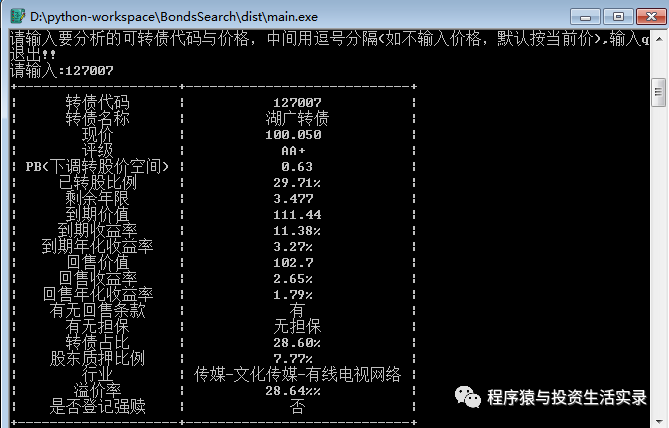

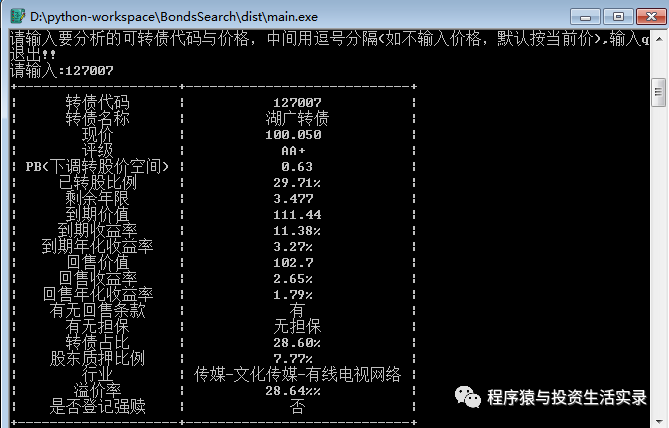

1232 用Python写个可转债分析器

2023-02-16 15:13:00 909

909

转换器分析器用户指南

2023-04-27 18:48:01 0

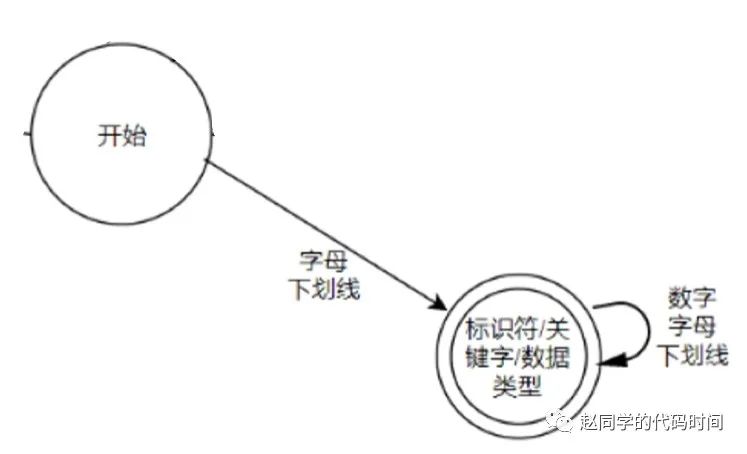

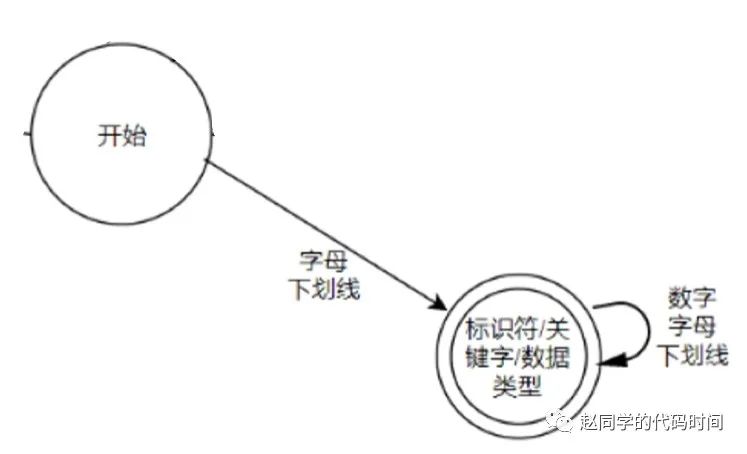

0 在开始手写词法分析器之前呢,我们得先准备好一些零件,规划好将要使用哪些函数,如果函数没有现成的,那还得自己写。

2023-05-23 11:20:58 514

514

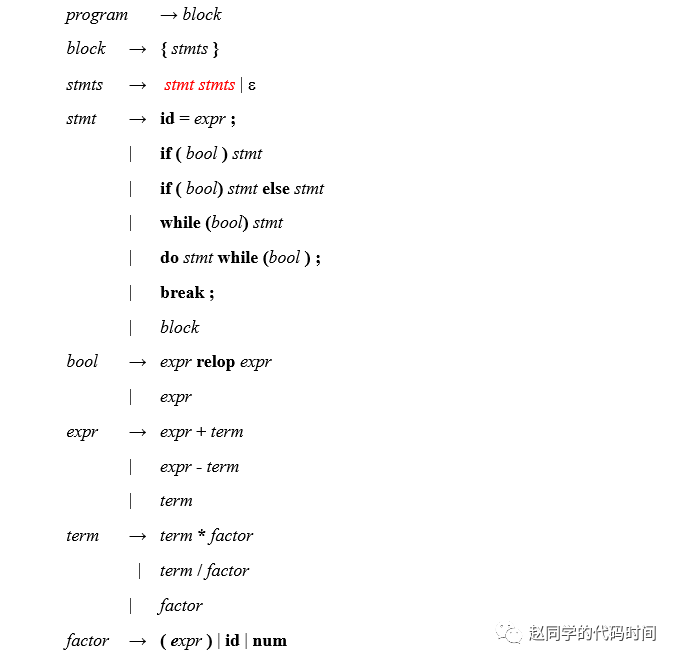

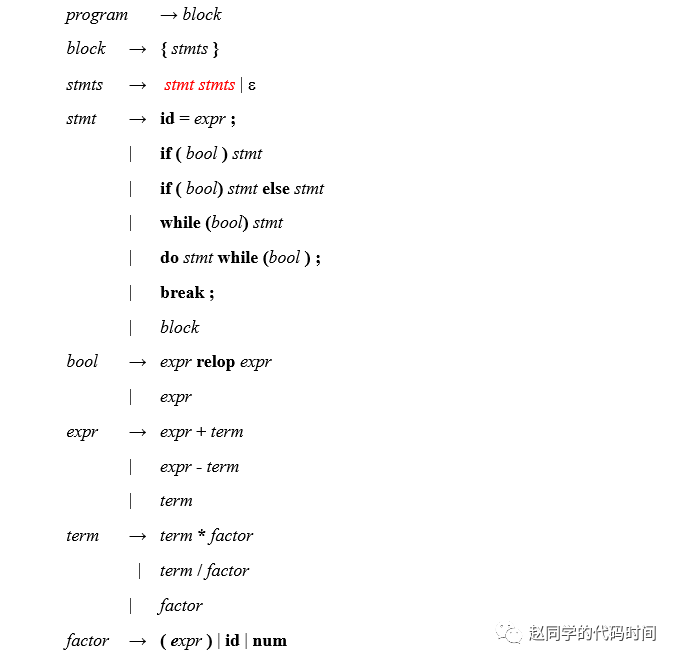

在之前已经通过手写的方式实现了一个词法分析器,现在,我将利用之前手写的词法分析器,使用递归下降的方式,实现一个简单的语法分析器。

2023-05-23 11:24:02 1451

1451

正在加载...

电子发烧友App

电子发烧友App

评论