表。 这4类路径中,我们最为关心是②的同步时序路径,也就是FPGA内部的时序逻辑。 时序模型 典型的时序模型如下图所示,一个完整的时序路径包括源时钟路径、数据路径和目的时钟路径,也可以表示为触发器+组合逻辑+触发器的模型。 该

2020-11-17 16:41:52 2768

2768

约束流程 说到FPGA时序约束的流程,不同的公司可能有些不一样。反正条条大路通罗马,找到一种适合自己的就行了。从系统上来看,同步时序约束可以分为系统同步与源同步两大类。简单点来说,系统同步

2020-11-20 14:44:52 6859

6859

在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是一个重点。只有约束正确才能在高速情况下保证FPGA和外部器件通信正确。

2022-09-27 09:56:09 1382

1382 计算和分析。同时,时序和信号完整性也是密不可分的,良好的信号质量是确保稳定的时序的关键,由于反射,串扰造成的信号质量问题都很可能带来时序的偏移和紊乱。因此,对于一个信号完整性工程师来说,如果不懂得系统

2022-12-13 10:50:35 1955

1955

FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间。

2023-06-06 17:53:07 860

860

在FPGA设计中,时序约束的设置对于电路性能和可靠性都至关重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的基础知识。

2023-06-06 18:27:13 6213

6213

在FPGA设计中,时序约束对于电路性能和可靠性非常重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的主时钟约束。

2023-06-12 17:29:21 1230

1230 前面几篇FPGA时序约束进阶篇,介绍了常用主时钟约束、衍生时钟约束、时钟分组约束的设置,接下来介绍一下常用的另外两个时序约束语法“伪路径”和“多周期路径”。

2023-06-12 17:33:53 868

868 关键路径通常是指同步逻辑电路中,组合逻辑时延最大的路径(这里我认为还需要加上布线的延迟),也就是说关键路径是对设计性能起决定性影响的时序路径。

2023-06-21 14:14:16 1220

1220

今天跟大家分享的内容很重要,也是调试FPGA经验的总结。随着FPGA对时序和性能的要求越来越高,高频率、大位宽的设计越来越多。在调试这些FPGA样机时,需要从写代码时就要小心谨慎,否则写出来的代码

2023-08-01 09:18:34 1041

1041

FPGA中时序约束是设计的关键点之一,准确的时钟约束有利于代码功能的完整呈现。进行时序约束,让软件布局布线后的电路能够满足使用的要求。

2023-08-14 17:49:55 712

712

时序路径作为时序约束和时序分析的物理连接关系,可分为片间路径和片内路径。

2023-08-14 17:50:02 452

452

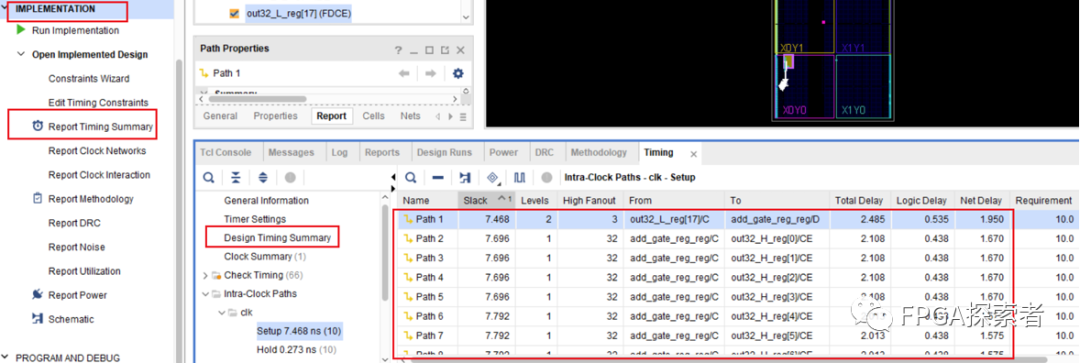

前面讲解了时序约束的理论知识FPGA时序约束理论篇,本章讲解时序约束实际使用。

2023-08-14 18:22:14 842

842

FPGA系统设计实质上是一个同步时序系统的设计,理解时序概念,掌握代码优化与综合技术,正确完整地进行时序约束和分析是实现高性能系统的重要保证。很多同学在设计中都会碰到时序方面的问题,如何解决时序难题

2018-06-07 15:52:07

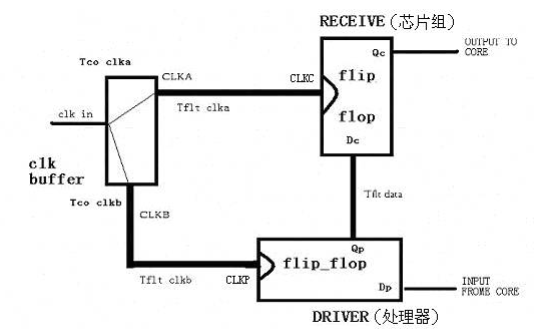

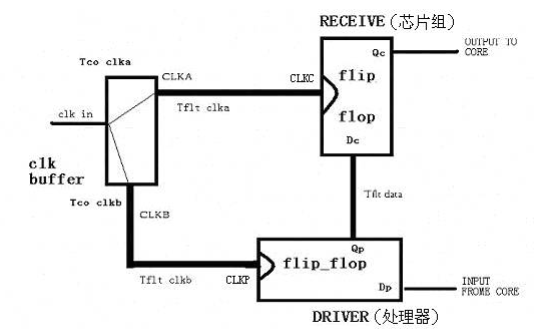

FPGA时序分析系统时序基础理论对于系统设计工程师来说,时序问题在设计中是至关重要的,尤其是随着时钟频率的提高,留给数据传输的有效读写窗口越来越小,要想在很短的时间限制里,让数据信号从驱动端完整

2012-08-11 17:55:55

FPGA时序分析与约束(1)本文中时序分析使用的平台:quartusⅡ13.0芯片厂家:Inter1、什么是时序分析?在FPGA中,数据和时钟传输路径是由相应的EDA软件通过针对特定器件的布局布线

2021-07-26 06:56:44

你好: 现在我使用xilinx FPGA进行设计。遇到问题。我不知道FPGA设计是否符合时序要求。我在设计中添加了“时钟”时序约束。我不知道如何添加其他约束。一句话,我不知道哪条路径应该被禁止。我

2019-03-18 13:37:27

经过两天的恶补,特别是学习了《第五章_FPGA时 序收敛》及其相关的视频后,我基本上明白了时序分析的概念和用法。之后的几天,我会根据一些官方的文件对时序分析进行更系统、深入的学习。先总结一下之前

2011-09-23 10:26:01

和时钟偏差组成的。

二、时序路径

时序路径是指从FPGA输入到输出的所有逻辑路径组成的路径。当存在时序路径时,需要考虑时序约束以确保正确的逻辑功能和时序性能。

时序路径中的关键元素包括:

(1) 路径

2023-11-15 17:41:10

FPGA时序约束,总体来分可以分为3类,输入时序约束,输出时序约束,和寄存器到寄存器路径的约束。其中输入时序约束主要指的是从FPGA引脚输入的时钟和输入的数据直接的约束。共分为两大类:1、源同步系统

2015-09-05 21:13:07

FalsePath、MulticyclePath、MaxDelay、MinDelay。但这还不是最完整的时序约束。如果仅有这些约束的话,说明设计者的思路还局限在FPGA芯片内部。 2. 核心频率约束

2016-06-02 15:54:04

不是最完整的时序约束。如果仅有这些约束的话,说明设计者的思路还局限在FPGA芯片内部。 2. 核心频率约束+时序例外约束+I/O约束 I/O约束包括引脚分配位置、空闲引脚驱动方式、外部走线延时

2017-12-27 09:15:17

FPGA时序相关的资料。都看完看懂时序就没问题了。分了三个附件:第一个是通过一些例子教你如何搞定时序分析。第二个附件是网上各种大神们对时序的理解,主要是他们的博客链接以及网站链接。第三个是其他的一些零散的关于时序的资料。

2012-11-12 17:45:28

FPGA中的I_O时序优化设计在数字系统的同步接口设计中, 可编程逻辑器件的输入输出往往需要和周围新片对接,此时IPO接口的时序问题显得尤为重要。介绍了几种FPGA中的IPO时序优化设计的方案, 切实有效的解决了IPO接口中的时序同步问题。

2012-08-12 11:57:59

FPGA为什么是实现绿色搜索技术的关键?

2021-05-08 07:47:03

FPGA毕竟不是ASIC,对时序收敛的要求更加严格,本文主要介绍本人在工程中学习到的各种时序约束技巧。 首先强烈推荐阅读官方文档UG903和UG949,这是最重要的参考资料,没有之一。它提倡

2020-12-23 17:42:10

基本的时序分析理论1本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 何谓静态时序分析(STA,Static

2015-07-09 21:54:41

FPGA时钟时序资料

2014-06-03 20:13:27

FPGA的时序优化高级研修班通知通过设立四大专题,帮助工程师更加深入理解FPGA时序,并掌握时序约束和优化的方法。1.FPGA静态时序分析2.FPGA异步电路处理方法3.FPGA时序约束方法4.FPGA时序优化方法

2013-03-27 15:20:27

FPGA/CPLD的综合、实现过程中指导逻辑的映射和布局布线。下面主要总结一下Xilinx FPGA时序约束设计和分析。

2023-09-21 07:45:57

延迟。 首先,我们使用TimingDesigner软件通过存储器数据表为QDR SRAM创造一个图表 大多数的FPGA利用约束驱动进行布局和布线。时序约束为关键信号提供时序信息

2017-09-01 10:28:10

FPGA设计技巧_关键路径FPGA软件无线电开发(全阶视频教程+开发板+实例)详情链接:http://url.elecfans.com/u/5e4a12f2ba

2014-04-22 13:11:41

随着FPGA器件体积和复杂性的不断增加,设计工程师越来越需要有效的验证方。时序仿真可以是一种能发现最多问题的验证方法,但对许多设计来说,它常常是最困难和费时的方法之一。过去,采用标准台式计算机的时序

2019-07-16 08:10:25

FPGA设计验证关键要点不同于ASIC设计,FPGA设计中的标准元件或客制化实作,一般欠缺大量的资源及准备措施可用于设计验证。由于可以重新程式化元件,更多时候验证只是事后的想法。本文将探讨在FPGA

2010-05-21 20:32:24

FPGA高级时序综合教程The UCF FileUCF =用户约束文件( User Constraints File )可以用文本编辑器和XilinxConstraints Editor (GUI

2012-08-11 11:28:50

fpga高手经验谈doc文档在数字电路的设计中,时序设计是一个系统性能的主要标志,在高层次设计方法中,对时序控制的抽象度也相应提高,因此在设计中较难把握,但在理解RTL电路时序模型的基础上,采用合理

2012-08-11 11:30:39

fpga关键路径 一份很好的资料

2013-07-12 17:33:36

在学习fpga的过程中的疑问:1、在功能仿真和板级验真后没问题,还需要进行时序分析吗2、怎么知道自己写的代码有时序问题?

2017-01-08 17:50:35

fpga时序逻辑电路的分析和设计 时序逻辑电路的结构及特点时序逻辑电路——任何一个时刻的输出状态不仅取决于当时的输入信号,还与电路的原状态有关。[hide][/hide]

2012-06-20 11:18:44

各位大侠,能否分享一下找到影响时序的关键路径的一些经验

2014-02-27 11:17:52

时序约束可以很复杂,这里我们先介绍基本的时序路径约束,复杂的时序约束我们将在后面进行介绍。在本节的主要内容如下所示:·时序路径和关键路径的介绍 ·建立时间、保持时间简述 ·时钟的约束(寄存器-寄存器之间的路径约束) ·输入延时的约束 ·输出延...

2021-07-26 08:11:30

和关键路径调整为了获得更好的时序,我们建议使用特定的代码风格来描述有限状态机、RAM、数学/DSP功能、时钟树和移位寄存器。结果会提高时序QoR,因为综合工具能够推断一个实现使用了FPGA原语的构件

2019-08-11 08:30:00

什么是时序分析?时序约束的作用是什么?FPGA组成的三要素分别是哪些?

2021-09-18 06:05:51

什么是时序路径和关键路径?常见的时序路径约束有哪些?

2021-09-28 08:13:15

当你的FPGA设计不能满足时序要求时,原因也许并不明显。解决方案不仅仅依赖于使用FPGA的实现工具来优化设计从而满足时序要求,也需要设计者具有明确目标和诊断/隔离时序问题的能力。设计者现在有一些

2021-05-18 15:55:00

了如何通过FPGA实现RS 232接口的时序逻辑设计。关键词:FPGA;时序电路;RS 232;串行通信

2019-06-19 07:42:37

。掌握分析和确定关键路径时序的方法,并通过分析找出关键路径的时序问题,再对关键路径进行优化,通过RTL层面的不断优化,不断修炼自己的设计能力,让设计出来的电路更为靠谱有效!本资料属大西瓜FPGA开发团队,在此开源,与大家一起学习FPGA!

2017-02-26 09:42:48

大家好,我想知道如何实现硬件(FPGA)中的时序报告给出的时序。我的意思是,如何测量FPGA和FPGA中输入信号的建立或保持时间与静态时间报告给出的值进行比较。FPGA怪胎以上来自于谷歌翻译以下

2019-01-15 11:07:15

延迟和确定正确的相位偏移。4. 使用FPGA设计要素大多数的FPGA利用约束驱动进行布局和布线。时序约束为关键信号提供时序信息。TimingDesigner提供独特的时序参考图如测量和计算变量结果,从

2009-04-14 17:03:52

1. FPGA时序的基本概念FPGA器件的需求取决于系统和上下游(upstream and downstrem)设备。我们的设计需要和其他的devices进行数据的交互,其他的devices可能是

2019-07-09 09:14:48

FPGA重要设计思想及工程应用之时序及同

在FPGA设计中最好的时钟方案 是: 由专用的全局时钟输入引脚 动单个 主时钟去控制设计项目中的每一个触发 器

2010-02-09 10:29:36 51

51 如何有效的管理FPGA设计中的时序问题

当FPGA设计面临到高级接口的设计问题时,EMA的TimingDesigner可以简化这些设计问题,并提供对几乎所有接口的预先精确控制。从简单

2009-04-15 14:19:31 659

659

介绍了采用STA (静态时序分析)对FPGA (现场可编程门阵列)设计进行时序验证的基本原理,并介绍了几种与STA相关联的时序约束。针对时序不满足的情况,提出了几种常用的促进 时序收敛的方

2011-05-27 08:58:50 70

70 FPGA时序约束方法很好地资料,两大主流的时序约束都讲了!

2015-12-14 14:21:25 19

19 FPGA重要设计思想及工程应用之时序及同步设计

2016-05-10 11:24:33 16

16 赛灵思FPGA设计时序约束指南,下来看看

2016-05-11 11:30:19 48

48 基于时序路径的FPGA时序分析技术研究_周珊

2017-01-03 17:41:58 2

2 如何有效地管理FPGA设计中的时序问题

2017-01-14 12:49:02 14

14 当你的FPGA设计不能满足时序要求时,原因也许并不明显。解决方案不仅仅依赖于使用FPGA的实现工具来优化设计从而满足时序要求,也需要设计者具有明确目标和诊断/隔离时序问题的能力。设计者现在有一些

2017-02-09 01:59:11 264

264 fpga时序收敛

2017-03-01 13:13:34 23

23 作时序和布局约束是实现设计要求的关键因素。本文是介绍其使用方法的入门读物。 完成 RTL 设计只是 FPGA 设计量产准备工作中的一部分。接下来的挑战是确保设计满足芯片内的时序和性能要求。为此

2017-11-17 05:23:01 2417

2417

一个好的FPGA设计一定是包含两个层面:良好的代码风格和合理的约束。时序约束作为FPGA设计中不可或缺的一部分,已发挥着越来越重要的作用。毋庸置疑,时序约束的最终目的是实现时序收敛。时序收敛作为

2017-11-17 07:54:36 2326

2326

现有的工具和技术可帮助您有效地实现时序性能目标。当您的FPGA 设计无法满足时序性能目标时,其原因可能并不明显。解决方案不仅取决于FPGA 实现工具为满足时序要求而优化设计的能力,还取决于设计人员指定前方目标,诊断并隔离下游时序问题的能力。

2017-11-18 04:32:34 2951

2951 作为赛灵思用户论坛的定期访客(见 ),我注意到新用户往往对时序收敛以及如何使用时序约束来达到时序收敛感到困惑。为帮助 FPGA设计新手实现时序收敛,让我们来深入了解时序约束以及如何利用时序约束实现

2017-11-24 19:37:55 4903

4903

FPGA时序布局算法TMDCP。将退火过程分发至多线程执行,利用TM机制保证共享内存访问的合法性,并将改进的时序优化算法嵌入到事务中并发执行。测试结果表明,与通用布局布线工具相比,8线程下的TMDCP算法在总线长仅有轻微增加的情况下,关键

2018-02-26 10:09:04 0

0 FPGA时序收敛让你的产品达到最佳性能!

2018-04-10 11:38:48 18

18 FPGA设计一个很重要的设计是时序设计,而时序设计的实质就是满足每一个触发器的建立(Setup)/保持(Hold)时间的要求。

2018-06-05 01:43:00 4150

4150

FPGA设计中,层次结构设计和复位策略影响着FPGA的时序。在高速设计时,合理的层次结构设计与正确的复位策略可以优化时序,提高运行频率。

2019-02-15 15:15:53 849

849 关键词:FPGA , 国产 , 国产FPGA , 试用 作者在:特权同学 关于时序工具的一些FAE解答: 问:你们的工具是否只提供所有输入输出管脚完全一致的时序约束?如tsu,th,tco,tpd

2019-02-25 18:24:01 266

266

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-05 07:08:00 2539

2539

时序分析结果,并根据设计者的修复使设计完全满足时序约束的要求。本章包括以下几个部分: 1.1 静态时序分析简介 1.2 FPGA 设计流程 1.3 TimeQuest 的使用 1.4 常用时序约束 1.5 时序分析的基本概念

2020-11-11 08:00:00 58

58 本文档的主要内容详细介绍的是华为FPGA硬件的静态时序分析与逻辑设计包括了:静态时序分析一概念与流程,静态时序分析一时序路径,静态时序分析一分析工具

2020-12-21 17:10:54 18

18 时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2021-01-08 16:57:55 28

28 在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束利序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是重点。只有约東正确才能在高速情况下保证FPGA和外部器件通信正确

2021-01-13 17:13:00 11

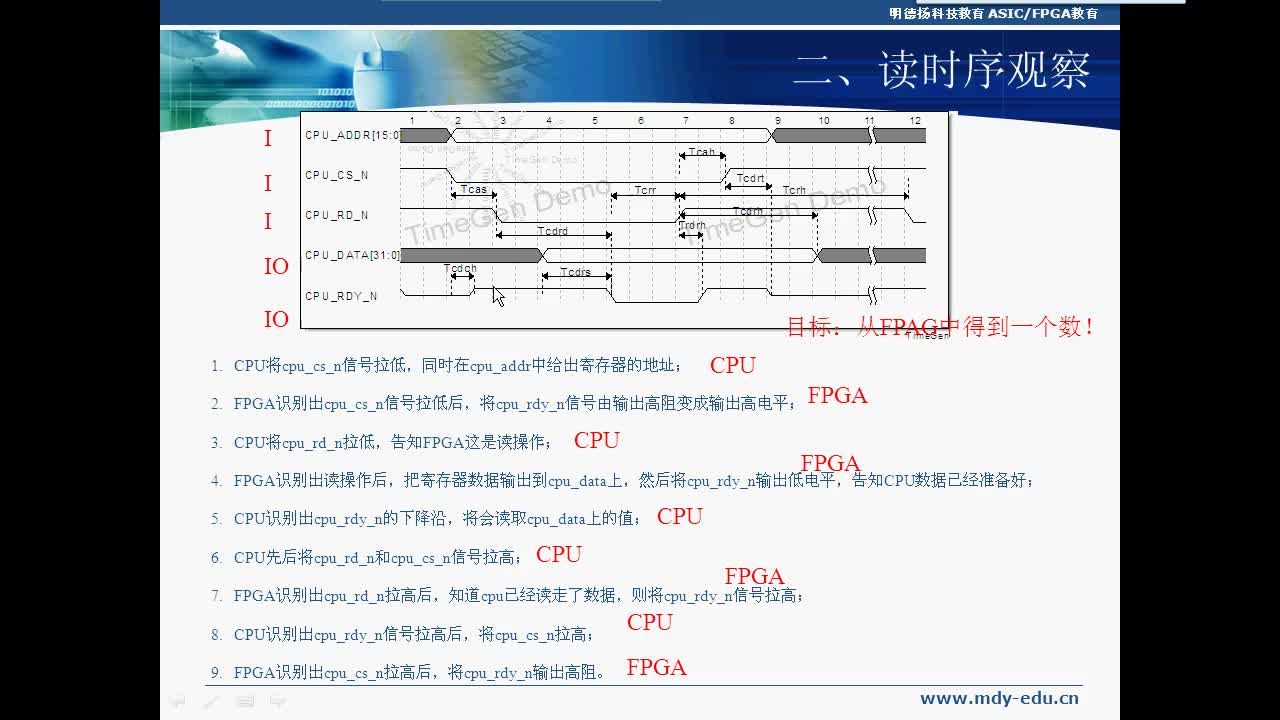

11 本文章探讨一下FPGA的时序约束步骤,本文章内容,来源于配置的明德扬时序约束专题课视频。

2022-03-16 09:17:19 3255

3255

上一篇《FPGA时序约束分享01_约束四大步骤》一文中,介绍了时序约束的四大步骤。

2022-03-18 10:29:28 1323

1323

时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2022-03-18 11:07:13 2096

2096 本文章探讨一下FPGA的时序input delay约束,本文章内容,来源于配置的明德扬时序约束专题课视频。

2022-05-11 10:07:56 3462

3462

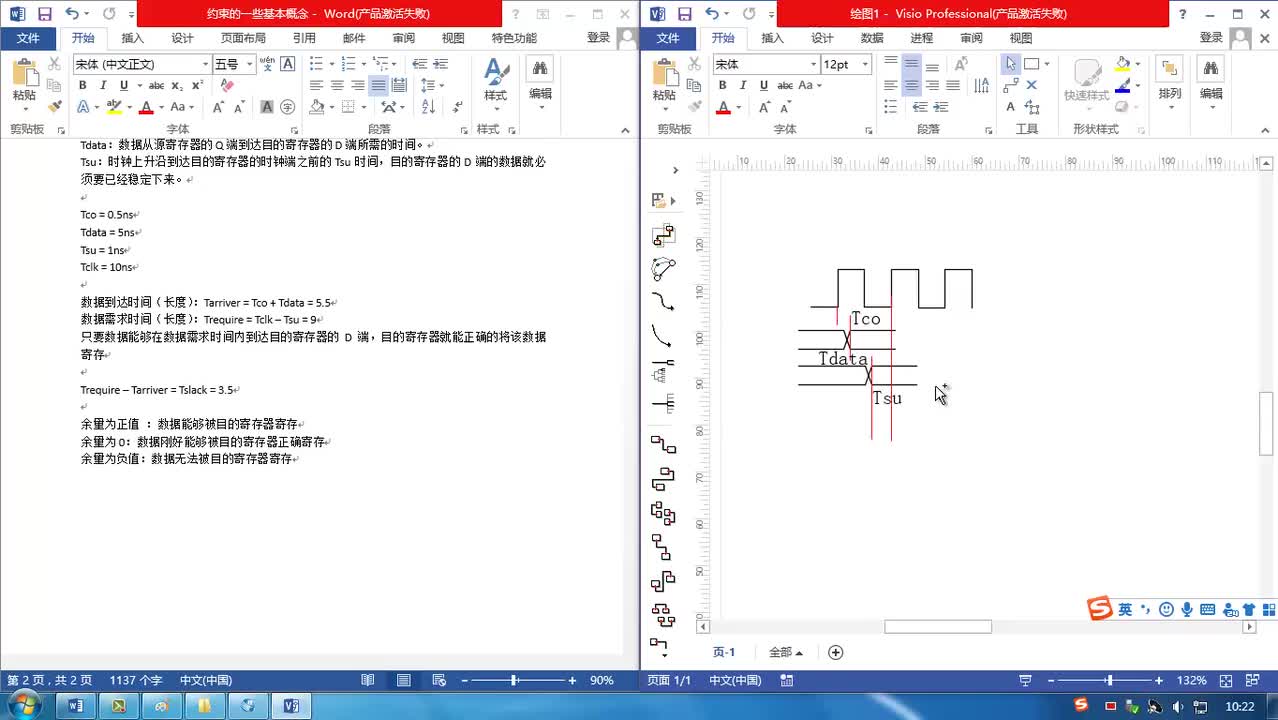

明德扬有完整的时序约束课程与理论,接下来我们会一章一章以图文结合的形式与大家分享时序约束的知识。要掌握FPGA时序约束,了解D触发器以及FPGA运行原理是必备的前提。今天第一章,我们就从D触发器开始讲起。

2022-07-11 11:33:10 2922

2922

本文章探讨一下FPGA的时序input delay约束,本文章内容,来源于明德扬时序约束专题课视频。

2022-07-25 15:37:07 2379

2379

FPGA/CPLD的综合、实现过程中指导逻辑的映射和布局布线。下面主要总结一下Xilinx FPGA时序约束设计和分析。

2023-04-27 10:08:22 768

768 随着FPGA对时序和性能的要求越来越高,高频率、大位宽的设计越来越多。在调试这些FPGA样机时,需要从写代码时就要小心谨慎,否则写出来的代码可能无法满足时序要求。

2023-05-06 09:33:27 774

774

STA(Static Timing Analysis,即静态时序分析)在实际FPGA设计过程中的重要性是不言而喻的

2023-06-26 09:01:53 362

362

FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间。

2023-06-26 14:42:10 344

344

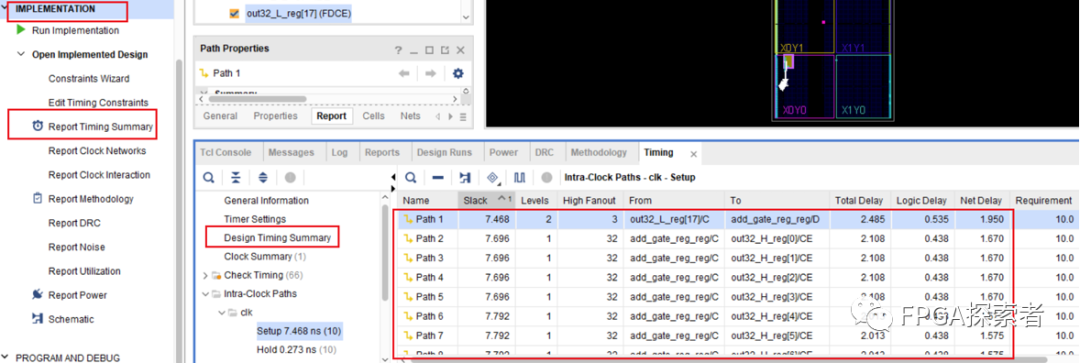

FPGA开发过程中,vivado和quartus等开发软件都会提供时序报告,以方便开发者判断自己的工程时序是否满足时序要求。

2023-06-26 15:29:05 531

531

FPGA时序不收敛,会出现很多随机性问题,上板测试大概率各种跑飞,而且不好调试定位原因,所以在上板测试前,先优化时序,再上板。

2023-06-26 15:41:31 1112

1112

FPGA高级时序综合教程

2023-08-07 16:07:55 3

3

正在加载...

电子发烧友App

电子发烧友App

评论