介绍了一种基于CPLD技术的MOSFET器件保护电路的设计与实现。该电路设计方案具有抗干扰能力强、响应速度快和通用性好的优点。通过试验验证了该方案的正确性和可行性。##在功率MOSFET保护电路输入

2014-04-25 11:15:47 1939

1939 本文将介绍一款基于ARM控制的逆变器电源电路设计方案及其应用。##系统软件设计

2014-05-12 10:59:26 3362

3362 485接口EMC电路设计方案分析: 一.原理图 1. RS485接口6KV防雷电路设计方案 图1 RS485接口防雷电路 接口电路设计概述: RS485用于设备与计算机或其它设备之间通讯,在产品

2018-02-10 02:51:03 26470

26470

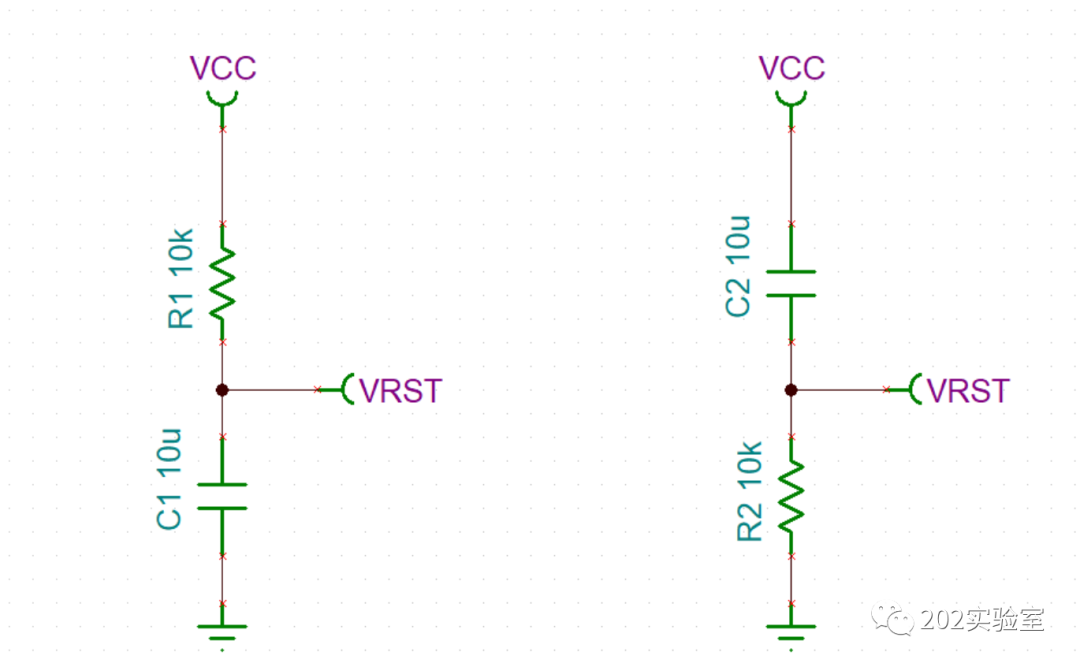

最近看advanced fpga 以及fpga设计实战演练中有讲到复位电路的设计,才知道复位电路有这么多的门道,而不是简单的外界信号输入系统复位。

2020-09-01 15:37:07 1461

1461

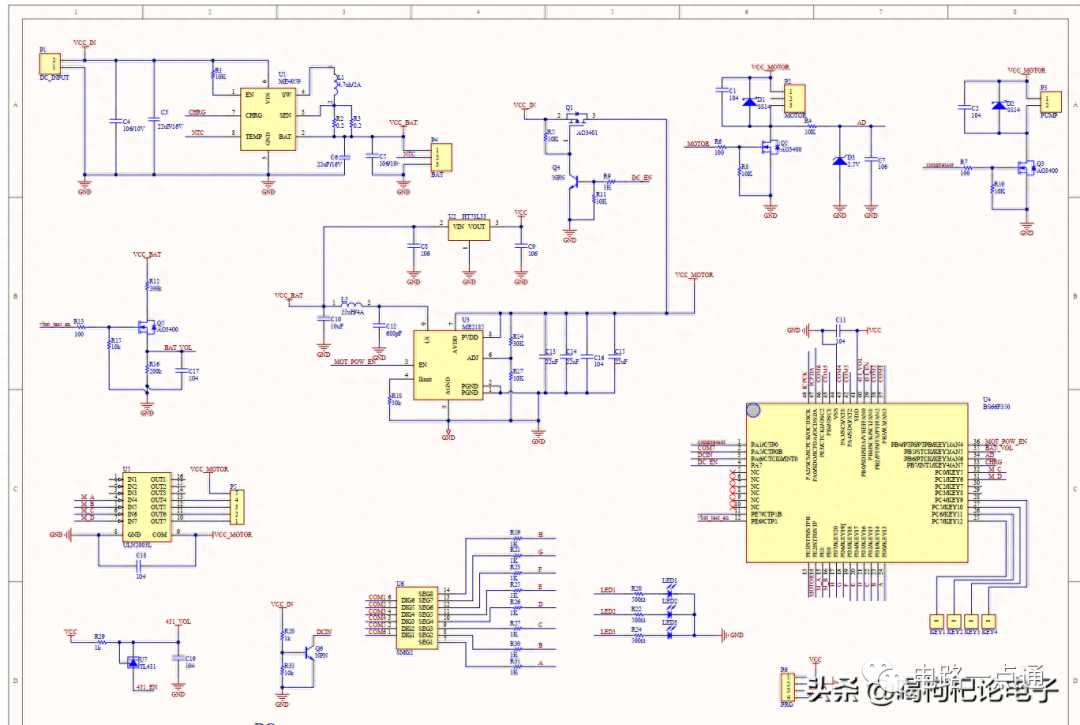

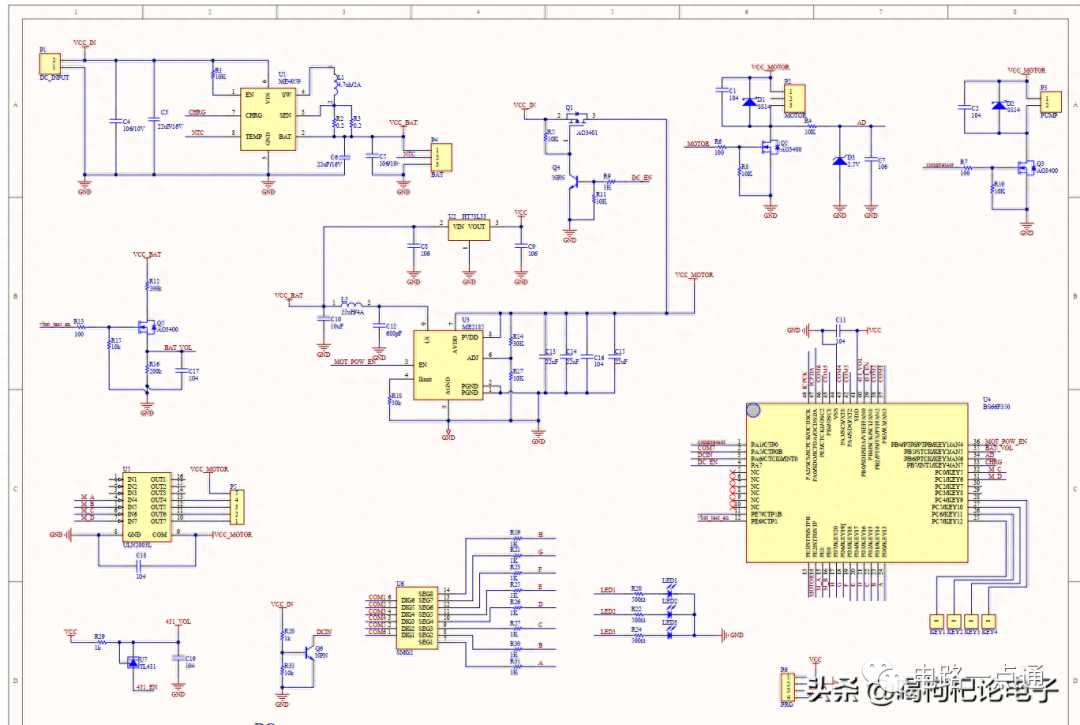

今天分享一个电动吸奶器的电路设计方案,如果不知道电动吸奶器是啥玩意的朋友,请自行百度脑补,电路原理图如下。

2023-08-24 09:09:19 1944

1944

本文主要介绍了电流检测电路设计方案汇总(六款模拟电路设计原理图详解),采用差分运放进行高端电流检测的电路更便于使用,因为近期推出了许多种集成电路解决方案。专用高端检流电路内部包含了完成高端电流检测

2018-02-06 11:31:39 322979

322979

的面阵CCD驱动时序发生器设计,基于CPLD的面阵CCD驱动时序发生器设计及其硬件实现,基于CPLD的线阵CCD驱动电路的设计,基于CPLD的线阵CCD驱动电路设计与实现,基于CPLD的线阵CCD驱动

2019-06-03 16:45:25

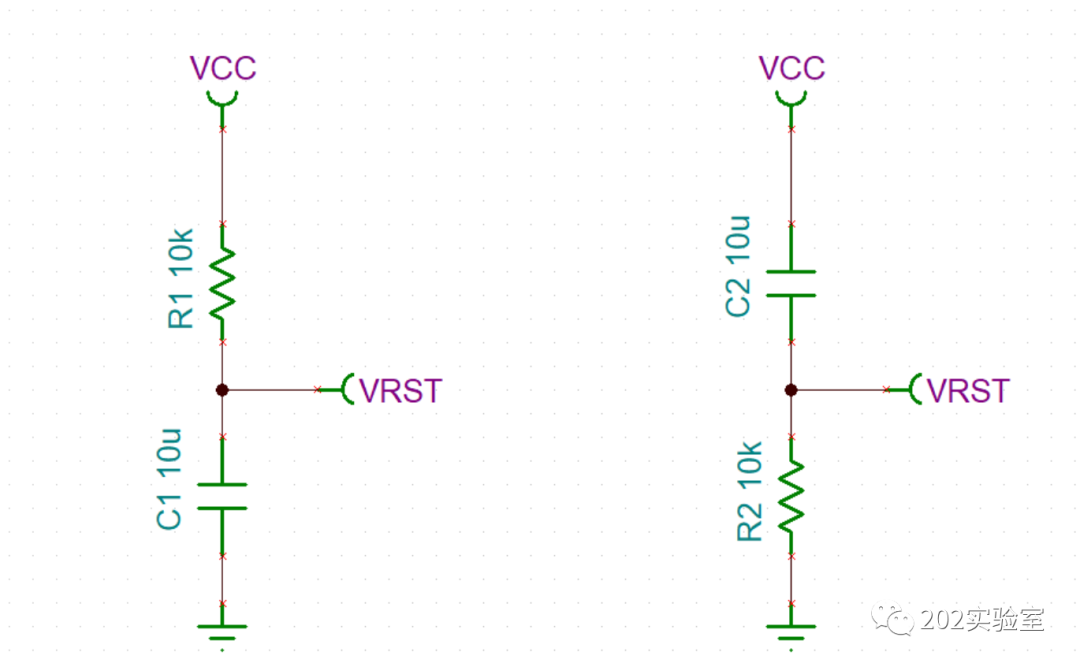

51单片机复位电路的设计方案

2012-11-29 19:37:59

用户根据需要生成特定的电路结构,完成一定的功能。由于 CPLD内部采用固定长度的金属线进行各逻辑块的互连,所以设计的逻辑电路具有时间可预测性,避免了分段式互连结构时序不完全预测的缺点。到90年代

2009-09-29 09:38:32

FPGA CPLFPGA CPLD 数字电路设计经验分享FPGA/CPLD数字电路设计经验分享摘要:在数字电路的设计中,时序设计是一个系统性能的主要标志,在高层次设计方法中,对时序控制的抽象度也相应

2012-08-11 10:17:18

数字系统是行之有效的,通过许多设计实例证明采用这种方式可以使电路的后仿真通过率大大提高, 并且系统的工作频率可以达到一个较高水平。本文档为你讲述FPGA/CPLD 数字电路设计经验和一些设计方法:[hide] [/hide]

2012-02-02 15:40:10

words:FPGA/CPLD;Synchronous design;Clock;Metastable state利用FPGA/CPLD实现数字系统电路设计时,如何设计出可读性强、重复利用率高、工作稳定可靠

2009-04-21 16:42:01

本帖最后由 xianer317 于 2014-6-21 19:34 编辑

FPGA/CPLD数字电路设计经验分享

2014-06-21 19:33:20

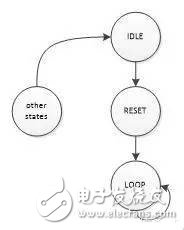

复位电路本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCttFPGA器件在上电后都需要有一个确定的初始状态,以

2019-04-12 06:35:31

信号送到器件的引脚上或者传进来,并且把CPLD内部的逻辑群连接起来。CPLD之所以称作粗粒,是因为,与路由数量相比,逻辑群要大得到。CPLD的逻辑群比FPGA的基本单元大得多,因此FPGA是细粒

2012-10-26 08:10:36

/O单元互连结构,可由用户根据需要生成特定的电路结构,完成一定的功能.由于 CPLD内部采用固定长度的金属线进行各逻辑块的互连,所以设计的逻辑电路具有时间可预测性,避免了分段式互连结构时序不完全预测

2020-08-28 15:41:47

片风险,使用方便。 3.通过开发工具在计算机上完成设计,电路设计周期短。 4.不需要设计人员了解很深的IC知识,EDA软件易学易用。 5.通过FPGA和CPLD开发的系统成熟后,可以进行ASIC设计,形成批量生产。

2020-07-16 10:46:21

FPGA时钟和复位电路设计本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt FPGA的时钟输入都有专用引脚

2015-04-24 08:17:00

各位FPGA设计大赛参赛者注意了:小编这里帮大家解释一下设计方案提交规则和活动时间安排

自4月23日比赛开始,参赛者报名之后即可提交设计方案。设计方案提交的截止日期是活动结束,暨设计方案评选的最后

2012-05-04 10:27:46

PFGA CPLD 电路设计1,alter EMP570

2011-11-10 07:54:48

。在数字电路设计中,设计人员一般把全局复位作为一个外部引脚来实现,在加电的时候初始化设计。全局复位引脚与任何其它输入引脚类似,对 FPGA 来说往往是异步的。设计人员可以使用这个信号在 FPGA 内部对自己的设计进行异步或者同步复位。常见的复位方式有三种1、硬件开关:复位信号接一个拨码开关或按键,.

2021-11-11 06:06:08

、印制板设计等。在设计完成后进行试验,以便对其不合理的部分进行修正,并最终确定硬件设计方案和完成印制电路板。中心控制器电路主要包括以下几个部分:(1) 电路核心部分:ARM微处理器、复位电路、晶振电路

2015-01-17 14:43:31

SSS1530电路设计,DEMO原理图,Type-C耳机设计方案

2017-10-26 17:42:29

`例说FPGA连载17:时钟与复位电路设计特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc FPGA的时钟输入都有专用引脚,通过这些专用

2016-08-08 17:31:40

LM358的封装形式有哪几种?基于LM358的人体感应灯电路设计方案

2021-04-14 06:34:52

分享一款不错的基于可编程逻辑器件PLD的数字电路设计方案

2021-04-30 06:34:54

本文以星载测控系统为背景,提出了一种基于 Actel Flash FPGA的高可靠设计方案。采用不易发生单粒子翻转的 flash FPGA芯片,结合 FPGA内部的改进型三模冗余、分区设计和降级重构,实现了高实时、高可靠的系统。

2021-05-10 06:58:47

高频感应加热电源驱动电路设计方案就目前国内的感应加热电源研发现状而言,高频感应加热电源是主流的研发设计方向,也是很多工程师的工作重点。在今天的文章中,我们将会为大家分享一种基于IR2llO芯片的高频

2021-07-26 07:07:52

本帖最后由 gk320830 于 2015-3-4 17:54 编辑

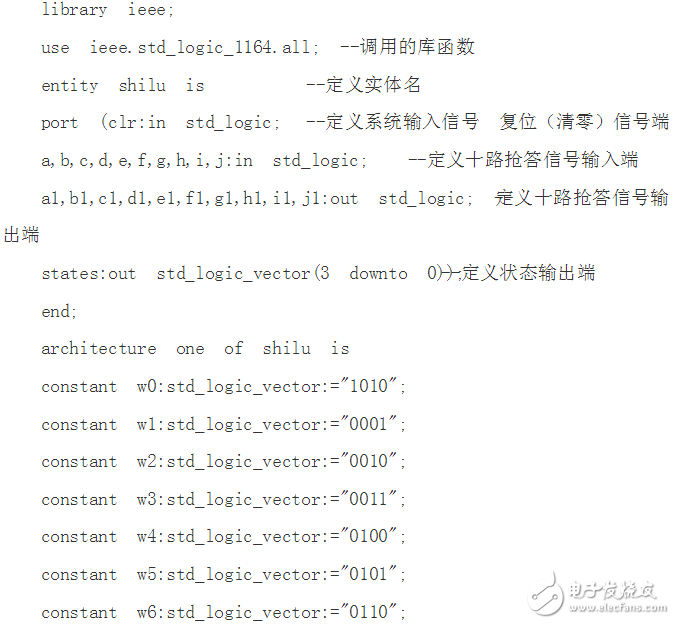

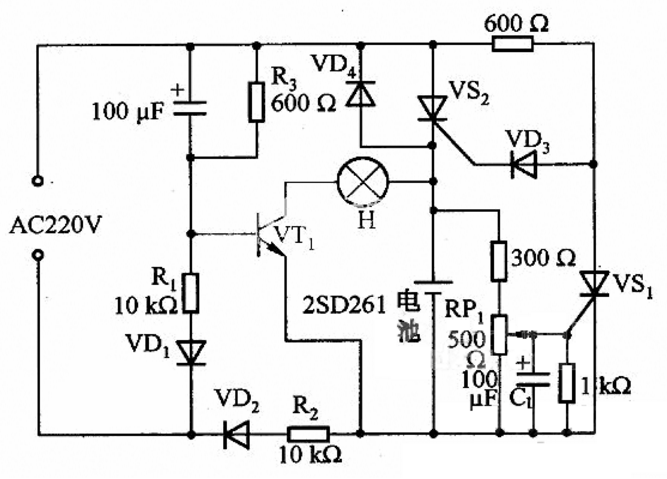

可控硅过零检测调速控制电路设计方案

2012-08-20 13:32:42

基于KeyStone架构的DSP电源设计方案电源硬件电路设计与计算

2021-02-04 06:48:30

晶振具有的等效电气特性晶振电路设计方案,电路中各元器件的作用是什么?消除晶振不稳定和起振问题有什么具体的建议和措施吗?

2021-04-13 06:19:09

求一个48V2A转5V2A的降压电路设计方案,要求效率尽量高,输出稳定点,尽量详细。或者推荐几款适合芯片,求指导大神们!!!

2019-07-24 13:01:14

求一种DSP+CPLD新型的智能仪器的设计方案

2021-05-08 07:54:25

求一种以CPLD为核心处理电路的数字电压表的设计方案

2021-04-28 07:14:04

本文针对点电网及现场出现的噪声干扰问题,提出一种去抖动电路设计方案.阐述了移相电路的基本设计思路。

2021-04-08 06:19:40

量程自切换频率的硬件电路设计量程自切换频率的软件部分设计如何对量程自切换频率系统进行调试?

2021-04-29 06:53:33

电流/电压转换电路设计方案在工业控制中各类传感器常输出标准电流信号4~20mA,为此,常要先将其转换成±10V;的电压信号,以便送给各类设备进行处理。这种转换电路以4mA 为满量程的0%对应-10V

2009-12-17 09:55:16

本文介绍了一种基于计算机总线的CPLD加密电路的设计方案。

2021-04-29 06:16:32

复位电路设计选型指南

介绍安森美(ON)公司及EXAR公司所生产的各种类型复位器件,方便工程师设计选型。

2010-04-02 12:12:43 0

0 基于FPGA的两相步进电机细分驱动电路设计摘要:在采用步进电机驱动的机构中,为了提高定位精度,提出了一种基于FPGA 的两相步进电机细分驱动电路的设计方案。

2010-05-11 16:09:41 50

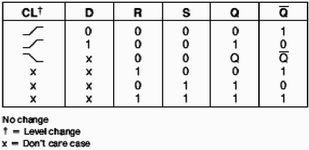

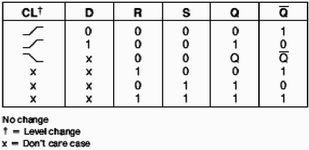

50 自动开/关机电路设计方案

摘要:本文介绍了一种结构简单、使用方便可靠的开/关机电路。电路使用一个D触发器,配合软件上的处理实现单键

2009-12-24 15:07:15 1684

1684

基于FPGA的光电抗干扰电路设计方案

光电靶的基本原理是:当光幕内的光通量发生足够大的变化时,光电传感器会响应这种变化而产生电信号。这就

2010-02-09 10:31:20 627

627

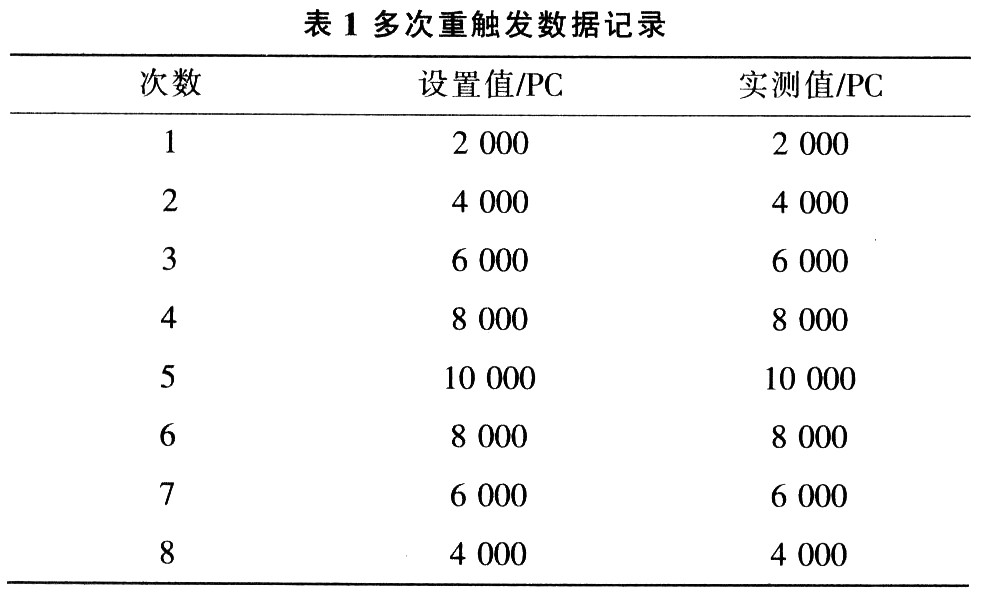

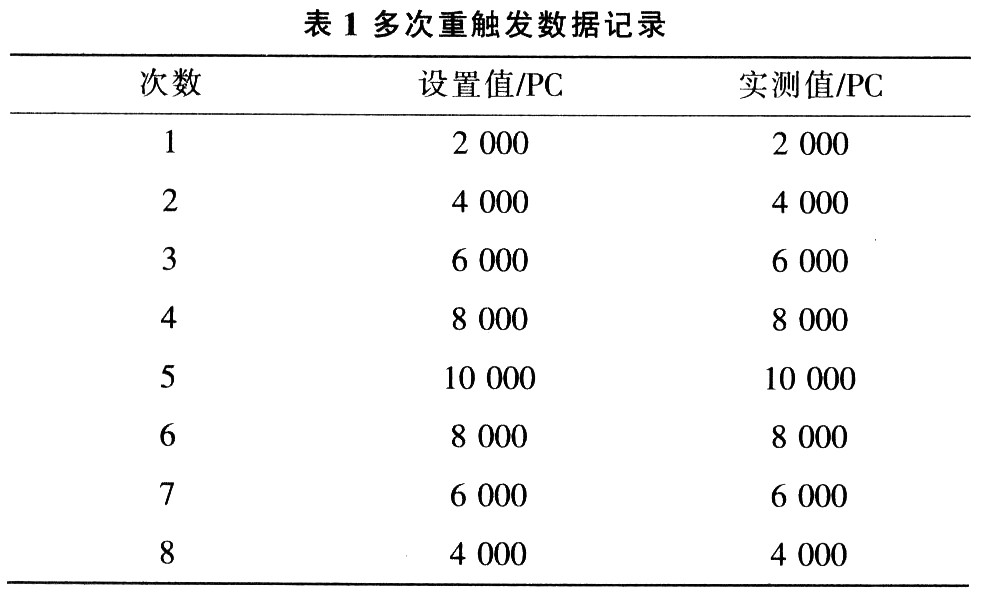

采用CPLD的多次重触发存储测试系统解决方案

概述:提出一种基于CPLD的多次重触发存储测试系统设计方案,详细介绍系统硬件设计以及CPLD内部控制

2010-03-17 11:37:51 531

531

在工业控制中如何提高一对多的串口通讯可靠性和系统的集成性成为研究热点。本文利用嵌入式技术,提出基于CPLD/FPGA的多串口扩展设计方案。实现并行口到多个全双工异步通讯口之间

2011-04-27 11:17:15 111

111 精密光电检测电路设计方案

2016-12-15 18:25:41 63

63 基于FPGA技术的RS232接口时序电路设计方案

2017-01-26 11:36:55 29

29 数字电路设计方案中DSP与FPGA的比较与选择

2017-01-18 20:39:13 15

15 当你需要将FPGA/CPLD内部的信号通过管脚输出给外部相关器件的时候,如果不影响功能最好是将这些信号通过用时钟锁存后输出。因为通常情况下一个板子是工作于一种或两种时钟模式下,与FPGA/CPLD相连接的芯片的工作时钟大多数情形下与FPGA的时钟同源,如果输出的信号经过时钟锁存可以起到如下的作用:

2017-02-11 13:18:12 1948

1948

在FPGA设计中,复位起到的是同步信号的作用,能够将所有的存储元件设置成已知状态。在数字电路设计中,设计人员一般把全局复位作为一个外部引脚来实现,在加电的时候初始化设计。全局复位引脚与任何其它输入

2017-11-22 17:03:45 5125

5125

本文为大家带来五种减法器电路设计方案介绍。

2018-01-17 11:29:44 86869

86869

本文为大家介绍五款乘法器电路设计方案,包括五款模拟电路设计原理及仿真程序分享,以供参考。

2018-01-17 18:03:30 53773

53773

本文为大家带来九款不同的除法运算电路设计方案,包括这九款模拟电路设计的原理及设计过程。

2018-01-17 18:24:49 49632

49632

本文为大家带来五种三人表决器电路设计方案,包括两款仿真电路及程序分析,三款逻辑电路设计的原理详解。

2018-01-17 18:49:21 298033

298033

本文为大家带来五款五人表决器电路设计方案。

2018-01-18 09:18:07 98683

98683

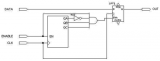

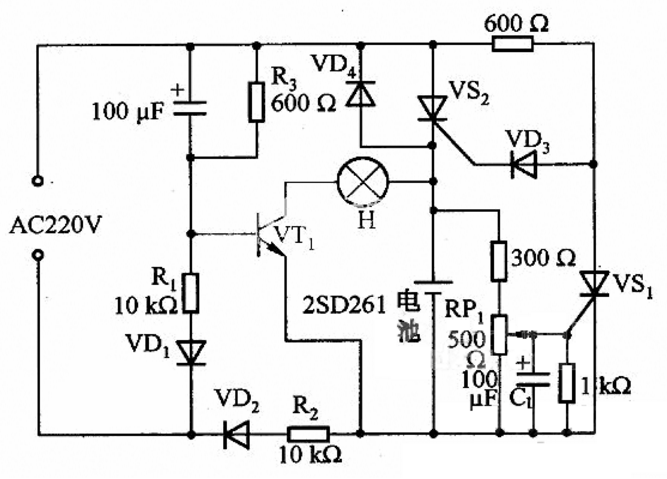

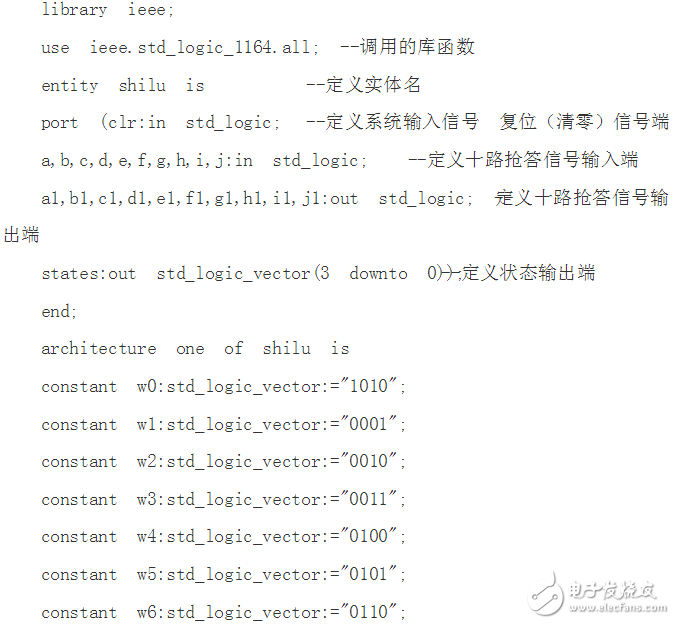

抢答器在各类智力竞赛之中经常出现,它的电路设计并不复杂,本文为大家带来三款十路抢答器电路设计方案。

2018-01-18 11:22:18 16650

16650

本文主要介绍了停电报警器电路设计方案汇总(五款模拟电路设计原理图详解),方案三分析了大部分电冰箱没有延时断电保护器,市电偶尔断电,瞬间又恢复供电,会对电冰箱造成不利影响,而白天又不易发现停电

2018-01-28 10:20:09 35116

35116

本文主要介绍了计数报警器电路设计方案汇总(多款模拟电路设计原理图详解),方案二主要由直流电源电路(整流、滤波、稳压电路)和计数报警电路(计数电路、译码电路、显示电路、声光报警电路)组成,:声光报警功能用蜂鸣器和LED灯实现,控制LED报警十秒,蜂鸣器报警10秒。

2018-01-29 10:30:07 23163

23163

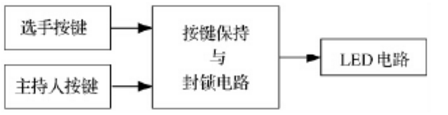

本文主要介绍了四人抢答器电路设计方案汇总(六款模拟电路设计原理图详解),四人抢答器的功能是每位参赛者有一个抢答按键,按动按键发出抢答信号;竞赛主持人有一个控制按键,用于将抢答信号复位和抢答开始;竞赛

2018-01-29 12:31:23 319015

319015

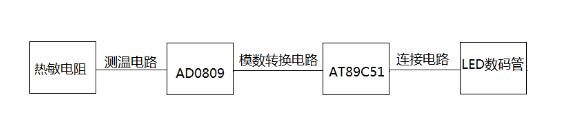

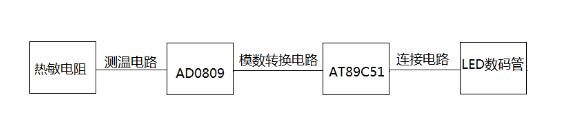

热电阻是基于电阻的热效应进行温度测量的,即电阻体的阻值随温度的变化而变化的特性。本文主要介绍了四款热敏电阻测温电路设计方案详情。

2018-02-02 14:54:56 49103

49103

WiFi产品的一般射频电路设计方案资料

2018-04-17 10:04:37 32

32 有源嵌位复位技术的设计方案资料下载

2018-04-25 16:35:21 10

10 基于FPGA的调焦电路设计方案资料下载

2018-05-07 15:53:08 9

9 PIC单片机 的 外接电压检测 复位电路 举例 1.设计思路 有许多型号单片机的内部均不具备掉电复位功能,即使对于内部包含该功能的PIC单片机,其复位门槛电压值是固定不可更改的,有时不能满足用户的需求,因此,外加电压检测复位电路也是较常见的设计方案。

2018-07-01 10:36:00 6935

6935

FPGA的可靠复位是保证系统能够正常工作的必要条件,本文对FPGA设计中常用的复位设计方法进行了分类、分析和比较,并针对各种复位方式的特点,提出了如何提高复位设计可靠性的方法。

2018-08-08 15:14:23 10154

10154 CPLD通常用于实现前面提到的简单组合逻辑功能,并负责“引导”FPGA以及控制整个电路板的复位和引导顺序。

2018-09-27 11:56:01 6191

6191 介绍了采用CPLD和Flash器件对FPGA 实现快速并行配置,并给出了具体的硬件电路设计和关键模块的内部编程思路。

2018-10-24 15:15:49 7

7 完成电子电路设计方案的过程大致分几个步骤?需要注意什么?

2019-04-12 17:45:52 14023

14023 485接口EMC电路设计方案!

2020-02-05 12:53:27 4078

4078 最近看 advanced fpga 以及 fpga 设计实战演练中有讲到复位电路的设计,才知道复位电路有这么多的门道,而不是简单的外界信号输入系统复位。 流程: 1. 异步复位: 优点:⑴大多数

2020-10-30 12:17:55 323

323 电子发烧友网站提供(温度传感器电路设计方案)资料免费下载。

2020-11-11 12:00:26 105

105 最近看 advanced fpga 以及 fpga 设计实战演练中有讲到复位电路的设计,才知道复位电路有这么多的门道,而不是简单的外界信号输入系统复位。

2020-12-22 12:54:00 13

13 卡拉OK人声增效电路设计方案

2021-03-25 11:06:33 7

7 带NFC管理的移动通信终端电路设计方案

2021-06-07 10:17:16 30

30 SSS1530电路设计方案免费下载。

2021-06-10 16:22:57 27

27 基于电流传输器的检测电路设计方案

2021-06-15 10:52:22 41

41 基于CPLD/FPGA的半整数分频器设计方案

2021-06-17 09:37:02 21

21 AC24V接口EMC标准电路设计方案

2021-07-12 11:16:36 33

33 AC380V EMC标准电路设计方案

2021-07-12 10:54:06 49

49 AV接口EMC标准电路设计方案

2021-07-12 10:52:08 28

28 CAN总线接口EMC标准电路设计方案

2021-07-12 10:45:28 199

199 智融SW3523车载快充电路设计方案

2021-08-14 11:01:10 85

85 小信号放大电路设计方案汇总

2021-09-14 15:01:12 127

127 FPGA CPLD数字电路设计经验分享.(电源技术发展怎么样)-FPGA CPLD数字电路设计经验分享

2021-09-18 10:58:03 51

51 。在数字电路设计中,设计人员一般把全局复位作为一个外部引脚来实现,在加电的时候初始化设计。全局复位引脚与任何其它输入引脚类似,对 FPGA 来说往往是异步的。设计人员可以使用这个信号在 FPGA 内部对自己的设计进行异步或者同步复位。常见的复位方式有三种1、硬件开关:复位信号接一个拨码开关或按键,.

2021-11-06 09:20:57 20

20 stm32复位电路设计

2022-06-26 09:26:01 7

7 有人说FPGA不需要上电复位电路,因为内部自带上电复位信号。也有人说FPGA最好加一个上电复位电路,保证程序能够正常地执行。不管是什么样的结果,这里先把一些常用的FPGA复位电路例举出来,以作公示。

2023-03-13 10:29:49 1585

1585 。 下面将讨论FPGA/CPLD的复位电路设计。 2、分类及不同复位设计的影响 根据电路设计,复位可分为异步复位和同步复位。 对于异步复位,电路对复位信号是电平敏感的,如果复位信号受到干扰,如出现短暂的脉冲跳变,电路就会部分或全部被

2023-04-06 16:45:02 782

782 我们在数字电路设计时,为了使系统在上电后处于 **已知的确定状态** ,常使用复位电路来实现这一目的。复位是数字逻辑电路所必须的,无论是最简单的数字时序逻辑门电路,还是复杂的 MCU、ARM、DSP

2023-05-25 14:48:07 2584

2584

有人说FPGA不需要上电复位电路,因为内部自带上电复位信号。也有人说FPGA最好加一个上电复位电路,保证程序能够正常地执行。不管是什么样的结果,这里先把一些常用的FPGA复位电路例举出来,以作公示。

2023-05-25 15:50:45 2110

2110

电子发烧友网站提供《基于CPLD/FPGA的多串口扩展设计方案.pdf》资料免费下载

2023-10-27 09:45:17 2

2 如果FPGA没有外部时钟源输入,可以通过调用STARTUP原语,来使用FPGA芯片内部的时钟和复位信号,Spartan-6系列内部时钟源是50MHz,Artix-7、Kintex-7等7系列FPGA是65MHz。

2023-10-27 11:26:56 973

973

电子发烧友网站提供《C波段二级放大电路设计方案.pdf》资料免费下载

2023-11-07 09:18:22 2

2 电子发烧友网站提供《一种推挽逆变车载开关电源电路设计方案.doc》资料免费下载

2023-11-14 14:23:15 0

0 电子发烧友网站提供《LED路灯驱动电路设计方案.doc》资料免费下载

2023-11-14 11:31:38 1

1 电子发烧友网站提供《基于PC机USB接口充电电路设计方案.doc》资料免费下载

2023-11-15 09:25:42 0

0 电子发烧友网站提供《FPGA/CPLD数字电路设计经验分享.pdf》资料免费下载

2023-11-21 11:03:12 3

3

电子发烧友App

电子发烧友App

评论