作者:Mculover666 1.实验目的 通过例程探索Vivado HLS设计流 用图形用户界面和TCL脚本两种方式创建Vivado HLS项目 用各种HLS指令综合接口 优化Vivado HLS

2020-12-21 16:27:21 3153

3153 在某些情况下,通过嗅探 AXI 接口来分析其中正在发生的传输事务是很有用的。在本文中,我将为大家演示如何创建基本 AXI4-Lite Sniffer IP 以对特定地址上正在发生的读写传输事务进行计数。

2022-07-08 09:35:34 775

775 设计技巧:在 Vivado Synthesis 中使用 SystemVerilog 接口连接逻辑

2019-07-02 12:03:07 10999

10999

请教一下,我在HLS里面要将以下程序生成IP核,C Synthesis已经做好了,但是在export RTL的时候一直在运行

int sum_single(int A int B

2023-09-28 06:03:53

2013.1 release notes regarding Zynq say: "Requires Early Access to Vivado IP integrator".What

2018-12-04 11:00:58

Vivado HLS视频库加速Zynq-7000 All Programmable SoC OpenCV应用加入赛灵思免费在线研讨会,了解如何在Zynq®-7000 All Programmable

2013-12-30 16:09:34

1.实验目的通过例程探索Vivado HLS设计流用图形用户界面和TCL脚本两种方式创建Vivado HLS项目用各种HLS指令综合接口优化Vivado HLS设计来满足各种约束用不用的指令来探索

2021-11-11 07:09:49

在模拟模型方面,Vivado提供的IP似乎有一些根本性的变化。在将工作设计从ISE 14.4转换为Vivado 2013.2之后,然后按照建议的方式升级大部分Xilinx IP,例如基本乘法器,除法

2019-02-26 10:42:23

在vivado生成ip核后缺少一大片文件,之前是可以用的,中途卸载过Modelsim,用vivado打开过ISE工程,因为工程中很多IP核不能用所以在重新生成过程中发现了这个问题,还请大神告知是怎么回事?

2023-04-24 23:42:21

你好,我如何启用自定义IP的中断。我使用vivado HLS生成了IP。中断线连接到ZYNQ的中断端口。以下是设备树{amba_pl:amba_pl {#address-cells

2020-05-01 16:46:48

本人在学习vivado系列软件开发套件的时候遇到以下问题.硬件平台:米尔科技 Z-turn 7020 Board.问题描述:我在Vivado hls 里面写了一个函数int add(int a

2016-01-28 18:40:28

本人在学习vivado系列软件开发套件的时候遇到以下问题.硬件平台:米尔科技 Z-turn 7020 Board.问题描述:我在Vivado hls 里面写了一个函数int add(int a

2016-01-28 18:39:13

请教一下,vivado怎么把带ip核的工程进行封装,保证代码不可见,可以通过端口调用。我尝试了以下方法,ippackage,如果要在另一个程序里调用,也要提供源代码;另一个方法是将网表文件edf文件与端口声明结合,这种方法只能实现不带ip核的封装

2017-07-14 09:18:30

本实验通过调用PLL IP core来学习PLL的使用、vivado的IP core使用方法。

2021-03-02 07:22:13

嗨,有什么例子vor Vivado 14.1如何在块设计中使用以太网ip核心?我想将帧传输到PL进行数据包检查。 (1GBit etho)谢谢HS

2020-03-16 09:54:01

早安Xilinx Communitry,我有一个关于VIVADO IP中心设计流程的问题。设计针对Xilinx fpga的数字逻辑不仅仅有一种方法。您可以使用HLS和HDL进行设计。您可以使用纯

2019-03-29 09:14:55

,我们一直在使用Vivado给我们提供的IP或者使用硬件描述语言制作 IP 。今天我们将讲解如何使用HLS-高级综合语言来创建属于我们自己的IP。我们将使用的工具称为Vitis HLS,此后称为 HLS

2022-09-09 16:45:27

我对Vivado内部的IP检查点有疑问。当我在Vivado中启用IP内核的检查点时,我可以在Design Runs窗口中看到此IP的“synth”和“impl”。对于IP的“合成”,我可以理解这是

2019-03-08 13:30:52

请问有哪位大神,可以帮忙破解一个vivado的IP核。不胜感激,联系QQ397679468

2017-11-24 09:30:30

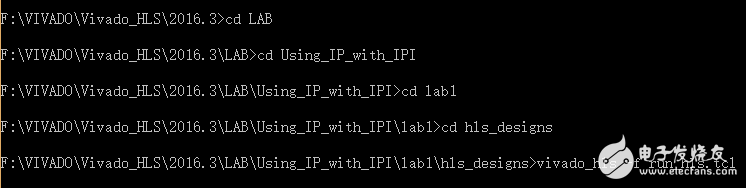

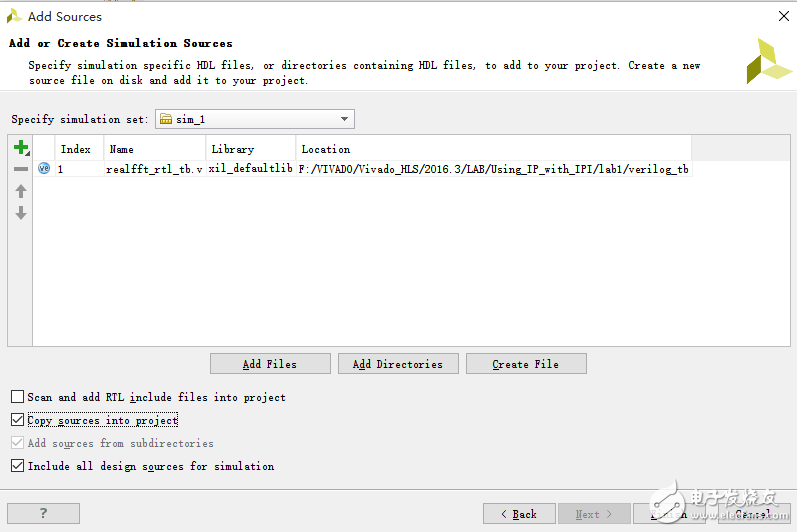

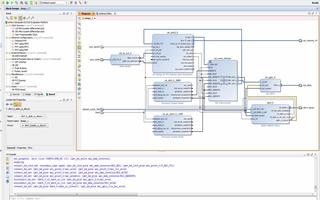

Debugger”,并点击OK。图6编译完成后即可全速或单步运行仿真代码。图7IP核封装综合完成后,点击生成IP核。图12图13图14运行完成后,将会在案例“vivado_hls\project

2021-02-19 18:36:48

vivado合成bugif我把这个文件(附件)打包到一个pcore,然后我在IP Intergrator.it中使用不能合成right.and一个错误msg命令失败:无法编译设计!“没有更多的其他

2019-03-07 11:05:26

你好。Vivado 2015.1 IP目录包含AXI_interconnect V1.7(默认情况下),同时DIR .. / data / IP / xilinx包含文件

2019-04-08 10:30:32

本文介绍如何在 vivado 开发教程,创建新工程 的基础上, 使用IP集成器, 创建块设计。

2021-02-23 07:02:27

如何在Libero的开发环境下封装通用的自定义的IP核?请各位大侠指点!

2019-11-13 23:09:18

你好我只想知道如何在 linux 中正确卸载以前版本的 CubeIDE。我只是删除文件夹吗?

2023-01-17 06:03:09

如何在全集成设计环境中开发视频IP?

2021-06-08 06:13:55

',它不存在。同时在〜/ ip_repo下检查那里没有multiplier.v文件。如何在打包IP时确保包含所有文件?看起来IP指的是位于IP Packager创建的临时项目中的multiplier.v文件,但此后已被删除。如何使其导出实际文件,然后通过正确的路径引用它?

2020-05-27 09:15:56

你好,我使用Vivado HLS生成了一个IP。从HLS测量的执行和测量的执行时间实际上显着不同。由HLS计算的执行非常小(0.14 ms),但是当我使用AXI计时器在真实场景中测量它时,显示3.20 ms。为什么会有这么多差异? HLS没有告诉实际执行时间?等待回复。问候

2020-05-05 08:01:29

的是如何使用它或将其转移到普通的Vivado项目,这样我就可以应用测试平台并对其进行测试。从我的角度来看,IP块设计是加载IP和进行互连的好方法。但是,使用它还需要其他步骤。我错了吗?我花了几个星期的时间尝试将

2020-03-20 08:52:30

我相信AXI Interconnect 2.1是Vivado 2013.3的最新产品吗?但是,只有1.7版本出现在IP目录中(针对Virtex 7 690T的项目)。我可以在data / ip下看到

2019-03-06 14:25:12

案例的使用说明,适用开发环境: Windows 7/10 64bit、Xilinx Vivado2017.4 、Xilinx Vivado HLS 2017.4 、Xilinx SDK 2017.4

2023-01-01 23:52:54

案例的使用说明,适用开发环境: Windows 7/10 64bit、Xilinx Vivado2017.4 、Xilinx Vivado HLS 2017.4 、Xilinx SDK 2017.4

2023-08-24 14:40:42

目 录4 matrix_demo 案例 274.1 HLS 工程说明 274.2 编译与仿真 304.3 综合 314.4 IP 核测试 364.4.1 PL 端 IP 核测试 Vivado 工程

2023-08-24 14:52:17

目 录5 sobel_demo 案例 395.1 HLS 工程说明 405.2 编译与仿真 435.3 IP 核测试 45

前 言本文主要介绍 HLS 案例的使用说明,适用开发环境: Windows

2023-08-24 14:54:01

目 录5 sobel_demo 案例 395.1 HLS 工程说明 405.2 编译与仿真 435.3 IP 核测试 45前 言本文主要介绍 HLS 案例的使用说明,适用开发环境: Windows

2023-01-01 23:46:20

前 言本文主要介绍HLS案例的使用说明,适用开发环境:Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx Vivado HLS 2017.4、Xilinx

2021-11-11 09:38:32

的经验几乎为0,因此我想就如何解决这个问题提出建议。这就是我的想法:1 - 首先,用Vivado HLS转换VHDL中的C代码(我现在有一些经验)2 - 在Vivado HLS中生成IP核(如果我

2020-03-24 08:37:03

你好我正在尝试在vivado HLS中创建一个IP,然后在vivado中使用它每次我运行Export RTL我收到了这个警告警告:[Common 17-204]您的XILINX环境变量未定义。您将

2020-04-03 08:48:23

,System_generator正常工作只有HLS没有启动。我卸载并安装java,我的java版本是1.8更新65也是两次我卸载vivado completly并重新安装它仍然是同样的问题,我检查并纠正所有环境正式路径和所有

2020-04-09 06:00:49

我照着xapp1167文档,用HLS实现fast_corners的opencv算法,并生成IP。然后想把这个算法塞到第三季的CH05_AXI_DMA_OV5640_HDMI上,这个demo里

2017-01-16 09:22:25

你好是否可以在不升级IP内核的情况下,通过较新版本的Vivado打开旧版Vivado?最好的祝福以上来自于谷歌翻译以下为原文HiIs it possible to open the older

2018-12-28 10:30:06

利用Zynq SoC的诸多功能与特性,赛灵思推出了以IP和系统为中心的设计环境Vivado™设计套件。该套件可加速集成和实现,从而可帮助设计人员提高开发生产力,进而动态开发出Smater嵌入式产品

2014-04-21 15:49:33

“hdmi_v1_0”和“hdmi_v2_0”的文件夹,每个文件夹都包含名为“hdmi.xml”和“hdmi_rt.xml”的文件,但我不知道如何使用它们或者它们是否正确。我的计算机上安装了Vivado

2019-01-02 15:02:41

如何在Momentum中正确的添加接地过孔?

2021-06-24 07:53:46

嗨伙计,在我的PC Vivado设计套件2015.2和SDK 2015.2工作,但只有vivado HLS 2015.2没有打开,这就是为什么我想重新安装Vivado HLS 2015.2。如何下载

2018-12-27 10:57:49

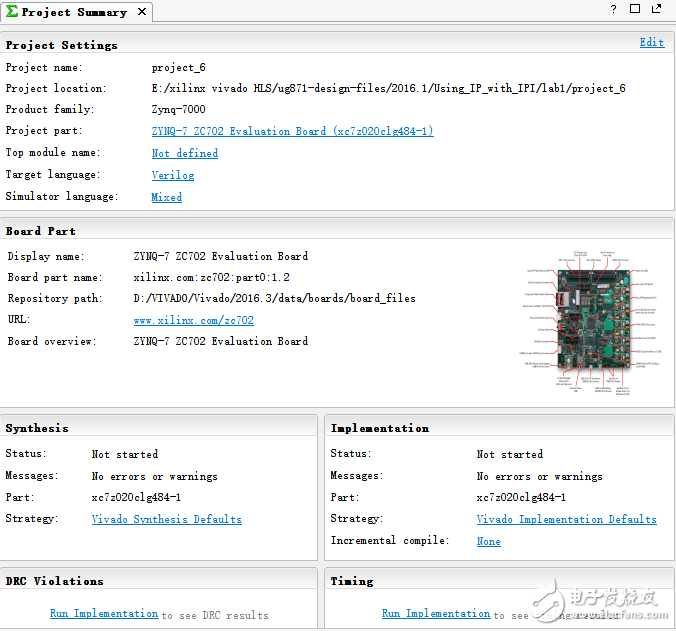

高层次综合设计最常见的的使用就是为CPU创建一个加速器,将在CPU中执行的代码移动到FPGA可编程逻辑去提高性能。本文展示了如何在Zynq AP SoC设计中使用HLS IP。 在Zynq器件

2017-02-07 18:08:11 3207

3207

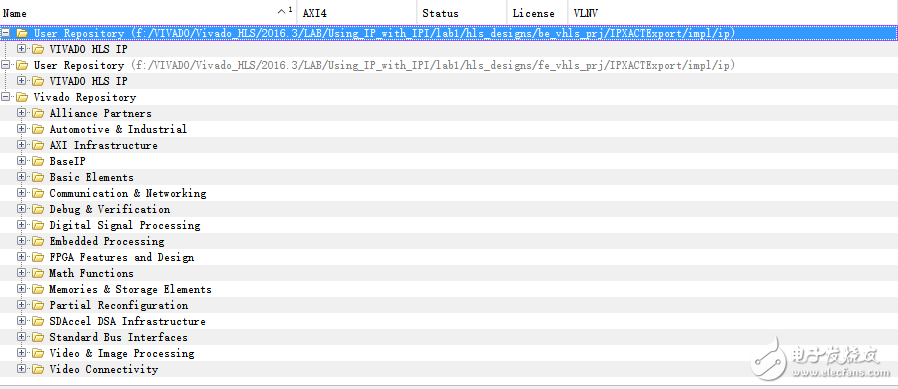

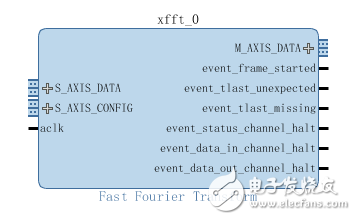

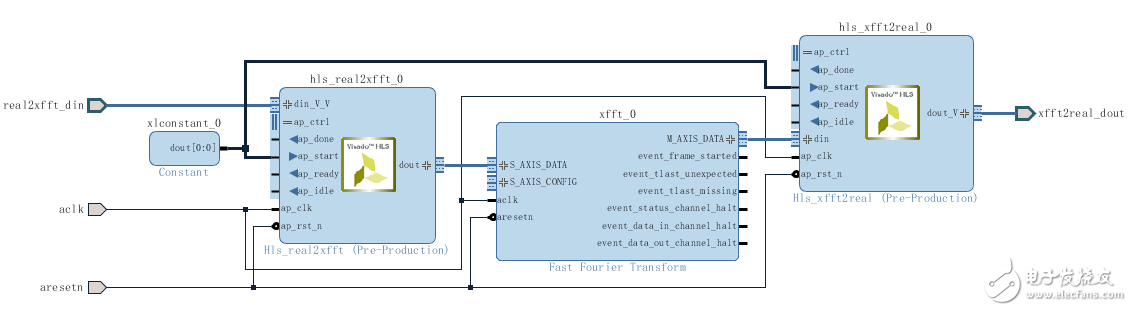

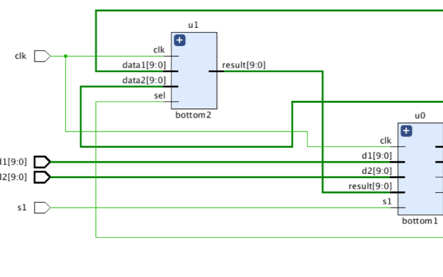

对于硬件加速模块来说,这些硬件加速模块会消耗源于CPU存储器的数据,并且以streaming方式产生数据。本文使用Vivado HLS和xfft IP模块(在IP Integrator使用HLS

2017-02-07 18:13:35 3135

3135 IP核(IP Core) Vivado中有很多IP核可以直接使用,例如数学运算(乘法器、除法器、浮点运算器等)、信号处理(FFT、DFT、DDS等)。IP核类似编程中的函数库(例如C语言

2017-02-08 13:08:11 1235

1235

最新针对市场量身定制的即插即用型 IP 子系统在更高的抽象层上工作,使得平台和系统开发人员能够提高生产力并降低开发成本。新的IP子系统结合Vivado IP Integrator (IPI) 和Vivado

2017-02-09 01:15:42 225

225 有关FPGA——VIVADO15.4开发中IP 的建立

2017-02-28 21:04:35 15

15 IP核(IP Core) Vivado中有很多IP核可以直接使用,例如数学运算(乘法器、除法器、浮点运算器等)、信号处理(FFT、DFT、DDS等)。IP核类似编程中的函数库(例如C语言

2017-11-15 11:19:14 8390

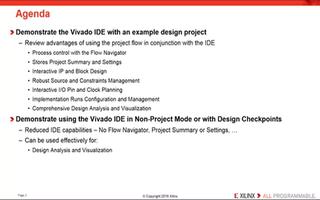

8390 1 Vivado HLS简介 2创建一个Vivado-HLS工程 2.1打开Vivado HLS GUI 2.2创建新工程 在 Welcome Page, 选择Create New Project

2017-12-04 10:07:17 0

0 大家好,又到了每日学习的时间了,今天咱们来聊一聊vivado 调用IP核。 首先咱们来了解一下vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如

2018-05-28 11:42:14 36234

36234 新增了一款以IP为中心的设计环境,用以加速系统集成;而其提供的一套完整数据库,则可加速C/C++系统级设计和高层次综合(HLS)。 加速IP创建与集成 为了加速在All Programmable

2018-09-25 09:18:01 275

275 对于硬件加速模块来说,这些硬件加速模块会消耗源于CPU存储器的数据,并且以streaming方式产生数据。本文使用Vivado HLS和xfft IP模块(在IP Integrator使用HLS

2018-10-02 07:25:11 394

394 欢迎阅读本快速视频,我将解释如何使用Vivado IP Integrator流程与Amazon F1硬件开发套件或HDK配合使用

2018-11-20 06:35:00 2212

2212 此视频概述了Vivado Design Suite中的IP加密。

它涵盖了IP加密工具流程,如何准备加密IP以及如何在Vivado中运行加密工具。

2018-11-20 06:34:00 5948

5948 了解如何在IP Integrator中创建简单的MicroBlaze设计,并创建一个在KC705目标板上运行的简单软件应用程序。

2018-11-20 06:13:00 2836

2836

了解如何生成Vivado HLS IP模块,以便在System Generator For DSP中使用。

2018-11-20 06:08:00 2940

2940 了解如何将Vivado HLS设计作为IP模块整合到System Generator for DSP中。

了解如何将Vivado HLS设计保存为IP模块,并了解如何将此IP轻松整合到System Generator for DSP的设计中。

2018-11-20 05:55:00 2940

2940 了解Vivado中的Logic Debug功能,如何将逻辑调试IP添加到设计中,以及如何使用Vivado Logic Analyzer与逻辑调试IP进行交互。

2018-11-30 06:22:00 3107

3107 了解如何使用Vivado Design Suite IP Integrator有效地调试AXI接口。

本视频介绍了如何使用该工具的好处,所需的调试步骤和演示。

2018-11-29 06:00:00 3680

3680 该视频演示了如何使用Vivado IP Integrator组装具有多个时钟域的设计。

它显示了Vivado中的设计规则检查和功能如何帮助用户自动执行此流程。

2018-11-27 07:40:00 3539

3539 ADI公司在Embedded World 2015上展示了采用Zynq SDR套件的DDS HLS IP

2018-11-30 06:44:00 3026

3026 DAVE嵌入式系统在嵌入式世界2015中展示了Matrix多重HLS IP和DAVE Bora套件

2018-11-30 06:43:00 2010

2010 iVeia使用嵌入式世界2015中的iVeia视觉套件演示了Canny边缘检测HLS IP

2018-11-30 06:41:00 2648

2648 本视频介绍了使用IP Integrator(IPI)创建简单硬件设计的过程。

使用IPI可以无缝,快速地实现DDR4和PCIe等块

连接在一起,在几分钟内创建硬件设计。

2018-11-22 06:13:00 4157

4157

在本教程中,我们将来聊一聊有关如何在 Vitis HLS 中使用 AXI4-Lite 接口创建定制 IP 的基础知识。

2020-09-13 10:04:19 5961

5961

Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP

2020-12-29 15:59:39 9496

9496 在Vitis HLS下,一个Solution的Flow Target可以是Vivado IP Flow Target,也可以是VitisKernel Flow Target,如下图所示。前者最终导出来

2020-11-05 17:43:16 37066

37066 本文介绍如何在 vivado 开发教程(一) 创建新工程 的基础上, 使用IP集成器, 创建块设计。

2022-02-08 10:47:39 2090

2090

前年,发表了一篇文章《VCS独立仿真Vivado IP核的一些方法总结》(链接在参考资料1),里面简单讲述了使用VCS仿真Vivado IP核时遇到的一些问题及解决方案,发表之后经过一年多操作上也有

2021-03-22 10:31:16 3409

3409 以供在 Vivado Design Suite 中使用、如何将其连接到其它 IP 核与处理器以及如何在板上运行工程。 本篇博文将分为 3 个部分: 1. 从 Vitis HLS 导出 IP。 2.

2021-04-26 17:32:26 3506

3506

在FPGA实际的开发中,官方提供的IP并不是适用于所有的情况,需要根据实际修改,或者是在自己设计的IP时,需要再次调用时,我们可以将之前的设计封装成自定义IP,然后在之后的设计中继续使用此IP。因此本次详细介绍使用VIvado来封装自己的IP,并使用IP创建工程。

2022-04-21 08:58:05 4579

4579 在本篇博文中,我们将学习如何导出 IP 以供在 Vivado Design Suite 中使用、如何将其连接到其它 IP 核与处理器以及如何在板上运行工程。

2022-07-08 09:34:00 2023

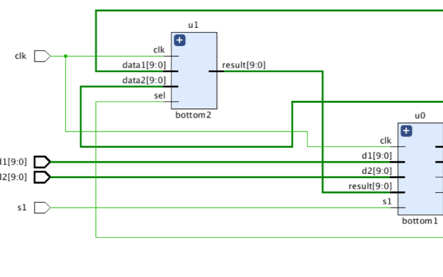

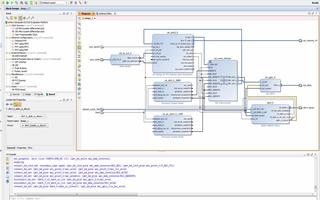

2023 Vivado IPI (IP Integrator)提供了直观的模块化的设计方法。用户可以将Vivado IP Catalog中的IP、用户自己的RTL代码、或者用户已有的BD文件添加到IP Integrator中构成Block Design,设计更复杂的系统,如下图所示。

2022-07-15 11:39:12 1335

1335 以供在 Vivado Design Suite 中使用、如何将其连接到其它 IP 核与处理器以及如何在板上运行工程。

2022-08-02 09:43:05 579

579

前年,发表了一篇文章《VCS独立仿真Vivado IP核的一些方法总结》(链接在参考资料1),里面简单讲述了使用VCS仿真Vivado IP核时遇到的一些问题及解决方案,发表之后经过一年多操作上也有些许改进,所以写这篇文章补充下。

2022-08-29 14:41:55 1549

1549 这里向大家介绍使用HLS封装的缩放IP来实现视频图像缩放功能。将HLS封装的缩放IP加入到OV5640图像传输系统,验证图像放大和缩小功能。

2022-10-11 14:21:50 1517

1517 在仿真Vivado IP核时分两种情况,分为未使用SECURE IP核和使用了SECURE IP核。

2023-06-06 14:45:43 1240

1240

在仿真Vivado IP核时分两种情况,分为未使用SECURE IP核和使用了SECURE IP核。

2023-06-20 14:23:57 622

622

Xilinx平台的Vivado HLS 和 Vitis HLS 使用的 export_ip 命令会无法导出 IP

2023-07-07 14:14:57 338

338

Vivado IP核提供了强大的FIFO生成器,可以通过图形化配置快速生成FIFO IP核。

2023-08-07 15:36:28 1628

1628

FPGA开发中使用频率非常高的两个IP就是FIFO和BRAM,上一篇文章中已经详细介绍了Vivado FIFO IP,今天我们来聊一聊BRAM IP。

2023-08-29 16:41:49 2605

2605

在给Vivado中的一些IP核进行配置的时候,发现有Shared Logic这一项,这里以Tri Mode Ethernet MAC IP核为例,如图1所示。

2023-09-06 17:05:12 529

529

电子发烧友网站提供《将VIVADO HLS设计移植到CATAPULT HLS平台.pdf》资料免费下载

2023-09-13 09:12:46 2

2 Vivado是Xilinx公司2012年推出的新一代集成开发环境,它强调系统级的设计思想及以IP为核心的设计理念,突出IP核在数字系统设计中的作用。

2023-09-17 15:37:31 1060

1060

文章是基于Vivado的 2017.1的版本,其他版本都大同小异。 首先在Vivado界面的右侧选择IP Catalog 选项。

2023-12-05 15:05:02 317

317

电子发烧友App

电子发烧友App

评论