FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。对于时序如何用FPGA来分析与设计,本文将详细介绍。

2017-06-21 16:05:57 7800

7800

同步电路设计中,时序是一个主要的考虑因素,它影响了电路的性能和功能。为了验证电路是否能在最坏情况下满足时序要求,我们需要进行静态时序分析,即不依赖于测试向量和动态仿真,而只根据每个逻辑门的最大延迟来检查所有可能的时序违规路径。

2023-06-28 09:35:37 490

490

这篇文章是探讨对接收端进行时序优化(即ready打拍,或称backward打拍)的方式。

2023-12-04 10:20:55 234

234

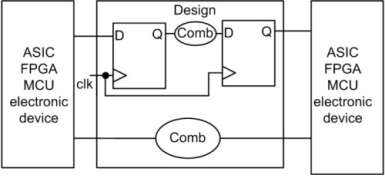

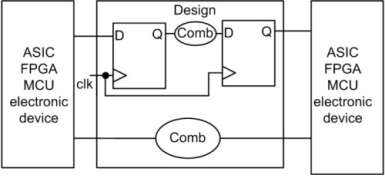

逻辑功能,若电路存在问题,并提出改进方法。在分析同步时序电路时分为以下几个步骤:分清时序电路的组成.列出方程. 根据时序电路的组合部分,写出该时电路的输出函数表达式.并确定触发器输入信号的逻辑表达式

2018-08-23 10:28:59

在进行数字电路系统的设计时,时序是否能够满足要求直接影响着电路的功能和性能。本文首先讲解了时序分析中重要的概念,并将这些概念同数字系统的性能联系起来,最后结合FPGA的设计指出时序约束的内容和时序

2020-08-16 07:25:02

Cadence高速PCB布线时的时序分析列位看观,在上一次的连载中,我们介绍了什么是时序电路,时序分析的两种分类(同步和异步),并讲述了一些关于SDRAM 的基本概念。这一次的连载中,我们将介绍

2009-07-01 17:26:16

文章目录EEPROM 多字节读写操作时序EEPROM 多字节读写操作时序我们读取 EEPROM 的时候很简单,EEPROM 根据我们所送的时序,直接就把数据送出来了,但是写 EEPROM 却没有

2021-11-24 07:01:10

地传送到接收端,就必须进行精确的时序计算和分析。同时,时序和信号完整性也是密不可分的,良好的信号质量是确保稳定的时序的关键,由于反射,串扰造成的信号质量问题都很可能带来时序的偏移和紊乱。因此,对于一个信号

2012-08-11 17:55:55

的方法一般有四个步骤:时序分析→时序约束→时序报告→时序收敛。

为什么要进行时序分析?

信号在系统中传输时由于经过一些逻辑器件和PCB上的走线会造成一定的逻辑延时和路径延时,如果系统要求信号

2011-09-23 10:26:01

控。从最近一段时间工作和学习的成果中,我总结了如下几种进行时序约束的方法。按照从易到难的顺序排列如下:0. 核心频率约束 这是最基本的,所以标号为0。1. 核心频率约束+时序例外约束 时序例外约束包括

2016-06-02 15:54:04

在进行FPGA的设计时,经常会需要在综合、实现的阶段添加约束,以便能够控制综合、实现过程,使设计满足我们需要的运行速度、引脚位置等要求。通常的做法是设计编写约束文件并导入到综合实现工具,在进行

2023-09-21 07:45:57

时。与综合过程相似,静态时序分析也是一个重复的过程,它与布局布线步骤紧密相连,这个操作通常要进行多次直到时序约束得到很好的满足。在综合与时序仿真过程中交互使用PrimeTime进行时序分析,满足设计要求后

2018-08-29 09:59:08

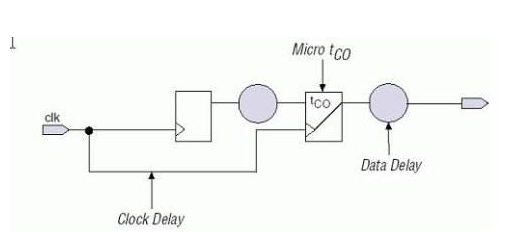

提高工作频率。3. 理论分析3.1静态时序分析的理论基础知识 在进行正确的时序分析前,我们必须具备基本的静态时序的基本知识点,不然看着编译器给出的时序分析报告犹如天书。如图3.1所示,为libero软件

2012-01-11 11:43:06

Modelsim库的概念,分析一下Quartus II自动完成仿真的代码,最后能自己写一些简单的do文件利用我们添加的仿真库自动进行时序仿真。前两个部分是简单的操作,掌握其中一个部分即可进行时序仿真。最后

2012-02-01 11:37:40

对原理图进行时序仿真时,需要通过Node Finder把引脚置入时序仿真列表中,在Node Finder里面的list中缺少了Q端(Q0~Q7)的引脚,一直没弄明白这是怎么回事!(设计的是频率计,进行了前部分仿真,2位十进制计数器counter8和频率计主结构ft_top的设计,后面没做)

2011-10-27 13:19:14

在初始化完成之后,对SDRAM进行读或者写操作之前,我们还需要有一个命令”ACT”(这个命令在我们的初始化时序图中也出现了,只是我们是拿到了这里来讲),这个命令的意思说成大白话就是”行有效”命令,就是让

2019-01-24 06:35:14

自己做了一个工程,静态时序分析的结果CLK信号的SLACK是负值(-7.399ns),书上说该值是负值时说明时序不对,但是我感觉时序仿真的结果是对的。是不是时序仿真波形正确就不用管静态时序分析的结果了?请高手指点

2010-03-03 23:22:24

在学习fpga的过程中的疑问:1、在功能仿真和板级验真后没问题,还需要进行时序分析吗2、怎么知道自己写的代码有时序问题?

2017-01-08 17:50:35

请教大牛,在用quartus II 9.1时进行时序约束时一按闹钟按钮打开time quest界面时程序就卡死了,不知道哪里出问题了,请教大牛应该怎莫办才好

2019-03-06 06:35:15

请问我已经create了一个bdf文件,怎么对它进行时序分析?

2016-10-08 20:15:41

我只有非常有限的知识来使用tcl命令进行时序分析(不用于时序约束,仅用于时序分析)。这些命令如下:check_timingreport_timing_summary我希望知道一些最常见的tcl命令来

2019-03-11 13:41:27

转自:VIVADO时序分析练习时序分析在FPGA设计中是分析工程很重要的手段,时序分析的原理和相关的公式小编在这里不再介绍,这篇文章是小编在练习VIVADO软件时序分析的笔记,小编这里

2018-08-22 11:45:54

Verilog HDL 中进行时序控制分别通过下面两种方式进行:• 延时控制;• 事件控制。延时控制的语法如下:#delay procedural_statement延时控制定义为执行过程中首次遇到

2018-09-25 09:16:12

直接输出。电路图层面,组合逻辑为一个加法器连接a和b,紧接着立刻给到c,如下图所示,可以看到a+b得出的值c直接输出,没有进行任何额外操作:时序逻辑的电路图加法器连接的a和b没有变,但是c的值在输出部分

2020-03-01 19:50:27

的触发功能● 强大的分析功能

逻辑分析仪在中可以分为4个层次:1、观察波形观察测量波形中是否存在毛刺、干扰,频率是否正确等。2、时序测量对被测量信号进行时序分析,排除操作冲突、时序协调等问题。3、辅助分析

2017-10-13 09:23:54

我们都知道在学校是通过铃声来控制所有班级的上下课时间,那个单片机是通过什么样的办法进行取指令,执行指令和其它操作的呢?在这里引入了一个时序的概念:一、时钟电路单片机时钟电路有三种方式:1、单片机

2018-07-21 16:38:31

工具,利用它可以达到更好的效果。将综合后的网表文件保存为db格式,可在PrimeTIme环境下打开。利用此软件查看关键路径或设计者感兴趣的通路的时序,并对其进行分析,再次对原来的设计进行时序结束,可以

2021-05-27 09:28:40

各位好,初次使用pt对fpga进行静态时序分析,想请教下需要哪些文件。是不是需要:1、在ise或qutartus生成的网表2、SDC文件3、.db文件.db文件必须且只能从dc生成吗,要是从.lib转化而来,这个lib文件在fpga设计时又从哪里得到问题貌似比较多,谢谢回答

2014-12-18 16:15:12

`问题1:对 motion control 模块进行时序分析,提示时序有问题,而且时序仿真中发现有个子模块的常量输入显示为高阻态,但是做时序仿真出来的结果缺是对的。问题2:对顶层模块

2017-08-22 09:56:54

挑战。本文主要介绍了逻辑设计中值得注意的重要时序问题,以及如何克服这些问题。最后介绍了利用Astro工具进行时序分析的方法。关键词:ASIC;同步数字电路;时序;Astro引言 随着系统时钟频率的提高

2012-11-09 19:04:35

数据集进行模型的构建与预测分析的,但是在实际的工程使用中会有一种特殊的情况就是:我们通过实验所采集到的数据集往往不是绝对连续的而是多“片段”的。何为 “片段”?以我之前的时序建模相关的文章来讲,诸如:气象数据预测、风力发电数据预测等等,都是具有一定数据规模的数据进行时序预测模型的构建,...

2021-06-30 07:52:16

,不同的寄存器在时钟脉冲的激励下相互配合完成特定的功能,所以要保证不同的寄存器在同一时刻的时钟脉冲激励下协同工作,就需要进行时序分析,通过分析得结果对FPGA进行约束,以保证不同寄存器间的时序要求

2017-02-26 09:42:48

ser-des核心工作在2.5 GHz。我使用了一个简单的包装器,它有clock,reset,tx& amp; rx串行信号用于环回,Tx并行数据输入和Rx并行数据输出。我该如何设置约束?请建议如何进行时序收敛,即如何确保生成的内核工作在2.5GHz。问候CJ

2020-06-03 11:24:21

你好,我有两个设计,一个工作在250MHz,另一个工作在450 MHz ......面积不大..我想知道如何为特定的fpga设备进行时序估计。要在fpga上实现特定的设计,我应该知道我的设计是否适合

2020-06-12 14:40:33

nRF24L01+ 2.4GHz无线收发器的主要特性有哪些?如何使用SPI?如何对SPI的操作时序进行读写呢?

2021-12-20 06:32:33

逻辑。而对其进行时序分析时,一般都以时钟为参考的,因此一般主要分析上半部分。在进行时序分析之前,需要了解时序分析的一些基本概念,如时钟抖动、时钟偏斜(Tskew)、建立时间(Tsu)、保持时间(Th)等

2018-04-03 11:19:08

片上系统(SoC) IC的广泛使用,对电源进行时序控制和管理变得越来越重要,今天我们来谈一下这个问题?欢迎大家留言一起交流

2019-11-12 10:07:54

以下针对目前项目所用到的SRAM时序进行分析,同时也对SRAM应用在STM32F4上进行详细解说。以此也可以类推出NAND/PSRAM等时序的应用技巧。时序当前用到的是模式A,其中读时序如下。图片截

2022-01-07 07:20:20

问一下啊,在写时序约束的时候,如何根据设计的要求进行时序上的约束啊,看了好多网上的资料,说的都是有关约束的一些原理。有没有那位大侠给个设计实例啊!

2023-04-23 11:42:16

一定难度,因此我将我的实习作品展示在此,希望对学弟学妹或者其他同学们有一定的帮助。一:题目分析左侧的8位数字信号发生电路我们使用硬件电路,右侧的时序分析装置我们使用单片机进行操作。##1.八位数字信号发生电路在给定的初步方案中,已经学校已经给出了相关的电路信息...

2021-08-09 08:33:45

在培训指南、模式方面完全模拟真实的AED,目的在于帮助急救人员熟悉AED,并掌握在急救过程中使用AED的一些必备的基础操作技能。CPR反馈功能:美国心脏协会(AHA)认为,早期识别并给予心肺复苏是患者

2021-06-19 17:37:06

请教如何做时序分析

2013-06-01 22:45:04

工具,利用它可以达到更好的效果。将综合后的网表文件保存为db格式,可在PrimeTIme环境下打开。利用此软件查看关键路径或设计者感兴趣的通路的时序,并对其进行分析,再次对原来的设计进行时序结束,可以

2019-05-03 08:00:00

工具,利用它可以达到更好的效果。将综合后的网表文件保存为db格式,可在PrimeTIme环境下打开。利用此软件查看关键路径或设计者感兴趣的通路的时序,并对其进行分析,再次对原来的设计进行时序结束,可以

2021-06-24 08:00:01

使用EDA工具Prime Time进行时序分析和sign-off,掌握识别不完整/不正确约束、高效分析与调试的方法和实践技巧,并掌握POCV、AWP、DSMA等高级时序方法和信号完整性分析。本次培训讲师为

2020-09-01 16:51:01

而又美好,那么我们这么多学费就没白交哈~ 下面我们进入正题,今天我们讲时序一、从静态时序分析说起 我理解的静态时序分析,就是我们在不加激励的情况下,通过对电路进行时序的延迟计算,预计电路的工作流

2015-03-31 10:20:00

PathsSTA无法检查不受约束的路径上的任何时序,因此需要约束所有路径以进行时序分析。实际情况中,设计人员可能并不在乎一些输入控制信号的时序,因此可能并不需要进行本节中将要介绍的时序检查。但是,本节假定我们

2023-04-20 16:17:54

进行分析,而不能对异步电路进行时序分析。但是它却可以验证每一条路径,发现时序的重大问题,比如建立时间和保持时间冲突,slow path以及过大的时钟偏移。 静态时序分析的优缺点静态时序分析可以大大提高

2021-09-04 14:26:52

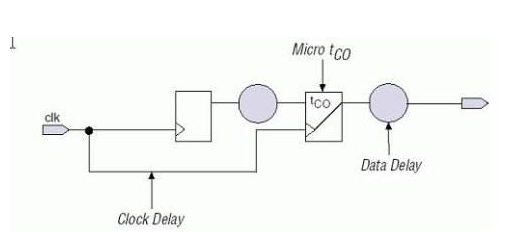

高速电路的时序分析电路中,数据的传输一般都是在时钟对数据信号进行有序的收发控制下进行的。芯片只能按规定的时序发送和接收数据,过长的信号延迟或信号延时匹配不当都会影响芯片的建立和保持时间,导致芯片无法

2012-08-02 22:26:06

Cadence高速PCB的时序分析:列位看观,在上一次的连载中,我们介绍了什么是时序电路,时序分析的两种分类(同步和异步),并讲述了一些关于SDRAM 的基本概念。这一次的连载中,

2009-07-01 17:23:27 0

0 Cadence 高速 PCB 的时序分析 1.引言 时序分析,也许是 SI 分析中难度最大的一部分。我怀着满腔的期许给 Cadence 的资深工程师发了一封 e-mail,希望能够得到一份时序分析的案

2010-04-05 06:37:13 0

0 时序约束与时序分析 ppt教程

本章概要:时序约束与时序分析基础常用时序概念QuartusII中的时序分析报告

设置时序约束全局时序约束个别时

2010-05-17 16:08:02 0

0 本文首先以Synopsys公司的工具Prime Time SI为基础,介绍了ASIC设计中主流的时序分析方法:静态时序分析及其基本原理和操作流程;接着分析了它与门级仿真之间的关系,提出了几个在T

2010-08-02 16:44:16 10

10

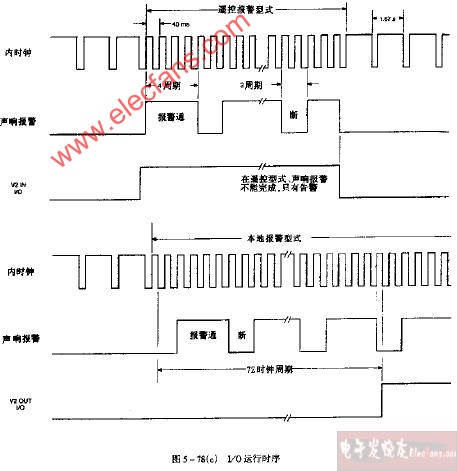

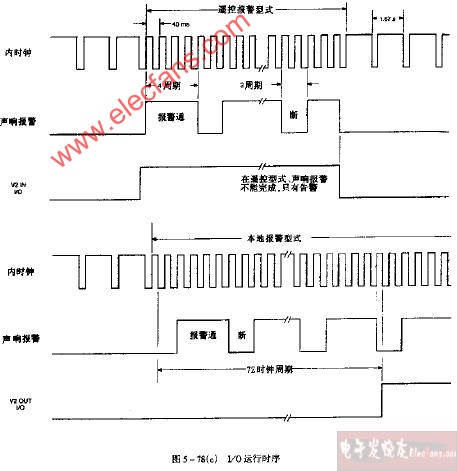

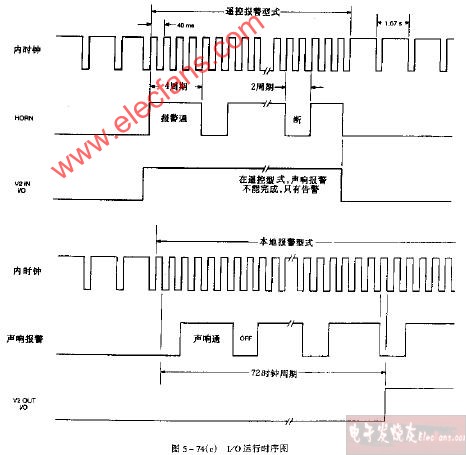

A5347 IO运行时序电路图

2009-07-03 12:03:29 440

440

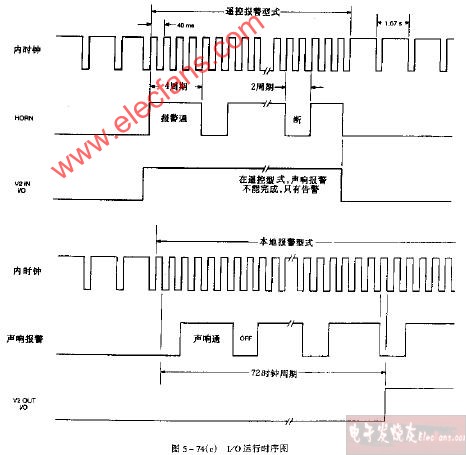

A5348 IO运行时序电路图

2009-07-03 12:11:10 393

393

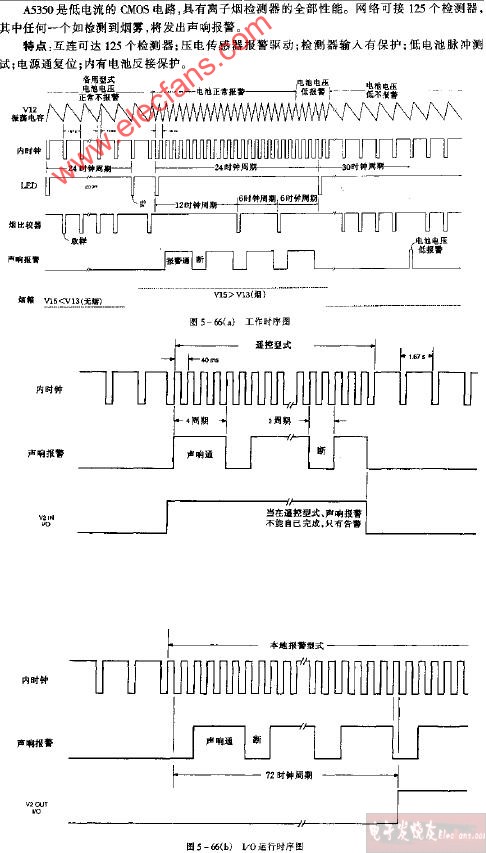

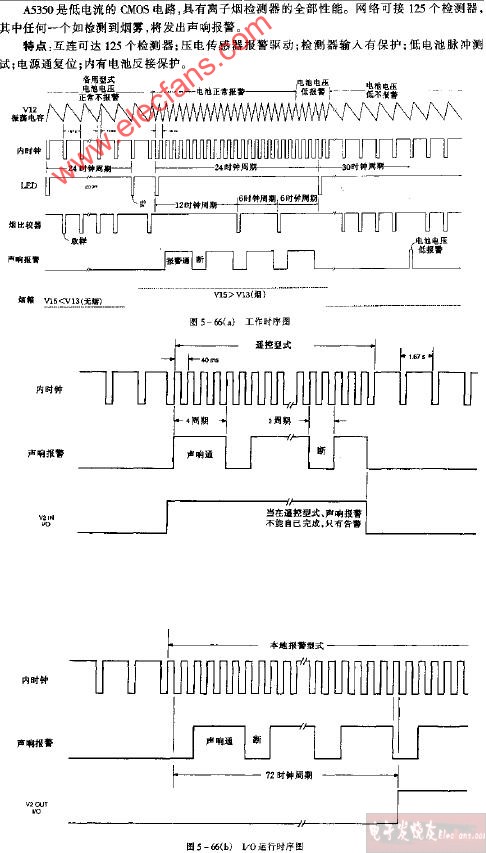

A5350 IO运行时序电路图

2009-07-03 12:20:26 484

484

跳变点是所有重要时序分析工具中的一个重要概念。跳变点被时序分析工具用来计算设计节点上的时延与过渡值。跳变点的有些不同含义可能会被时序分析工程师忽略。而这

2010-09-15 10:48:06 1461

1461

介绍了采用STA (静态时序分析)对FPGA (现场可编程门阵列)设计进行时序验证的基本原理,并介绍了几种与STA相关联的时序约束。针对时序不满足的情况,提出了几种常用的促进 时序收敛的方

2011-05-27 08:58:50 70

70 本文通过对源同步时序公式的推导,结合对SPECCTRAQuest 时序仿真方法的分析,推导出了使用SPECCTRAQuest 进行时序仿真时的计算公式,并对公式的使用进行了说明。 通常我们在时序仿真中

2011-07-12 10:05:52 97

97 讨论了静态时序分析算法及其在IC 设计中的应用。首先,文章讨论了静态时序分析中的伪路径问题以及路径敏化算法,分析了影响逻辑门和互连线延时的因素。最后通过一个完整的IC 设计

2011-12-20 11:03:16 95

95 ddr2_sdram 操作时序,非常好的教程,可以充分了解DDR2

2015-10-28 11:07:39 19

19 _静态时序分析(Static_Timing_Analysis)基础及应用[1]。

2016-05-09 10:59:26 31

31 基于时序路径的FPGA时序分析技术研究_周珊

2017-01-03 17:41:58 2

2 静态时序分析基础及应用

2017-01-24 16:54:24 7

7 在ISE 中可以进行时序分析,在PlanAhead 中同样也可以进行时序分析。下面介绍用PlanAhead 进行时序分析的步骤。

2017-02-11 06:13:11 437

437

FPGA,即现场可编程门阵列,它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。对于时序如何用FPGA来分析与设计,本文将详细介绍。

2017-06-30 15:09:36 28

28 从最近一段时间工作和学习的成果中,我总结了如下几种进行时序约束的方法。按照从易到难的顺序排列如下:

2018-08-07 14:14:00 13908

13908

时序分析在FPGA设计中是分析工程很重要的手段,时序分析的原理和相关的公式小编在这里不再介绍,这篇文章是小编在练习Vivado软件时序分析的笔记,小编这里使用的是18.1版本的Vivado。 这次

2019-09-15 16:38:00 5787

5787

TimeQuest时序约束是作用在门级网表上的,因此在进行时序约束前应该首先编译一边工程,之后进行时序约束并再次编译进行时序分析,直至无时序错误为止,之后烧写工程下板子。

2019-12-19 07:03:00 1151

1151

TimeQuest Timing Analyzer是一个功能强大的,ASIC-style的时序分析工具。采用工业标准--SDC(synopsys design contraints)--的约束、分析和报告方法来验证你的设计是否满足时序设计的要求。

2019-11-28 07:09:00 1753

1753 TimeQuest时序约束是作用在门级网表上的,因此在进行时序约束前应该首先编译一边工程,之后进行时序约束并再次编译进行时序分析,直至无时序错误为止,之后烧写工程下板子。

2019-12-12 07:06:00 1372

1372

干的活!)。无需用向量(激励)去激活某个路径,分析工具会对所有的时序路径进行错误分析,能处理百万门级的设计,分析速度比时序仿真工具块几个数量级。

2019-11-22 07:07:00 3179

3179 TimeQuest时序约束是作用在门级网表上的,因此在进行时序约束前应该首先编译一边工程,之后进行时序约束并再次编译进行时序分析,直至无时序错误为止,之后烧写工程下板子。

2019-11-15 07:05:00 2984

2984

时序分析是以分析时间序列的发展过程、方向和趋势,预测将来时域可能达到的目标的方法。此方法运用概率统计中时间序列分析原理和技术,利用时序系统的数据相关性,建立相应的数学模型,描述系统的时序状态,以预测未来。

2019-11-15 07:02:00 2570

2570

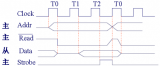

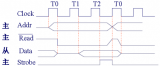

操作时序(timing):各信号有效的先后顺序及配合关系

2019-06-24 16:21:45 10207

10207

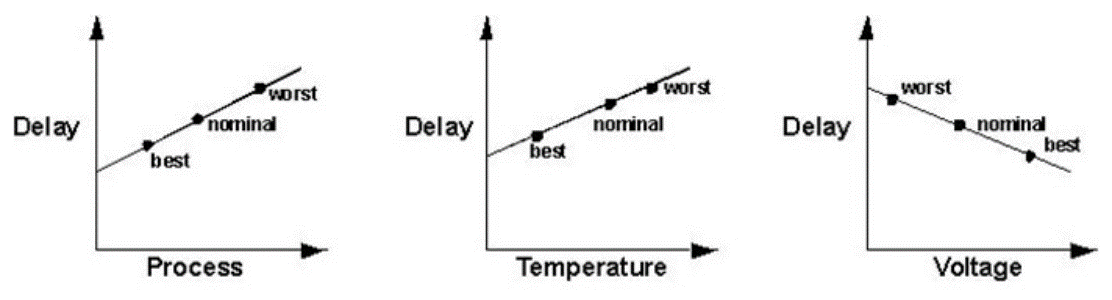

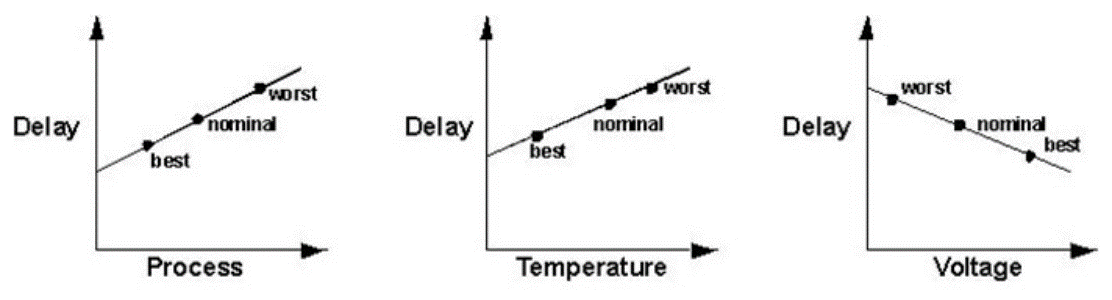

即便是同一种FF,在同一个芯片上不同操作条件下的延时都不尽相同,我们称这种现象为OCV(on-chip variation)。OCV表示的是芯片内部的时序偏差,虽然很细小,但是也必须严格考虑到时序分析中去。

2019-07-25 11:22:30 4462

4462

静态时序分析简称STA,它是一种穷尽的分析方法,它按照同步电路设计的要求,根据电路网表的拓扑结构,计算并检查电路中每一个DFF(触发器)的建立和保持时间以及其他基于路径的时延要求是否满足。

2019-09-01 10:45:27 2942

2942

上面我们讲的都是xdc文件的方式进行时序约束,Vivado中还提供了两种图形界面的方式,帮我们进行时序约束:时序约束编辑器(Edit Timing Constraints )和时序约束向导(Constraints Wizard)。两者都可以在综合或实现后的Design中打开。

2020-03-08 17:17:00 19067

19067

静态时序分析是检查芯片时序特性的一种方法,可以用来检查信号在芯片中的传播是否符合时序约束的要求。相比于动态时序分析,静态时序分析不需要测试矢量,而是直接对芯片的时序进行约束,然后通过时序分析工具给出

2020-11-11 08:00:00 58

58 本文档的主要内容详细介绍的是时序分析的静态分析基础教程。

2021-01-14 16:04:00 14

14 方法,能够有效减少时序路径问题分析所需工作量。 时序路径问题分析定义为通过调查一条或多条具有负裕量的时序路径来判断达成时序收敛的方法。当设计无法达成时序收敛时,作为分析步骤的第一步,不应对个别时序路径进行详细时序分

2021-05-19 11:25:47 2677

2677

时序冲突的概率变大以及电路的稳定性降低,为此必须进行时序、面积和负载等多方面的约束。

2021-06-15 11:24:05 2874

2874

一、前言 无论是FPGA应用开发还是数字IC设计,时序约束和静态时序分析(STA)都是十分重要的设计环节。在FPGA设计中,可以在综合后和实现后进行STA来查看设计是否能满足时序上的要求。

2021-08-10 09:33:10 4768

4768

左边的电路图是需要分析的电路,我们的目的是要对此电路进行时序分析,那首先要找到该电路需要分析的时序路径,既然找路径,那找到时序分析的起点与终点即可。

2022-05-04 17:13:00 1827

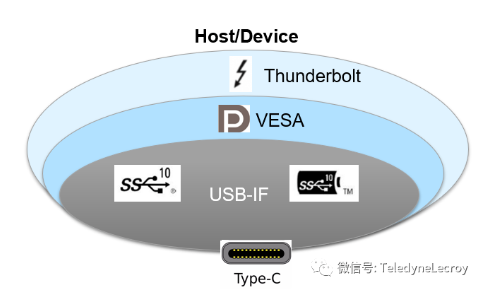

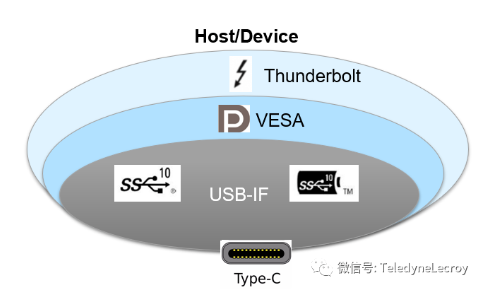

1827 越来越多的串行数据分析涉及到系统中同时运行的多个协议的互操作性。USB-C就是这样的一个接口,本文我们介绍使用力科示波器TDMP分析软件进行跨协议的时序测量。

2022-04-29 15:13:27 2932

2932

另一种是手动的方式,在大型设计中,设计人员一般会采用手动方式进行静态时序分析。手动分析方式既可以通过菜单操作(个人理解:通过鼠标点击和键盘输入)进行分析,也可以采用Tcl脚本(工具控制语言,个人理解运用代码控制)进行约束和分析。

2022-08-19 17:10:25 1360

1360 时序约束是我们对FPGA设计的要求和期望,例如,我们希望FPGA设计可以工作在多快的时钟频率下等等。因此,在时序分析工具开始对我们的FPGA设计进行时序分析前,我们必须为其提供相关的时序约束信息

2022-12-28 15:18:38 1893

1893 主要针对E5071C进行时域测试的详细操作步骤.编写本测试程序是为了说明如何使用Keysight ENA Option TDR

进行100BASE-TX以太网电缆测量。

2023-03-06 15:49:10 5

5 引言 在同步电路设计中,时序是一个非常重要的因素,它决定了电路能否以预期的时钟速率运行。为了验证电路的时序性能,我们需要进行 静态时序分析 ,即 在最坏情况下检查所有可能的时序违规路径,而不需要测试

2023-06-28 09:38:57 714

714

在离线分析的过程中,可能会对两个不同的信号进行时间上同步,本文以举例的形式介绍,如何使用 CANape 或者 vSignalyzer 对不同的信号进行时间同步。

2023-10-13 12:28:59 1155

1155

电子发烧友网站提供《分立式元件对电源进行时序控制的优缺点.pdf》资料免费下载

2023-11-29 11:36:07 0

0

电子发烧友App

电子发烧友App

评论