我们如何为4脚设置参考电压呢?之前有说到过可以使用电阻的分压来实现不同数值的电压。

2019-05-24 07:29:00 5152

5152

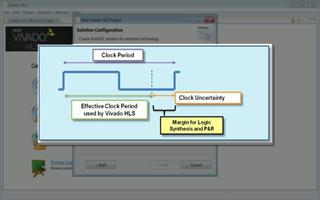

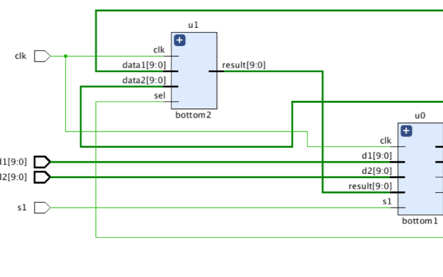

综合(Synthesis)是指将RTL设计转换为门级描述。Vivado开发套件中的综合工具是一款时序驱动型、专为内存使用率和性能优化的综合工具,支持System Verilog 2012

2020-12-29 14:07:42 5432

5432 设计技巧:在 Vivado Synthesis 中使用 SystemVerilog 接口连接逻辑

2019-07-02 12:03:07 10999

10999

X如何在XC8中包含“文件”工作?看起来XC8使用当前的工作目录(正在编译的文件目录)作为搜索路径的一部分,我期待使用标准的(GCC)方法来执行执行包含“文件”的文件的目录。是否有一种方法来配置包含

2018-12-28 15:47:55

Verilog Synthesis Methodology

2012-08-15 15:31:23

嗨,我正在使用vivado 2013.4并且在实现后从触发器的Q引脚到180个负载(RAMB36E1上的ENBWREN引脚)获得高扇出网络。它符合时间,但是,我希望网络能够得到缓冲。1.有没有

2018-10-18 14:28:10

时,我收到此错误:[Common 17-345]找不到功能'Synthesis'和/或设备'xc7a100t'的有效许可证。请运行Vivado License Manager以获取有关确定哪些功能

2019-01-04 11:22:04

17-345] A有效未找到功能'Synthesis'和/或设备'xc7z010'的许可证。请运行Vivado许可证管理器以获取有关确定哪些功能和设备已获得系统许可的帮助。解决方案:在Vivado许可证

2018-12-25 11:03:50

功能'Synthesis'和/或设备'xc7a35t'的有效许可证。请运行Vivado许可证管理器以获取有关确定系统许可的功能和设备的帮助。解决方案:在Vivado License Manager中检查

2018-12-26 11:30:48

你能否告诉我,自2014年4月以来Vivado 2016.3中对任何System Verilog功能的支持是否有所改变?你能告诉我这段代码是否适用于2014.4?interface ibb_if

2020-05-14 08:57:57

你好,在Vivado 2016.4中运行Synthesis功能时,我收到了有效的许可证错误[Common 17-345]。请参阅附件和帮助。谢谢,Gursimar合成日志file.txt 2 KB

2019-01-04 11:22:27

的布线延迟。在上一个项目中,如果路由在FPGA内部进行,则很难平衡4中的所有延迟。每次更改HDL源代码时,ISE / PlanAhead 14.3中每个生成的比特流的路由都不同。由于这个困难,4条线从

2018-10-26 15:08:50

嗨,在我的Vivado实现tcl脚本中,以下行导致错误:设置SRC_PATH ./input.............#Input the netlistread_edif $ SRC_PATH

2018-10-18 14:26:39

在ISE中可以设置状态机安全模式 safe impementation模式,但是在Vivado中有没有类似的设置?我现在一段代码中可以跑到else,但是 偶尔会跑不到ifs_state_4这个状态机。。有大佬知道是为什么么?

2020-11-09 15:25:41

: No error这个错误出现的原因是工程的路径名太长,超过了80个字符。解决方法也很简单,缩短工程路径即可。Vivado在编写和genvar有关的代码时,出现的错误:[Synth 8-196

2021-07-31 09:09:20

我已经下载了电路板文件并将它们添加到board_files文件夹中,如从此链接获得的pdf中所述。 - 根据thislink,在vivado安装文件夹内的scripts文件夹中添加了带有

2018-12-28 10:52:41

在Vivado中进行HDL代码设计,不仅需要描述数字逻辑电路中的常用功能,还要考虑如何发挥Xilinx器件的架构优势。目前常用的HDL语言有三种。VHDL语言的优势有:语法规则更加严格;在HDL

2020-09-29 10:08:57

回到ISE, 我们可以做的一件事是路由设计,然后为设计生成约束文件,过去对这些较小的部件有用,看看工具如何连接引脚,给出了一个起点,我怎么在Vivado做这个?在vhdl / ip块中输入设计,模拟

2018-10-22 11:19:29

…。(不同Vivado版本可能Write Tcl菜单位置会有不同,但是都在File菜单中)弹出的WriteProject to Tcl文件夹,在Output File中设置当前工程路径,并输入.tcl为后缀

2020-08-17 08:41:25

。除了手动技术映射之外,我还使用分层RLOC来管理这些模块的放置,从而获得快速且确定性的PAR运行,并从我的关键路径中削减数十个百分点。在我的设计中,通常> 50%的基元是手工技术映射和/或手工放置

2018-11-06 11:40:10

。我打开批处理文件,我希望它在%VIVADO_VER%失败,因为没有变量,它无法找到下的可执行文件C:\赛灵思\ Vivado \ 2016.4 \ ....我需要为vivado工具和SDK设置的所有环境变量是什么?我怀疑这是因为我们的IT部门阻止了下载管理器的正常安装,我们不得不进行特殊安装

2020-05-25 07:41:25

使用的更多信息,请参阅(UG901)Vivado设计工具用户指南:Synthesis(综合)。 分析日志文件中的信息图4是通过重定时提升逻辑水平的一个例子,该电路结构中有一个关键的路径分为三个逻辑层

2019-03-14 12:32:05

vivado自己设置的工程目录本身比较深,而文件路径太深会导致某些奇怪的错误。这是windows系统本身的特性决定的,windows的路径名不能超过260字节,所以大家设计的时候一定注意路径名长度

2019-09-11 11:52:42

ADVANCED ASIC CHIP SYNTHESIS文件大小:16MUNIX is a registered trademark of UNIX Systems Laboratories

2009-12-18 11:16:27

searth path 怎么设置呢?还有一个问题是include options和file searth path都有上下两个可以添加路径的窗口,这两个窗口有什么不同呢?谢谢大家的回答~~

2018-06-21 10:27:12

我自己做了一个小模块,来实现检测输入信号的上升沿的功能。VCS和vivado synthesis post timing仿真运行都符合预期,但是生成的bit文件下载到fpga则不对。fpga平台

2021-10-14 11:23:46

在UE中include都需要时绝对路径,有没有办法可以设置成相对路劲呢

2013-06-14 22:15:35

labview 中罗列文件夹控件的路径是怎么设置的?

2012-03-13 19:24:48

nWave(ctrl+w)中报signal路径错误,nTrace中显示信号路径是xx.xx.xx.signal1;而nWave中信号路径是xx/xx/xx/signal1.单独使用Verilog语言或者

2016-01-10 18:37:53

你好:我没有通过ZC702评估套件和Vivado 2013.2中的PMOD1上的SPI外设通过EMIO获得预期的行为。我已阅读AR#47511我必须在MHS文件中更改或添加一些代码行,但我在项目目录中找不到MHS文件。 Vivado不使用MHS文件吗?我怎么解决这个问题?

2019-11-08 12:12:06

为什么在verilog中添加与逻辑的其他部分无关的进程(带有always语句)会影响输出?我将该过程添加到verilog代码中,即该过程中的一个寄存器将根据状态机中的某些信号变高或变低,并且此过程中

2019-03-27 07:37:35

工程才可以。 但如果需要读取或写入工程本身的文件夹之外的txt文件中,就涉及到路径问题,在verilog中使用这个下面的系统任务命令 $readmemb("filename"

2016-06-21 13:52:59

1,创建工程打开Vivado软件,点击新建工程。根据向导创建工程,以下以Xilin 7020开发板为例,进行介绍。注意:I,设置工程的名称,在这个步骤中可以勾选“Create project

2023-04-05 23:21:24

enumdefine.sv为Verilog Header即可。同样,在Vivado中可以通过下面的方式设置宏定义:Add synthesis option "-verilog

2022-07-08 16:13:01

Header.

在config.v中增加宏定义: `define FPGA_SOURCE

将tb_top.v设置为顶层, 并添加如上图读入.verilog文件的路径,保存文件。

请问胡哥,上述步骤有出现错误或疏漏吗

2023-08-16 08:20:13

vivado中synthesis通过,implement通过,但是在编译simulation的时候报错:[USF-XSim-62] 'compile' step failed with error

2017-07-05 10:46:33

只想看模块D的波形,那么该fsdb波形,能够在仿真环境B中查看了吗?当然,在仿真环境B中,能够直接打开该fsdb波形,但是不能将模块D的代码和波形中模块D的波形进行对应,因为他们的层次路径不一样。所以

2022-04-02 17:30:33

吧xadc_prj.xpr文件放置到脚本中设置的路径下。 双击xadc_prj.xpr,Vivado工具将被打开,会自动以此创建新的工程,界面如图所示。 此时,工程文件夹里也自动创建了很多新的子文件夹

2016-10-19 18:05:13

郁闷了,表示只看过VHDL语法但没写过。暂且不说VHDL模块的内容,我应该如何在测试平台中例化它并对它进行测试呢?稍微查了一下,其实很简单,只要把VHDL中的组件名、端口统统拿出来,按照verilog

2018-07-03 12:58:49

郁闷了,表示只看过VHDL语法但没写过。暂且不说VHDL模块的内容,我应该如何在测试平台中例化它并对它进行测试呢?稍微查了一下,其实很简单,只要把VHDL中的组件名、端口统统拿出来,按照verilog

2018-07-09 01:14:18

在LABVIEW中,用Matlab Scrip怎么调用Matlab中.m的函数,怎么设置路径,我是这样设置路径的,一直识别不了,请问问题出哪儿?

2018-05-09 16:07:33

代码中的语法错误以及代码行为的正确性,其中不包括延时信息。如果没有实例化一些与器件相关的特殊底层元件的话,这个阶段的仿真也可以做到与器件无关。因此在设计的初期阶段不使用特殊底层元件即可以提高代码的可读性

2018-01-24 11:06:12

Tools> Vivado 2017.2>Vivado 2017.2;

2) 点击‘Create Project’,或者单击File>New Project

2023-08-17 19:31:54

2017.2>Vivado 2017.22)点击‘Create Project’,或者单击File>New Project创建工程文件3)将新的工程项目命名为‘lab3’,选择工程保存路径,勾选

2017-12-20 10:23:11

嗨朋友们,我正在尝试使用块内存生成器访问存储在ROM中的.coe文件。我想为此编写一个verilog代码。如何以verilog代码访问存储在BRAM中的像素值?提前致谢。以上来自于谷歌翻译以下为原文

2019-02-26 09:48:33

大家好,我试图在verilog文件中将命令传递给系统。 (在最初的开始循环中)我尝试使用$ system命令行。它现在处于verilog标准,但它似乎不适用于vivado。谁知道怎么做?这是我想要

2020-05-22 15:23:42

当我构建项目时,我得到了“include file”错误。我发现修复这些错误的唯一方法是指定包含文件的完整路径或相对路径。如何修改包含文件的搜索路径,从而不必编辑源代码“include”语句

2019-07-05 09:32:44

是5位模式。我决定编写一个代码来生成值,而不是在LCD上看到它我会创建一个文本文件并将结果写入该文件。任何人都可以告诉我如何在verilog中编写代码,这将允许我给出一个特定的频率,以便我可以绕过信号发生器的使用并在代码中输入各种频率值并获得不同的结果?谢谢

2019-10-29 09:40:37

的便捷性和实用性不用说,接下来我们就来盘点一下使用Notepad++在编写verilog代码时要配置哪些!第一 括号、双引号自动补全点击设置——首选项,如图所示在弹出的窗口中选择自动完成,将下面需要

2017-11-18 09:44:25

嗨,我认为这仍然可以作为xilinx问题(而不是synplify pro问题),因为我在xilinx ISE 14.5中使用synplify pro仅用于合成。所以这里......我在verilog

2019-03-12 09:08:41

您好,我正在为Vivado 2015.3课程做一个项目。该项目是边界扫描测试。我编写了所有VHDL代码并尝试实现。但是,实施还没有发生。我一直得到错误:[Synth 8-4169]使用条款中的错误

2019-04-15 12:38:48

大家早上好,我们尝试编写用于将FPGA的IO设置为JTAG模式的verilog代码。请仔细阅读下面附带的verilog,测试台代码。我们在模拟中没有得到正确的输出。 D_out正在成为高阻抗。任何人都可以帮我解决这个问题吗?问候Vimalasimulation.wcfg 6 KB

2020-03-23 09:04:29

综合,结果存储在.DCP文件中我做了第二个VIVADO综合后项目......我从第一个VIVADO项目添加了DCP文件,我也添加了NGC文件...但每当我运行实现我得到“顶部找不到文件。请添加一个顶级

2019-03-22 07:46:30

大家好,使用UCF文件中的ISE,我习惯于在输入焊盘和第一个触发器之间的信号上设置maxdelay约束,特别是在总线信号上,以确保总线的所有信号具有大致相同的传播时间。使用Vivado,我无法在

2018-10-25 15:17:18

重新打开ISE项目时,它失败了。有没有办法在ISE中设置Include目录?谢谢,保罗以上来自于谷歌翻译以下为原文Hi, I am running ISE 10.1.03 and am trying

2018-10-12 14:13:51

,希望能带着大家一步一个脚印,脚踏实地的在Vivado和Modelsim两个主流的工具中完成Verilog的设计和验证。FPGA或Verilog的视频教程有很多了,但是能下功夫“陪着”初学者一行一行敲代码

2020-04-22 09:20:48

(Filetype)为Verilog;文件名(File name)为sim_zstar;文件路径(File location)为默认的<Local to Project>。图设置新建

2019-09-20 12:02:36

谁能给个verilog中的.vt格式文件的建立路径,比如要建一个.v文件的路径是:quartus/new/Verilog hdl file;再比如要建一个时序文件,路径是:quartus/new

2016-05-17 21:59:24

通过编写的Verilog代码去实现(如果用数字电路的话,太复杂了);目前问题:不知道如何通过Cadence新建的Verilog file,实现生成.lib库文件(.olb符号库文件已经会生成了);其他

2018-06-02 09:44:22

我正在使用Eclipse,我想将MPLAB X IDE编译器与它结合起来。请帮忙。在Eclipse中需要设置哪些路径和哪些路径? 以上来自于百度翻译 以下为原文 I am using

2019-06-27 08:14:57

如何为NuMicro®M451系列中的PWM设置计数器同步?

2020-12-18 07:04:37

我发现vivado可以改变工具中的featuresaboutSynthesis - settings - Synthesis。但我在ISE中找不到类似的东西。如果有人知道设置在哪里。非常感谢你!

2019-08-12 10:13:33

`include "define_file.v" 是不行的,要使用绝对路径,如 `include "F:/110503_Test/rtl

2014-08-27 00:49:38

Verilog HDL Synthesis (A Practical Primer)

2009-02-12 09:36:24 40

40 ref-sdr-sdram-verilog代码

SDR SDRAM Controller v1.1 readme.txt

This readme file for the SDR SDRAM

2009-06-14 08:50:44 32

32 本文简单介绍在使用Verilog HDL语言时文件的调用问题之include使用方法介绍及举例说明,详见本文...

2013-01-24 14:40:42 6412

6412

verilog_代码资料,非常实用的代码示例。

2016-02-18 15:00:10 36

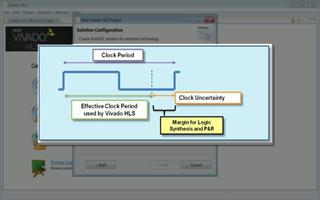

36 Xilinx公司讲述:Getting Started with Vivado High-Level Synthesis

2018-06-04 13:47:00 3416

3416

如何为您的NFV应用设置DPDK

2018-11-12 06:37:00 2738

2738 vivado创立的某个文件夹路径太长了,导致报错。这个是本身工程目录路径名很长导致的。这个错误在windows下才会有,因为windows本身就限制了路径长度,Linux下运行vivado不会这样。

2019-03-30 09:39:44 6263

6263 中国大学MOOC

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-08-06 06:12:00 3450

3450

有个小伙伴在我们的嵌入式交流群里发了类似下面的一张图, 顿时引起一阵骚动,我把源代码再附上, main.c 如下: #include 《stdio.h》 #include 《string.h

2021-05-03 11:52:00 802

802

一、Verilog 编码风格 (本文的语法高亮因为浏览器的缘故,所以不准确) 1.1 使用“`include编译器指令” 文件包含“`include编译器指令”用于在合成过程中将源文件的全部内容插入

2021-05-23 14:51:51 1600

1600 Vivado 的XDC设置输出延时 Vivado 的XDC设置输出延时,用于输出伴随时钟和数据的,数据是由系统时钟125M驱动,伴随时钟是由125M经过Pll相位移动-90度。 设置输出时钟

2021-06-09 17:28:01 3888

3888

符。 Vivado Synthesis Hangs/StopsVivado在综合时,如果显示一直在运转,但不再输出任何log信息时,检查一下工程路径是否包含了特殊字符“”。因为“”字符在Tcl脚本里是变量置换

2021-09-12 15:15:19 5055

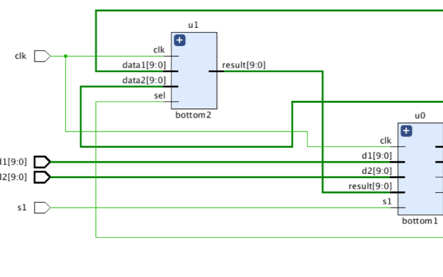

5055 在整个流程中,用户先创建一个设计 C、C++ 或 SystemC 源代码,以及一个C的测试平台。通过 Vivado HLS Synthesis 运行设计,生成 RTL 设计,代码可以是 Verilog,也可以是 VHDL。

2022-06-02 09:48:17 6129

6129 中的file_path就是获取的文件所在路径。 代码如下: import os file=self.openfile= QFileDialog.getOpenFileNames() file

2022-06-20 21:05:14 2994

2994 Vivado IPI (IP Integrator)提供了直观的模块化的设计方法。用户可以将Vivado IP Catalog中的IP、用户自己的RTL代码、或者用户已有的BD文件添加到IP Integrator中构成Block Design,设计更复杂的系统,如下图所示。

2022-07-15 11:39:12 1335

1335 全局综合(Global Synthesis)全局综合意味着整个设计在一个Synthesis Design Run流程中完成,这样会带来几个好处。

2022-07-15 11:39:42 1468

1468 写代码是给别人和多年后的自己看的。 关于Verilog代码设计的一些风格和方法之前也写过一些Verilog有什么奇技淫巧?

2022-10-24 15:23:54 1011

1011 当使用Codeviser调试系统映像文件时,经常遇到映像编译使用的源代码路径和调试时使用的源代码路径不一致的情况,调试这样的映像时,经常会发生找不到源代码的情况,这时就需要设置映像对应的源代码路径,以便映像引用的是正确的源代码。

2022-11-15 11:07:36 850

850 本文主要介绍Vivado布线参数设置,基本设置方式和vivado综合参数设置基本一致,将详细说明如何设置布线参数以优化FPGA设计的性能,以及如何设置Vivado压缩BIT文件。

2023-05-16 16:40:45 2957

2957

本文主要介绍ROM和RAM实现的verilog代码版本,可以借鉴参考下。

2023-05-16 16:57:42 799

799 什么是Logic Synthesis?Logic Synthesis用于将输入的高级语言描述(如HDL、verilog)转换为门级电路的网络表示。

2023-10-24 15:56:04 484

484

电子发烧友App

电子发烧友App

评论