在这篇实例之前,说点自己的两点感受。

一、这个zynq开发流程基本上是这样一个节奏:PlanAhead为软硬件结合的载体,在此可以设计硬件,然后将硬件导出到软件设计。基本流程如图:

这里三个软件切换来切换去,极其麻烦,并且其中还可能要FPGA开发用到的ISE,应该不是xilinx想要的结果,预计以后会集成到一个软件上。

二、刚使用这个平台不久,碰到bug不少,说明xilinx推出时准备不是很充分。

用户IPcore与PS交互数据分两种方案:一种是通过EMIO交换数据,将PL的IP核当做系统外设,性能有所欠缺。

常用的是第二种:满足AXI协议的IP核。此IPcore与AXI密切相关,难度较高。为降低难度,xilinx提供wizard自动生成axi总线相关代码,做好地址译码逻辑、读写控制逻辑,并在工作区生成一些寄存器。用户PL逻辑通过读写这些寄存器与PS交互。

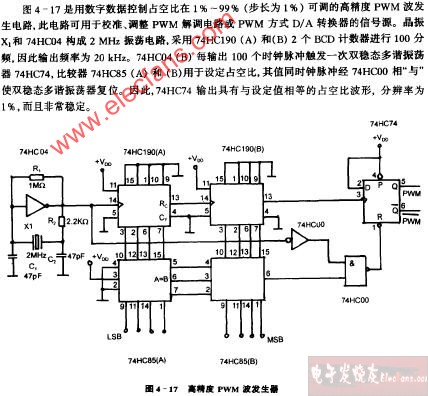

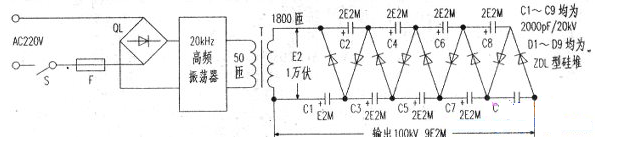

以PWM发生器为例,有两个寄存器,一个调节周期的寄存器,一个调节占空比。PlanAhead建立工程,添加嵌入式资源进入XPS,添加xml配置之后,进入XPS Hardware —> Create or Import Periphera。开始添加IPcore wizard过程,注意在 IP interface阶段,user logic master support表示ip核内部是否要加入master接口,一般用在较复杂外设。software reset和include data phase timer分别为是否开启软件中断和数据周期计时器,在此我们不要这些,防止生成多余的AXImaster接口、复位和计时模块。下一步选择寄存器数量,这里我们用到占空比和周期reg,因此设为2。下一步仿真平台不要,下一步勾选二三项,第一项是生成verilogVHDL,我要VHDL,不选,二表示生成一个ISE工程便于测试和调试IP core。三表示生成软件驱动库文件,方便在SDK中使用IP core。完成wizard。

配置完成,接下来添加刚完成的IPcore,在IP catalog中双击添加,不用修改ok即可在 bus interface可找到刚添加的pwm_ip_0,右键之,view MPD,添加pwm_out接口,1bit的输出PORT pwm_ou = "", DIR =o这里添加的代码在systemassembly view中的port映射出添加的pwm_out,

问题:在wizard完成后出现pwm_ip.vhd文件没有user_logic的component块。原因:勾选Generate stub ‘user_logic’template in verilog instead of VHDL之后会生成。

右键pwm_ip_0,选择browser HDL sources 选pwm_ip.hdl在component加用户逻辑user_logic,继续右键pwm_ip_0,选择browser HDL sources 选user_logic.v添加自己要加的功能,这里我们加pwm发生功能,代码如下

wire ovprd;//下一个周期开始信号

reg [C_SLV_DEIDTH-1 : 0] pwm_counter;

wire pre_pwm_out;//预输出信号

always @(posedge Bus2IP_Clk) begin

if(!Bus2IP_Clk || ovprd || ~slv_reg1[31])//时钟0,下一个周期开始1,占空比reg31位0 计数器复位

pwm_counter = 32'h8000_0000;

else if(slv_reg1[31])

pwm_counter = pwm_counter + 1'b1;

else

pwm_counter = pwm_counter;

end

assign ovprd = (pwm_counter[30 : 0] == slv_reg0[30 : 0])? 1'b1 : 1'b0;

assign pre_pwm_out = (slv_reg1 < pwm_counter)? 1'b0 : 1'b 1;

assign pwm_out = pre_pwm_out & slv_reg1[31];

然后project—>Rescan User Repositories更新,可以在ports中看到新添加的引脚,选择exteral ports连接管脚。

在Address中右上角Generated Address自动分配地址

Project—> Design Rule Check 没有错误后关闭XPS回到PA

右键module_1,create top HDL

add source 选择添加约束,对应之前的工程名

run synthesis,出现错误,如下图1

重新建程序,更改新建xps工程名以及PA的约束名为system,而不使用module_1默认名,另外一个改动是wizard建立ipcore过程中去掉data phase timer模块。之后错误消失,但是警告如图2,这个警告是由于约束地址造成,关系不大。

下一步打开open synthesized design(不点开这个在PA界面找不到IO ports标签)打开IO ports,设置pwm_out的引脚,然后保存(点击PA的保存标签会让你选择一个ucf文件来保存,不需要自己另外写)。

Generate Bitstream 然后导出硬件到SDK,新建xilinx cproject,选择hello world模板。

注意接下来是将自己的pwm_ip导入的过程,跟上一个实验不一样的地方。选择xilinx tools —> Repositories 点击new 找到工程路径到edk,ok。右击hello_world_bsp_0,选择Board Support Package Setting,找到drivers中的pwm_ip_0,将drive栏目下的generic修改为pwm_ip,自此自设的IP核驱动就已经添加进来了。这里会报错,这是xilinx的一个bug,在hello_world_bsp_0上有一个红叉,在pwm_ip_selftest.c中加入#definePWM_IP_USER_NUM_REG_2,添加之后还是报错,如图3

注释掉

添加C代码

PWM_IP_mWriteReg(XPAR_PWM_IP_0_BASEADDR,0, 10000);

PWM_IP_mWriteReg(XPAR_PWM_IP_0_BASEADDR, 4,0X80000000+5000);//5000/10000=50%

保存报错'XPAR_PWM_IP_0_BASEADDR'undeclared (first use in this function)

修改后报错cannot find -lxil(可能是project_1没有改为对应pwm_ip_test,导致库文件宏定义之类的不能调用)

发现PWM_IP_USER_NUM_REG 2多写了个下划线的错误。修改后错误依旧,貌似不会重新编译。因此要重新从PA导出硬件到SDK。

选择Xilinx Tools->Program FPGA

在hello_world_0工程上右击,选择RunAs->Launch on Hardware运行出现各种错误,如下图4、5

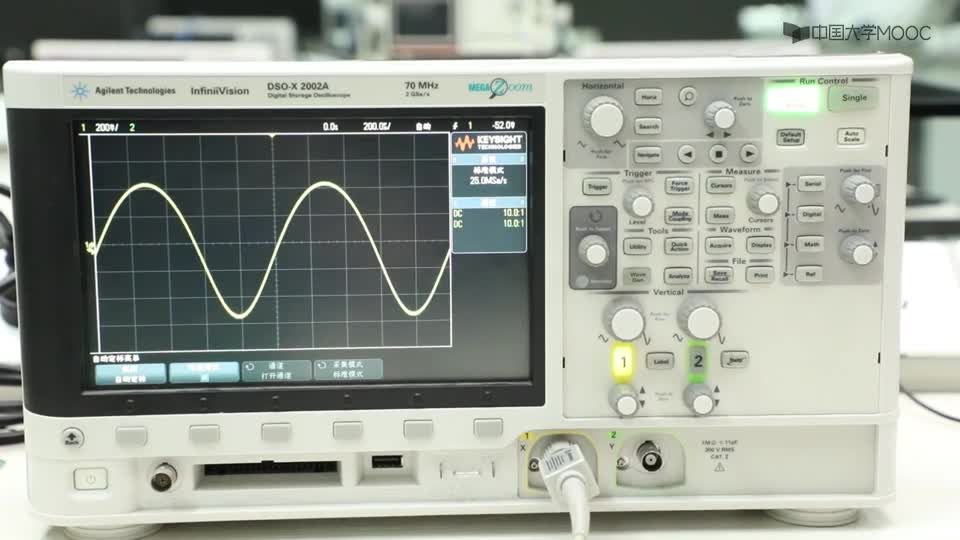

换成memorytest模板后,万用表查看JA1约为1.2V。用示波器看波形结果是正确的。helloworld模板不行,具体原因不明。

总结:

第一、添加user_logic.v时要求为verilog代码,在wizard过程中尝试过使用VHDL而不是verilog,结果是生成的pwm_ip.hdl中没有user_logic的component模块。而pwm_ip.hdl又是VHDL语言,极其不便。

第二、添加约束时使用默认的module_1文件名,综合时会出错,改名为system则通过。

第三、在SDK中添加#define PWM_IP_USER_NUM_REG 2后不会自动编译进去,需要重新新建 Xilinx CProject才能正常使用。

第四、使用hello world模板会出现不明问题导致RunAs->Launch onHardware出错,改为memorytest模板正常。

电子发烧友App

电子发烧友App

评论