在数字电路中,出于应用的需要,我们可以使用无符号数,即包括0及整数的集合;也可以使用有符号数,即包括0和正负数的集合。在更加复杂的系统中,也许这两种类型的数,我们都会用到。 有符号数通常以2的补码

2020-11-18 17:46:10 16178

16178 不知道有没有人像我一样,长久以来将verilog中的有符号数视为不敢触碰的禁区。

2023-12-04 16:13:21 259

259

无符号整型数据,将这两数相乘后强制转换为无符号字符型数据。并通过P0口将运算结果显示出来在keil c51中创建新工程ex8,编写如下程序代码,编译并生成ex8.hex文件。//实例87:利用P0

2012-03-22 10:43:43

:01010010这样计算更为简便符号描述运算规则&:与两个位都为1时,结果才为1| :或两个位都为0时,结果才为0^:异或两个位相同为0,相异为1~:取反0变1,1变0>> :右移各二进位全部右移若干位,对无符号数,高位补0,有符号数,各编译器处理方

2021-12-24 07:44:47

想法是,定义一个32位无符号整形,然后把它用二进制的形式显示出来。如图所示。 但是,最高8位一旦超过0x7f,就不正常了。这不是有符号整形才有的特点吗? 无符号整形不应该呀。求好心人指点下。

2015-09-17 22:06:35

一.如果对一个32位无符号数开方,那么结果一定是一个16位无符号数。现设被开方的数为a,开方结果:b = b[15] * 2^15 + b[14] * 2^14 + ... + b[0] * 2^0

2009-09-21 09:12:45

转换器的数据总线的逻辑构件。一、实验目的1、了解算术逻辑运算器(74LS181)的组成和功能。2、掌握基本算术和逻辑运算的实现方法。二、实验内容运用算术逻辑运算器 74LS181 进行有符号数/无符号数的算术运算和逻辑运算。三、实验元器件1、算术逻辑运算器(74LS181)。2、三态门(74LS24

2022-01-25 08:11:31

hi,everyone:

我做优化时候,需要将一个有符号的32位 int 类型的数,做一个饱和操作,变成一个

无符号的8位的数。具体代码如下:

int var;

if(var>255

2018-06-21 02:36:07

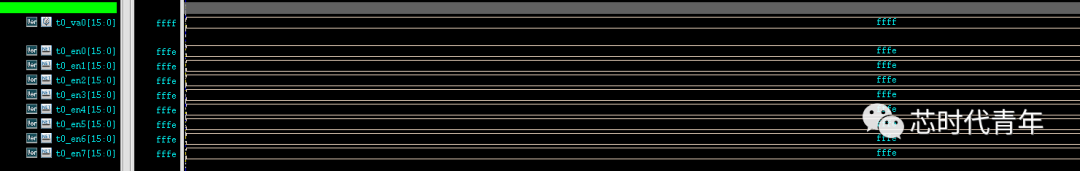

。 VerilogHDL中默认数据类型为无符号数,因此需要数学运算的场合必须要用“signed”声明,如:reg signed [8-1:0] signal_a; wire signed [32-1:0

2018-08-13 09:27:32

;>>;有符号数算术移位和逻辑移位,两者左移时一样,右移时逻辑移位最高位填充的是0,算术移位最高位填充的是符号位。`

2012-02-23 16:45:35

LabVIEW对8-bit图像进行滤波或算术运算8-bit(U8)无符号整数图像并不包含负数,这样的话如果对其进行的操作,例如IMAQ Convolute,IMAQ Subtract等等,结果出现

2022-06-16 20:58:21

Matlab符号数学工具箱应用说明Matlab符号运算是通过集成在Matlab中的符号数学工具箱(Symbolic Math Toolbox)来实现的。和别的工具箱有所不同,该工具箱不是基于矩阵

2009-09-22 15:28:46

在Bits的基础上,SpinalHDL提供了UInt、SInt数据类型,从而能够进行有符号/无符号数操作。变量定义/初始化UInt/SInt的初始化与Bits类型相似:逻辑操作符UInt/SInt

2022-07-14 14:45:15

Verilog HDL应用实例

2017-09-19 23:03:44

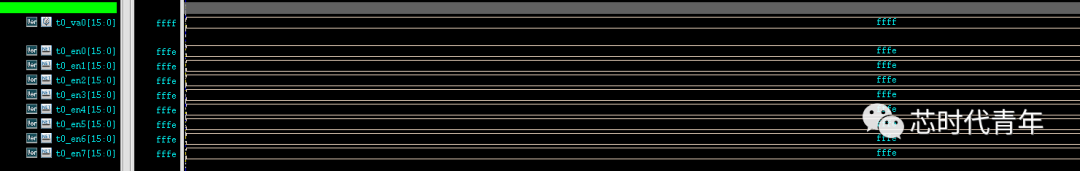

在代码里面d和cnt都是无符号数,但是在编写测试文件仿真的时候,modelsim中变成了有符号数,cnt计数到1023后也会变成负的,这是什么原因呢

2021-01-11 15:45:36

…………………………………………………………………………………………… 51、 无符号数一位乘法 …………………………………………………………………………… 72、 符号数一位乘法 ……………………………………………………………………………… 83、 布思算法(Booth

2012-08-12 11:59:01

stm32无符号8位转换为int类型的方法是什么

2021-12-20 07:14:30

xilinx dds IP核输出能不能改为无符号数,因为一般DA转化器只能转化正数

2015-09-29 18:30:23

常量90.00006 // 实数型常量"BOND" // 串常量;每个字符作为 8 位 ASCII 值存储表达式中的整数值可被解释为有符号数或无符号数。参数类似于常量,并且使用参数

2018-09-20 09:23:23

的C51定点运算库,在乘除相关指令方面,没能充分运用中颖SH79/88/89/F51系列自带的 16位X8位硬件乘法器 和 16位/8位硬件除法器,网上搜了一下,中颖SH79/88/89/F51系列有个

2011-11-22 19:26:19

为什么MCU中的除法运算要比乘法运算的效率低

2023-10-09 07:45:11

乘除法运算本应用例的目的在于提供乘、除运算的函数及介绍乘除运算在SPMC75F2413A中的使用。应用例提供有符号和无符号数的乘除,其中包括32-Bit/16-Bit、16-Bit/8

2009-09-21 09:26:57

(1)加法带符号数进行加法运算时,加数与被加数均用补码形式表示,其结果仍为补码,只要结果不超过规定的数表示的范围,也就是只要不发生溢出,则结果总是正确的。而当发生溢出时,使符号位遭到破坏,则结果出错

2019-12-11 17:58:19

,存储无符号数)Tab = -4'd12;//整数Tab的十进制数为-12,位形式为110100.(因为Tab是整数寄存器变量,存储有符号数)我的困惑是,-12的二进制补码应该是10100,为什么这里写成110100了?前面为啥多个1??求大神指教~谢谢!

2013-11-02 14:13:19

小弟我最近被一个问题纠结好久,就是有符号,无符号数,原码补码之间的运算,比如举个例吧,-6和7,我去算它们之间的加法和乘法。假设输入数据用8位2进制表示。首先,-6的原码是10000110,补码

2021-06-24 10:00:57

我有一个纯粹的原理图设计。当我尝试获取它的HDL实例化模板时,我得到这些错误:错误:找不到符号“mult32”错误:找不到符号“sub32”错误:找不到符号“sqrt”错误:找不到符号

2019-10-30 08:59:06

原码、补码、反码、有符号数、无符号数概念.pdf

2012-11-15 08:44:54

双状态无符号数据类型双状态有符号数据类型四状态数据类型

2021-01-18 06:03:15

问题:(1)从外部扩展RAM中读取被乘数和乘数,乘数存放于0100H处开始,总共3个乘数,每个乘数是3字节的有符号数。被乘数存放于0200H处开始,总共3个被乘数,每个被乘数是3字节的有符号数。(2

2021-12-01 07:27:23

跪求各位大神有没有基于verilog HDL的高速对数运算模块设计的CORD IC算法实现自然对数运算的代码

2016-03-10 12:39:28

我刚来这地方。对于Verilog中的FPGA乘法,在进行多重校对之前,是否需要扩展有符号数的符号位?或者,有一个库可以自动处理这部分,就像我们如何使用VHDL进行乘法一样?

2019-11-05 09:47:09

如何去实现单片机开发中无符号数的左移和右移运算呢?对于左移和右移的操作分别是如何呢?

2022-02-25 06:42:54

HelloIm试图编写代码来计算16位无符号整数乘法的16位的机器周期,IM使用PIC16F87 4 MHz振荡器。我知道在4 MHz时,1个机器周期需要1U。但是我不知道如何用16位无符号整数乘法

2019-03-27 06:47:34

LCD(16BPP)的ASCII(8x16)字库数组为什么定义成16位无符号而不是8位,图片资源文件为什么定义成8位:const uint16 ascii[4096] ={ };const uint8 gImage[614400] ={ };

2015-05-02 21:01:32

大家好,我在Virtex5上实现MAC(乘法和累加)单元。乘法器输入8位被乘数和9位有符号乘法器。我的问题是实施的可行性是什么; DSP Slice或Fabric逻辑片? Y'

2020-03-27 10:33:23

为什么很多嵌入式算法 都将浮点数转化为无符号整形,再进行运算,有些DSP自带浮点运算库的,但还是这样转换,本人初到,接触了一部分历程,有TI提供的,有大牛自己写的,感觉对IQmath不熟悉,但知道

2017-04-26 20:07:55

嗨,可能是个愚蠢的问题。我有两个像这样的无符号变量(XC32):当在两个变量之间求差时,我得到一个有符号的结果(即,在某个点上可能有负值)。为了纠正这个问题,我得到了结果的绝对值。我的问题是:我能配置XC吗?32,使得两个无符号变量的差值也是无符号的,从而避免了用户的绝对设计错误。欢迎任何评论。

2020-03-24 07:50:43

本帖最后由 hq1987 于 2015-4-29 11:52 编辑

对于无符号数大家都基本理解,我主要说说有符号数,浮点数在机器世界里到底是怎么表示的。1、有符号数机器表示以16位有符号数为例

2015-04-29 10:15:32

两个四位十进制数(BCD码表示)的乘法运算

2013-04-04 13:34:59

求无符号数的平均数文章目录题目重述问题分析以及求解思路程序代码题目重述试求内部RAM30H~37H单元中8个无符号数的算术平均值,结果存入38H。问题分析以及求解思路待完善(请耐心等待)程序代码

2021-12-01 08:01:16

求EDA四位乘法器实现0~9的平方运算

2017-06-12 10:58:53

1、实验内容一 1.1、问题一: 设ROM中的表格TAB中存储有8个无符号数(小于等于10),求这8个无符号数的算术平均值(结果只保留整数位),结果存入内部RAM30H中(先将TAB中存入8个常数

2021-07-14 08:08:08

基于FPGA的64位流水线加法器的设计基本要求: FPGA 可自行选择可实现64位无符号数的加法运算8级流水线深度

2014-12-18 11:00:42

1. 移位运算符移位运算符是双目运算符,将运算符左边的操作数左移或右移运算符右边的操作数指定的位数,用0来补充空闲位。如果右边操作数的值为X或Z,则移位结果为未知数X。Verilog HDL中有两种

2015-04-30 09:43:36

用Rom比较两个4bit无符号数,怎么实现?ROM宽度和深度怎么计算?

2015-09-24 14:33:07

请问AFE5801 AD转换后数字信号是用有符号数还是无符号数表示的啊?

2019-05-24 08:04:13

小弟最近在用STM32F030C6T6芯片完成电机的SVPWM控制。现在发现算法中,运行速度很慢。打算将所有的除法运算改成移位运算。一般的,无符号数的右移几位和除以2的几次幂是等效的。但是,在STM32里面,有符号数的右移也和除法运算等效吗?

2019-01-22 08:14:26

嗨,如何在Vivado项目中实例化hdl系统生成器输出的多个实例?在vivado项目中很容易实例化一个hdl系统生成器输出。当我想将另一个实例实例化到同一个项目时,我在合成状态下面临一些错误。最好的祝福

2020-07-31 10:38:59

和signed在一种类型下,unsigned表示在这个范围大小的整数,signed一般都是在这个范围内的从负到正,即其最高位为符号位。unsigned( 无符号整数 ):无符号整数 (unsig...

2021-07-02 07:59:47

1. 计算机中的符号位l 数据类型的最高位用于标识数据的符号A. 最高位为1,表面这个数为负数B. 最高位位0,表面这个数为正数2. 有符号表示法l 在计算机内部用补码表示有符号数A. 正数的补码为

2017-05-16 21:43:16

的时候怎么都不正确,具体原因如下,字符串转数值的时候只发现可以转换成无符号数,而采集下来的数据是有符号数,转换成无符号数之后就无法正确显示波形了。请教采集卡采集下来的有符号字符串类型的数据如何正确

2012-05-02 11:55:08

6.1 无符号数和有符号数6.2 数的定点表示和浮点表示6.3 定点运算6.4 浮点四则运算6.5 算术逻辑单元

2009-04-11 09:33:33 0

0 Verilog hdl教程实例

【例 3.2】4 位计数器module count4(out,reset,clk);output[3:0] out;input reset,clk;reg

2010-02-09 09:41:01 54

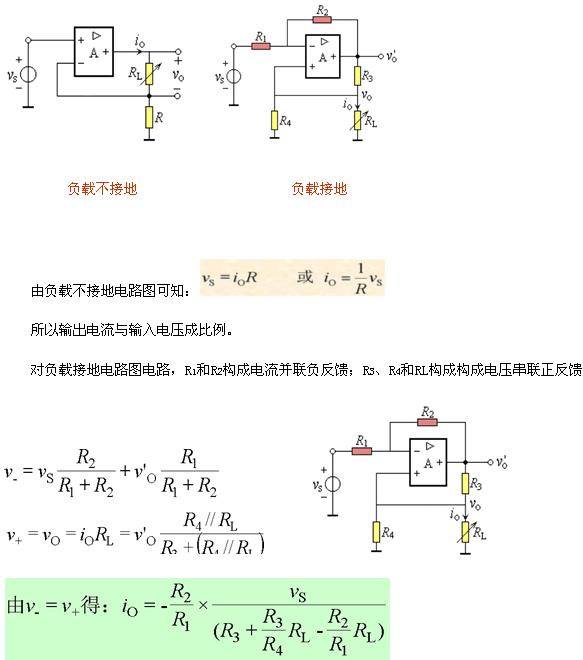

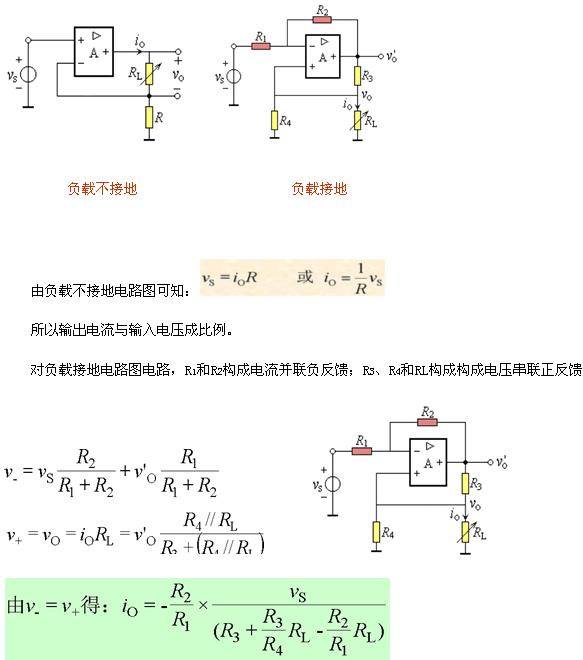

54 模拟乘法器在运算电路中的应用

8.6.1 乘法运算电路

8.6.2 除法运算电路

8.6.3 开方运算电路

2010-09-25 16:28:45 145

145 乘除运算电路

基本乘除运算电路,乘法电路

乘法器符号

2008-01-17 12:54:12 2705

2705

单字节无符号数据块排序(增序)

入口条件:数据块的首址在R0中,字节数在R7中。出口信息:完成排序(增序)影响资源

2009-01-19 22:58:25 1005

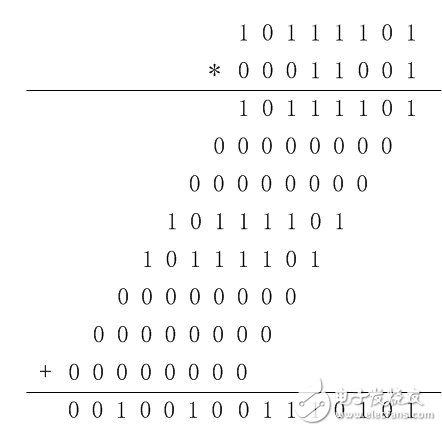

1005 原码一位乘法的实现算法(一) 用原码实现乘法运算是十分方便的。原码表示的两个数相乘,其乘积的符号为相乘两数符号的异或值,数值则为两数绝对值之积。假

2009-10-13 22:53:26 10820

10820

原码乘法,原码乘法原理详解

1.人工算法与机器算法的同异性 在定点计算机中,两个原码表示的数相乘的运算规则是:乘积的符号位由两数的

2010-04-13 10:55:30 31588

31588 补码乘法,补码乘法计算详细解说 1.补码与真值得转换公式 补码乘法因符号位参与运算,可以完成补码数的“直接”乘法,而不需要求补级

2010-04-13 11:05:06 35427

35427 电路简单的PWM乘法运算电路

电路的功能

脉冲宽度调制的乘法运算器

2010-05-08 14:23:16 3167

3167

乘法器在模拟运算电路中的应用

相乘运算

2010-05-18 16:48:06 1879

1879 本内容介绍了应用Verilog HDL进行数字系统设计实例

2011-09-27 16:30:29 87

87 该ALU采取层次化设计方法,由控制模块、逻辑模块、加减法模块、乘法模块和除法模块组成,能实现32位有符号数和无符号数的加减乘除运算,另外还能实现9种逻辑运算、6种移位运算以

2012-02-09 15:24:55 80

80 该程序实现功能:16位无符号数的乘法运算

2012-05-16 11:02:00 3198

3198 Verilog HDL应用程序设计实例精讲。

2016-05-20 11:16:35 90

90 Verilog HDL应用程序设计实例精讲

2016-05-20 11:16:35 284

284 MSP430硬件乘法器是一种外围设备,并不构成MSP430 CPU的一部分。它允许进行签名和无符号数的乘法运算。还支持乘法和累加(MAC)操作,这对于实现诸如有限脉冲响应(FIR)滤波器的数字信号处理(DSP)任务是有用的。

2018-05-07 09:38:18 8

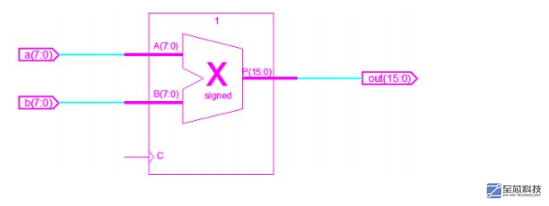

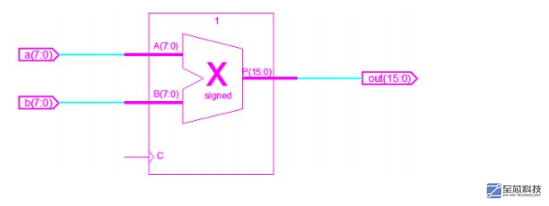

8 在设计中,所有的算数运算符都是按照无符号数进行的。如果要完成有符号数计算,对于加、减操作通过补码处理即可用无符号加法完成。对于乘法操作,无符号数直接采用“*”运算符,有符号数运算可通过定义输出

2018-10-09 15:22:29 5658

5658

Matlab 符号运算是通过符号数学工具箱(Symbolic Math Toolbox)来实现的。Matlab 符号数学工具箱是建立在功能强大的 Maple 软件的基础上的,当 Matlab 进行符号运算时,它就请求 Maple 软件去计算并将结果返回给 Matlab。

2018-10-31 08:00:00 0

0 Matlab 符号运算是通过符号数学工具箱(Symbolic Math Toolbox)来实现的。Matlab 符号数学工具箱是建立在功能强大的 Maple 软件的基础上的,当 Matlab 进行符号运算时,它就请求 Maple 软件去计算并将结果返回给 Matlab。

2019-07-24 16:03:26 33

33 输入系统的有正有负的模拟信号在AD采样前,会加上了直流偏置变成全正信号才输入AD的,所以在AD采样后送给FPGA的信号是无符号数。

2019-08-11 11:43:39 2821

2821 理解:对于两个有符号数X,Y,不外乎有四种情况,即(正,负),(负,正),(正,正),(负,负)。所有程序里就这四种情况进行讨论就行了。

2019-10-17 15:59:35 7502

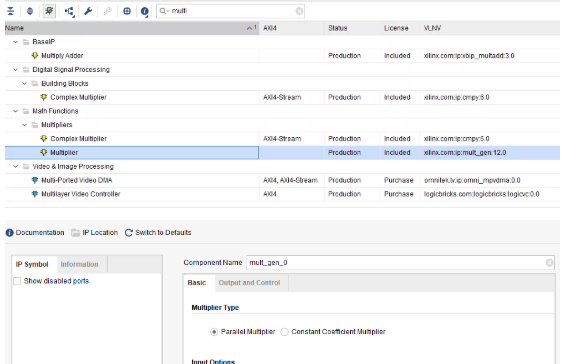

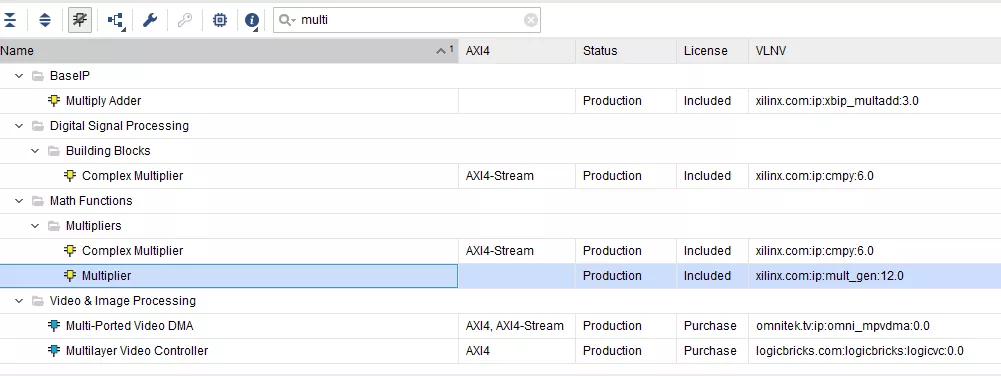

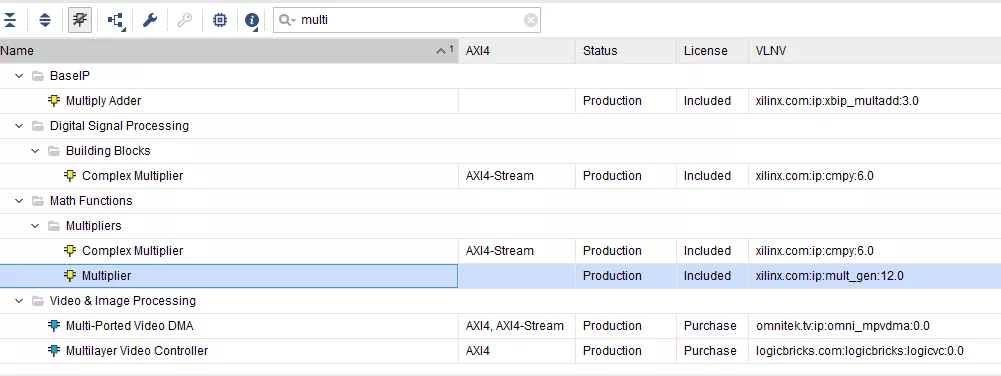

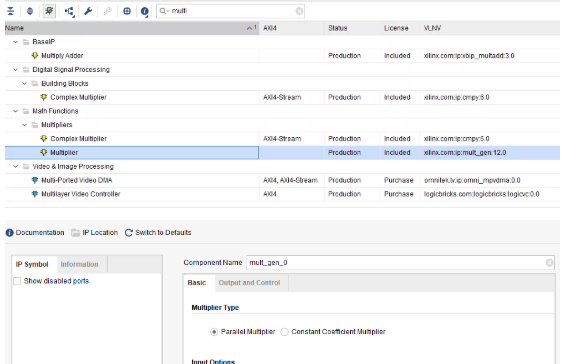

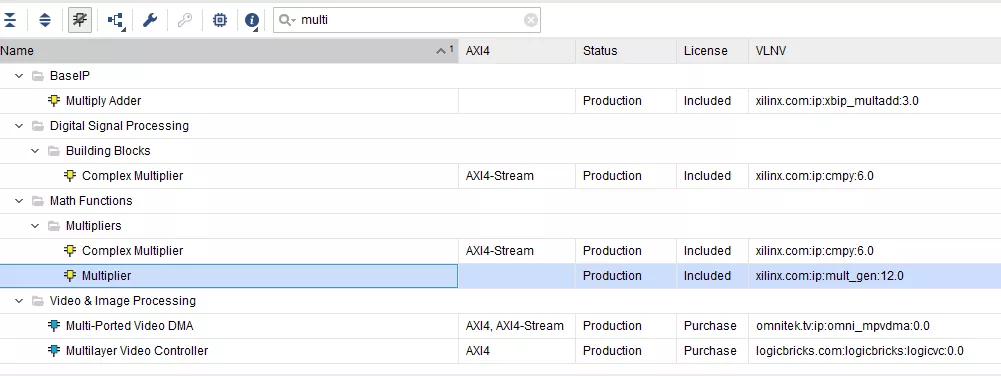

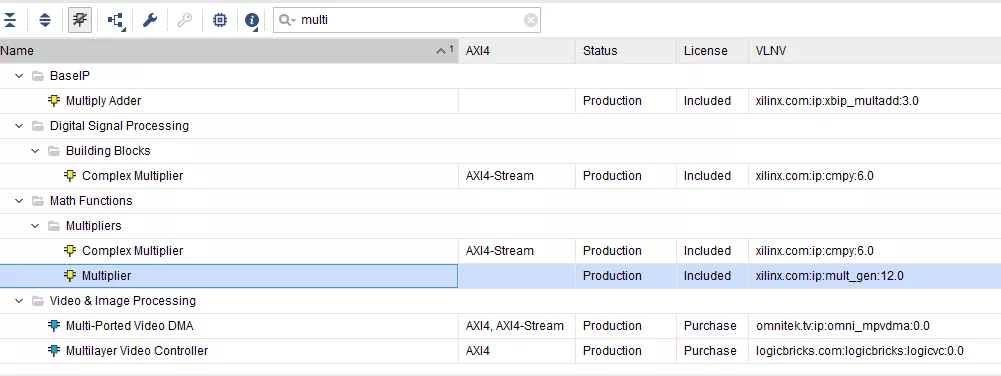

7502 FPGA中乘法器是很稀缺的资源,但也是我们做算法必不可少的资源。7系列及之前的FPGA都是25x18的DSP,UltraScale中是27x18,我们可以通过调IP Core的方式或者原语的方式来进行乘法操作。在里面可以设置有符号还是无符号数乘法。

2020-03-08 17:14:00 6251

6251

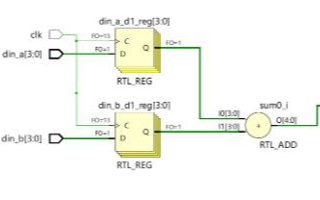

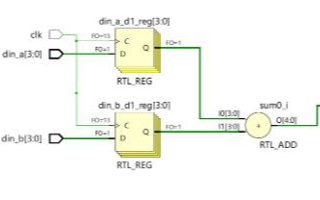

采用HDL代码描述加法运算只需要用操作符+即可,这看似很简单,这里我们以两个4-bit数相加为例,对输入/输出数据均寄存,从而形成如下图所示电路。 此电路对应的HDL代码如下图所示。这里采用

2020-09-24 14:31:15 1996

1996

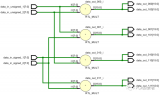

原语的方式来进行乘法操作。在里面可以设置有符号还是无符号数乘法。 当然,我们也可以直接使用*符合来进行乘法,对于无符号的乘法 reg [7:0] ubyte_a;reg [7:0] ubyte_b

2020-09-27 15:12:52 8952

8952

有符号数的计算在 Verilog 中是一个很重要的问题(也很容易会被忽视),在使用 Verilog 语言编写 FIR 滤波器时,需要涉及到有符号数的加法和乘法,在之前的程序中我把所有的输入输出和中间信号都定义成有符号数,这样在计算时没有出现问题,下面实际试验一下 Verilog 的乘法问题;

2021-05-02 10:48:00 6035

6035

基于空间相关性分析的符号数据分类

2021-06-09 14:41:15 8

8 问题:(1)从外部扩展RAM中读取被乘数和乘数,乘数存放于0100H处开始,总共3个乘数,每个乘数是3字节的有符号数。被乘数存放于0200H处开始,总共3个被乘数,每个被乘数是3字节的有符号数

2021-11-23 10:21:09 25

25 在单片机开发中,通常会使用左移和右移操作做快速的乘法和除法运算。例如,将0x0001左移1位,相当于乘以2^1左移2位相当于乘以2^2,以此类推,左移n位,相当于乘以2^n。右移则相当于除以

2022-01-13 13:17:21 2

2 FPGA中乘法器是很稀缺的资源,但也是我们做算法必不可少的资源。7系列及之前的FPGA都是25x18的DSP,UltraScale中是27x18,我们可以通过调IP Core的方式或者原语的方式来进行乘法操作。在里面可以设置有符号还是无符号数乘法。

2022-02-16 16:21:36 4197

4197

给定四个无符号数,请找出最小值。无符号数可以与标准比较运算符(a < b)进行比较。使用条件运算符描述一个两路的最小值电路,然后组合它来创建一个4路最小电路。可能需要一些线向量作为中间结果。

2022-09-28 17:07:03 929

929 我们学习一下Systemverilog中的有符号数据类型的赋值。

2022-10-17 14:40:26 694

694 为了省流,还是先甩结论。有符号数和无符号数的最本质区别就是:符号位的识别和高位拓展。除此之外,另一个区别就是从人的角度如何如何读这个数,或者说$display(%d)打印时打印的值是什么(而从机器的角度它压根就不区分signed和unsigned)。

2023-12-10 10:50:46 380

380

电子发烧友App

电子发烧友App

评论