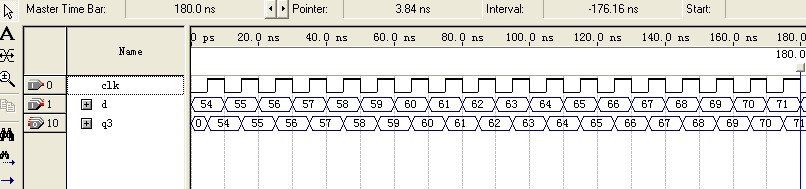

原文链接:学verilog 一个月了,在开发板上面写了很多代码,但是始终对一些问题理解的不够透彻,这里我们来写几个例子仿真出阻塞和非阻塞的区别,我们先上代码module LED ( CLK, RSTn, scan, flag , c, ,one,two,three,four); input CLK; input RSTn; input scan; output flag,c; output [3:0] one,two,three,four;/***********************************************************/ reg F1,F2; reg a,b; reg [3:0] one,two,three,four; /********************信号传递之间的非阻塞赋值***************************************/ always @ ( posedge CLK or negedge RSTn ) // if( !RSTn ) begin F1 <= 1'b1; F2 <= 1'b1; end else begin F1 <= scan; F2 <= F1; end /*******************信号传递之间的阻塞赋值****************************************/ always @ ( posedge CLK or negedge RSTn ) // if( !RSTn ) begin a = 1'b1; b = 1'b1; end else begin a = scan; b = a; end /******************数据加 非阻塞赋值 先判断后计数*****************************************/ always @ ( posedge CLK or negedge RSTn ) //one <= if( !RSTn ) begin one<=0; end else begin if(one==14) one<=0; else one<=one+1; end/***************数据加 非阻塞赋值 先计数后判断********************************************/ always @ ( posedge CLK or negedge RSTn ) // two<= if( !RSTn ) begin two<=0; end else begin two<=two+1; if(two==14) two<=0; end /**************数据加 阻塞赋值 先判断后计数*********************************************/ always @ ( posedge CLK or negedge RSTn ) //three = if( !RSTn ) begin three=0; end else begin if(three==14) three=0; else three=three+1; end/*************数据加 阻塞赋值 先计数后判断**********************************************/ always @ ( posedge CLK or negedge RSTn ) //four = if( !RSTn ) begin four=0; end else begin four=four+1; if(four==14) four=0; end /****************信号之间传递***********************/ assign flag = F2 & !F1;assign c = b & !a;/***************************************/ endmodule 2、我使用modesim 仿真,下面为我的 test bench `timescale 1 ps/ 1 psmodule LED_vlg_tst();// constants // general purpose registersreg eachvec;// test vector input registersreg CLK;reg RSTn;reg scan;// wires wire c;wire flag;wire [3:0] four;wire [3:0] one;wire [3:0] three;wire [3:0] two;// assign statements (if any) LED i1 (// port map - connection between master ports and signals/registers .CLK(CLK), .RSTn(RSTn), .c(c), .flag(flag), .four(four), .one(one), .scan(scan), .three(three), .two(two));/*initial begin // code that executes only once // insert code here --> begin // --> end $display("Running testbench"); end always // optional sensitivity list // @(event1 or event2 or .... eventn) begin // code executes for every event on sensitivity list // insert code here --> begin @eachvec; // --> end end endmodule*/initial beginCLK = 0;forever#10 CLK = ~CLK; endinitial beginscan = 0;forever#100 scan = ~scan; endinitial beginRSTn = 0;#1000 RSTn = 1;#1000;#1000;#1000;#1000;#1000;#1000;#1000;#1000;$stop;endendmodule 主要就是初始化一个CLK 和scan的信号,然后就是初始化一下复位,最后就是设置仿真时间,这样modesim 就不会一直处于仿真状态,消耗资源,也可以方便仿真。 其中quartus 与modesim 互相调用调试,可以关注我的博客,这里我就不具体讲解了! 3、modesim 波形图 大家注意到红线框内的数据变化,就能很清楚的理解 阻塞与非阻塞了! 微观分析 阻塞与非阻塞1、上代码,具体观察,a,b,c与F1,F2,flage 的变化 module LED ( CLK, RSTn, scan, flag , a,b,c,F1,F2,); input CLK; input RSTn; input scan; output flag,a,b,c; output F1,F2;/***********************************************************/ reg F1,F2; reg a,b; /***********************************************************/ always @ ( posedge CLK or negedge RSTn ) // if( !RSTn ) begin F1 <= 1'b1; F2 <= 1'b1; end else begin F1 <= scan; F2 <= F1; end /***********************************************************/ always @ ( posedge CLK or negedge RSTn ) // if( !RSTn ) begin a = 1'b1; b = 1'b1; end else begin a = scan; b = a; end /***********************************************************/ assign flag = F2 & !F1;assign c = b & !a;/***************************************/ endmodule 代码涵义就不讲解了 2、test bench 代码,与上面相同,这里不重复了 3、上图 看波形

深入分析verilog阻塞和非阻塞赋值

- Verilog(109207)

- 阻塞(8028)

- 非阻塞(2154)

相关推荐

FPGA基础篇(一):阻塞与非阻塞赋值,不只是比原始信号差一个时钟周期的问题!(深入剖析)

阻塞与非阻塞赋值 首先从名字上理解,阻塞赋值即赋值没完成,后边的语句将无法执行,非阻塞刚好与其相反,即赋值完不完成并不阻碍后续程序的执行,所以我们常说非阻塞赋值的对象并未立马得到新值,如果从时序来看

2017-09-19 18:32:43 11967

11967

11967

11967Verilog语言中阻塞和非阻塞赋值的不同

来源:《Verilog数字系统设计(夏宇闻)》 阻塞和非阻塞赋值的语言结构是Verilog 语言中最难理解概念之一。甚至有些很有经验的Verilog 设计工程师也不能完全正确地理解:何时使用非阻塞

2021-08-17 16:18:17 6000

6000

6000

6000Verilog HDL语言编程的误区与经验

Verilog的两个误区:使用Reg类 型还是Net类型:Reg类 型只在过程块中被赋值;而Net类型则在过 程块外面被赋值或者驱动.阻塞赋值和非阻塞赋值:Verilog中竞争发生的条件:两个或多个

2019-03-26 08:00:00

Verilog阻塞和非阻塞原理分析

Verilog阻塞和非阻塞原理分析在Verilog语言最难弄明白的结构中“非阻塞赋值”要算一个。甚至是一些很有经验的工程师也不完全明白“非阻塞赋值”在仿真器(符合IEEE标准的)里是怎样被设定执行

2009-11-23 12:02:57

Verilog中阻塞赋值和非阻塞赋值的正确使用

[table][tr][td] Verilog中有两种为变量赋值的方法。一种叫做连续赋值,另一种叫做过程赋值。过程赋值又分为阻塞赋值和非阻塞赋值。阻塞性赋值使用“=”为变量赋值,在赋值结束前不可以进行其他操作,在赋值结束之后继续后面的操作。这个过程就好像阻断了程序的运行。非阻塞赋值使用“

2018-07-03 03:06:04

Verilog流水线加法器always块中应该采用阻塞赋值(=),还是非阻塞赋值(<=)?

图一图二图三图四最近写了一个16位二级流水线加法器,并进行了一下仿真。发现在always块中采用阻塞赋值(=)和非阻塞赋值(

2016-09-09 09:18:13

Verilog过程赋值语句提问

时,dreg还是变成了areg这样不就是延时3个时钟周期了吗?为什么不是这样呢?另外,阻塞型赋值语句,规定是,顺序执行语句,每种状态一个接一个执行,非阻塞型赋值语句,规定是,并行赋值语句,当执行语句时同事计算

2017-09-20 15:10:01

verilog 非阻塞赋值的综合

刚学verilog,试了一下非阻塞赋值,代码如下, 很简单module test(clk,in,out);input clk;input in;output reg out;always @(posedge clk)out

2012-10-30 09:20:14

verilog中的阻塞和非阻塞

这个是非阻塞赋值,b的值为0,仿真结果也是0module TOP(input clk,input rst,output reg b );reg a,c;always@(posedge clk or negedge rst)beginif(~rst)begina

2015-09-13 15:55:05

电子发烧友App

电子发烧友App

评论