原文链接:熬夜到了1点了,终于写出了1602的时钟计数器代码。为什么是时钟计数器呢?因为我还没来得及做校准时间,所以只能称之为时钟计数器,不能成为电子钟。网上很少用人公开这一类代码,一搜FPGA 1602,都是写一个静态的显示,在实际应用中,是没有用的,因此这个简单的例子,给大家抛砖引玉了!上代码: Qii 9.0编译过,21EDA 开发板测试OKmodule LCD ( rst, key1, clk, rw, rs, en, data ); input clk,rst,key1; output rs,en,rw; output [7:0] data; reg rs,en_sel; reg [7:0] data; reg [7:0] shi,fen,miao; reg [31:0]count,count1; //LCD CLK 分频计数器 reg lcd_clk; reg [7:0] one_1,one_2,one_3,one_4,one_5,one_6,one_7,one_8,one_9,one_10,one_11,one_12,one_13,one_14,one_15,one_16; reg [7:0] two_1,two_2,two_3,two_4,two_5,two_6,two_7,two_8,two_9,two_10,two_11,two_12,two_13,two_14,two_15,two_16; reg [7:0] next,xianshi,two; parameter state0 =8'h00, //设置8位格式,2行,5*7 8'h38; state1 =8'h01, //整体显示,关光标,不闪烁 8'h0C 闪烁 8'h0e state2 =8'h02, //设定输入方式,增量不移位 8'h06 state3 =8'h03, //清除显示 8'h01 state4 =8'h04, //显示第一行的指令 80H state5 =8'h05, //显示第二行的指令 80H+40H scan =8'h06, nul =8'h07; parameter data0 =8'h10, //2行,共32个数据 data1 =8'h11, data2 =8'h12, data3 =8'h13, data4 =8'h14, data5 =8'h15, data6 =8'h16, data7 =8'h17, data8 =8'h18, data9 =8'h19, data10 =8'h20, data11 =8'h21, data12 =8'h22, data13 =8'h23, data14 =8'h24, data15 =8'h25, data16 =8'h26, data17 =8'h27, data18 =8'h28, data19 =8'h29, data20 =8'h30, data21 =8'h31, data22 =8'h32, data23 =8'h33, data24 =8'h34, data25 =8'h35, data26 =8'h36, data27 =8'h37, data28 =8'h38, data29 =8'h39, data30 =8'h40, data31 =8'h41; initial //初始值 begin //第一行显示 TEL:13868160569 one_1<="T"; one_2<="E"; one_3<="L"; one_4<=":"; one_5<="1"; one_6<="3"; one_7<="8"; one_8<="6"; one_9<="8";one_10<="1";one_11<="6";one_12<="0";one_13<="5";one_14<="6";one_15<="9";one_16<=" "; //第二行显示 Clock:00-00-00 two_1<="C"; two_2<="l"; two_3<="o"; two_4<="c"; two_5<="k"; two_6<=":"; two_7<=" "; two_8<=" "; two_9<="-";two_10<=" ";two_11<=" ";two_12<="-";two_13<=" ";two_14<=" ";two_15<=" ";two_16<=" "; shi<=0;fen<=0;miao<=0; end always @(posedge clk ) //获得LCD时钟 begin count<=count+1; if(count==250000) begin count<=0; lcd_clk<=~lcd_clk; end end always @(posedge clk or negedge rst ) //时钟计数器 begin if(!rst) begin shi<=0;fen<=0;miao<=0; count1<=0; end else begin en_sel<=1; two_7<= (shi/10)+8'b00110000; two_8<= (shi%10)+8'b00110000; two_10<=(fen/10)+8'b00110000; two_11<=(fen%10)+8'b00110000; two_13<=(miao/10)+8'b00110000; two_14<=(miao%10)+8'b00110000; count1<=count1+1'b1; if(count1==49999999) // 时钟计数 begin count1<=0; miao<=miao+1; if(miao==59) begin miao<=0; fen<=fen+1; if(fen==59) begin fen<=0; shi<=shi+1; if(shi==23) begin shi<=0; end end end end end end always @(posedge lcd_clk ) begin case(next) state0 : begin rs<=0; data<=8'h38; next<=state1; end //配置液晶 state1 : begin rs<=0; data<=8'h0e; next<=state2; end state2 : begin rs<=0; data<=8'h06; next<=state3; end state3 : begin rs<=0; data<=8'h01; next<=state4; end state4 : begin rs<=0; data<=8'h80; next<=data0; end //显示第一行 data0 : begin rs<=1; data<=one_1; next<=data1 ; end data1 : begin rs<=1; data<=one_2; next<=data2 ; end data2 : begin rs<=1; data<=one_3; next<=data3 ; end data3 : begin rs<=1; data<=one_4; next<=data4 ; end data4 : begin rs<=1; data<=one_5; next<=data5 ; end data5 : begin rs<=1; data<=one_6; next<=data6 ; end data6 : begin rs<=1; data<=one_7; next<=data7 ; end data7 : begin rs<=1; data<=one_8; next<=data8 ; end data8 : begin rs<=1; data<=one_9; next<=data9 ; end data9 : begin rs<=1; data<=one_10; next<=data10 ; end data10 : begin rs<=1; data<=one_11; next<=data11 ; end data11 : begin rs<=1; data<=one_12; next<=data12 ; end data12 : begin rs<=1; data<=one_13; next<=data13 ; end data13 : begin rs<=1; data<=one_14; next<=data14 ; end data14 : begin rs<=1; data<=one_15; next<=data15 ; end data15 : begin rs<=1; data<=one_16; next<=state5 ; end state5: begin rs<=0;data<=8'hC0; next<=data16; end //显示第二行 data16 : begin rs<=1; data<=two_1; next<=data17 ; end data17 : begin rs<=1; data<=two_2; next<=data18 ; end data18 : begin rs<=1; data<=two_3; next<=data19 ; end data19 : begin rs<=1; data<=two_4; next<=data20 ; end data20 : begin rs<=1; data<=two_5; next<=data21 ; end data21 : begin rs<=1; data<=two_6; next<=data22 ; end data22 : begin rs<=1; data<=two_7; next<=data23 ; end data23 : begin rs<=1; data<=two_8; next<=data24 ; end data24 : begin rs<=1; data<=two_9; next<=data25 ; end data25 : begin rs<=1; data<=two_10; next<=data26 ; end data26 : begin rs<=1; data<=two_11; next<=data27 ; end data27 : begin rs<=1; data<=two_12; next<=data28 ; end data28 : begin rs<=1; data<=two_13; next<=data29 ; end data29 : begin rs<=1; data<=two_14; next<=data30 ; end data30 : begin rs<=1; data<=two_15; next<=data31 ; end data31 : begin rs<=1; data<=two_16; next<=scan ; end scan : //交替更新第一行和第二行数据 begin next<=state4; end default: next<=state0; endcase end assign en=lcd_clk && en_sel; assign rw=0;endmodule

FPGA verilog实现的1602时钟计数器

- FPGA(591969)

- 1602时钟计数器(726)

相关推荐

计数器应用实例

计数器应用实例

除了计数功能外,计数器产品还有一些附加功能,如异步复位、预置数(注意,有同步预置数和异步预置数两种。前者受时钟脉冲控制,后者不受时钟

2010-05-27 09:37:55 5544

5544

5544

5544

基于FPGA和单片机的多功能计数器设计

本文设计了一种以超低功耗单片机MSP430F149为控制器,以高速的FPGA(现场可编程门阵列)实现等精度测量正弦信号的频率、周期和相位差的多功能计数器。在设计中依据等精度计数原理,应

2012-07-16 16:02:09 4299

4299

4299

4299

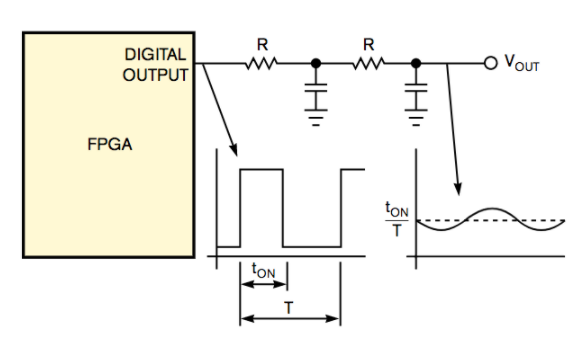

如何通过交换位提高FPGA-PWM计数器性能

1 )。 图1 一个简单的低通滤波器将FPGA的PWM数字输出更改为模拟电压电平。最大纹波出现在占空比为50%的情况下。 假设Enable为高电平,则计数器在每个时钟周期递增计数,PWM输出的频率为时钟频率除以2个计数位。您可以使用启用将其连接到预分频器来降低输

2021-05-13 16:22:44 4592

4592

4592

4592

32位MCU APT32F1023F6U6在计数器的应用

计数器不仅具有对时钟脉冲计数功能,还具有多种输出和控制功能,通过对参数进行设置,可实现频率、转速以及计数之间的转换。

2022-07-26 11:25:59 503

503

503

50310进制计数器是什么?

学习这门技术也越来越重要,很多人都开启了学习机器学习,本文就介绍了机器学习的基础内容。提示:以下是本篇文章正文内容,编程实现10进制计数器,具有异步复位功能,十位和个位用8421BCD码表示一、4选1多路选择器是什么?示例:pandas 是基于NumPy 的一种工具,该工具是为了解决

2022-02-09 07:33:15

FPGA verilog语言学习 加法器

我是刚开始学FPGA,现在对其verilog语言还不是很懂。下面题目:设计一个十进制的加法计数器,功能包含复位信号,置位信号,每个时钟的正跳变沿计数器加一。计数0-99即可。请帮忙给个参考的程序。

2012-05-11 23:03:24

FPGA提高篇——禁止使用分频时钟、计数器时钟

,分享给大家吧。——高手应该是这样做时钟信号的。禁止用计数器分频后的信号做其它模块的时钟,而要用改成时钟使能的方式。否则这种时钟满天飞的方式对设计的可靠性极为不利,也大大增加了静态时序分析的复杂性。时钟

2018-08-08 11:13:26

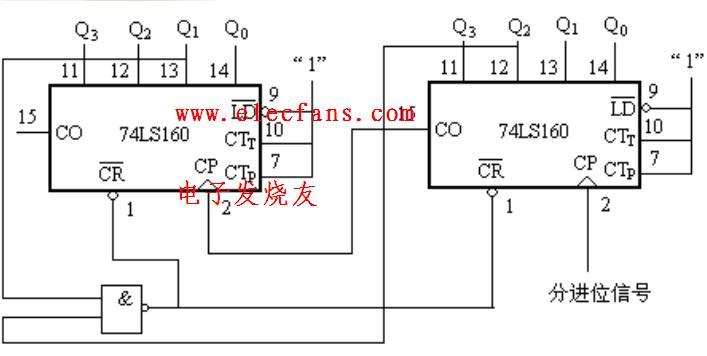

N进制计数器的实现

N进制计数器的实现 一、用集成计数器可以实现任意进制的计数器二、集成计数器控制功能的归类三、集成计数器的级联扩展四、复位法组成任意进制加法计数器五、置位法组成任意进制加法计数器六

2008-07-05 13:41:26

SysTick计数器有哪些应用呢

实现软件的短时间延迟利用 Cortex-M3 内核包含的 SysTick 时钟代替 Delay(N) ,实现延时N毫秒的精确值。SysTick 为一个24位递减计数器,SysTick 设定初值并使能

2021-12-07 09:37:56

stm32时钟选择计数器

时钟选择计数器时钟可以由下列时钟源提供1.内部时钟(CK_INT)2.外部时钟模式1:外部输入脚(TIx)3.外部时钟模式2:外部触发输入(ETR)4.内部触发输入(ITRx):使用一个定时器作为

2021-08-18 08:24:57

【FPGA】UART的计数器模块的实现方式

计数器模块的功能是可控地在输入时钟驱动下进行计数,当到达计数上阈时给 UART 内核一个提示信号。在不同的工作状态下,计数器模块的输入时钟是不同的。UART 在数据发送之前需要进行数据加载(即将串行

2018-10-23 10:02:16

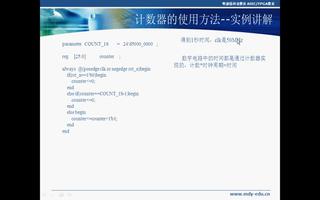

【verilog每日一练】计数器计时

已知外部输入时钟信号clk为50MHz,请用verilog实现计数器的计时1秒钟,每间隔1秒输出一个clk时钟周期的脉冲信号flag,参考波形如下:

2023-08-17 09:13:59

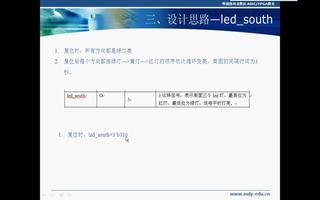

【连载视频教程(五)】小梅哥FPGA设计思想与验证方法视频教程之BCD码计数器设计验证

讲解数字系统,尤其是时钟系统中非常常见的一个模块——BCD码计数器的设计实现与验证,讲解Verilog基础语法,了解BCD码技术器与普通二进制计数器的区别。BCD码计数器经常用在需要十进制计数,十进制

2015-09-23 12:39:23

关于FPGA在仿真软件中计数器提前计数的问题

FPGA的人来说,非常之实用。但是,部分工程师在做仿真时,有时候会出现违反这一原则的奇怪现象。例如下面这个案例。关于在仿真软件中,为什么计数器的判定会在不满足加一条件的时候进行加一操作(如下图所示

2020-04-24 14:54:53

关于计数器的疑问

最近在看《现代操作系统》,他提到了时钟维持实际时间,在每个时钟滴答将计数器加1即可实现。但要注意位溢出(32位计数器),可以通过以下方法解决:使用64位计数器:缺点是这种方法使得计数器加一操作的代价很高,1s内维护很多次计数器。我不太懂红色字体的意思

2018-05-04 11:36:41

双边计数器无法在Spartan上工作

我正在尝试实现一个verilog代码,用于计算时钟的转换(ei:正向和负向转换)。以下verilog代码使用由“dualedgeregister”模块实现的双边沿寄存器。我使用其中的8个

2019-06-21 07:09:56

在FPGA中设计实现24进制加法计数器的设计

1、实现一个24进制加法计数器的设计本实验设计实现一个24进制的加法计数器,它由晶体振荡器、分频器、计数器和数码管显示器组成,图6.1是该加法计数器的示意图。晶体振荡器产生稳定的50MHz的脉冲信号

2022-07-05 15:14:27

在FPGA开发板上实现一个电子秒表的计数器模块设计

1、设计一个电子秒表的计数器模块在上一例中,使用了FPGA开发板上的拨码开关控制四位数码管进行动态显示,在本例中,我们将数码管作为一个整体IP,然后用一个计数器驱动它实现一个电子秒表的功能。根据这一

2022-07-29 14:57:01

基于FPGA的任意分频器设计

的时钟触发计数器进行计数,当计数器从0计数到N/2-1时,将输出时钟进行翻转,并给计数器一个复位信号,以使下一个时钟开始从零计数。以此循环,就可以实现偶数倍分频。以10分频为例,相应的verilog

2014-06-19 16:15:28

基于verilog的数字时钟程序

基于verilog的数字时钟程序,时钟芯片基础——60进制计数器设计目的让nexys 4板上的7段码LED显示时钟信息,其中包括时钟的小时,分钟,秒钟部分,且能够实现时钟的停止计时信号,手动调整小时

2021-07-22 07:37:01

如何在FPGA中实现实时时钟或时间和日期计数器

嗨,我是Xilinx FPGA的新手。我该如何在FPGA中实现实时时钟或时间和日期计数器?Xilinx是否为Artix 7提供任何RTC核心或IP?非常感谢您的建议。

2020-05-22 12:41:35

如何设计一个实际可用的计数器

我需要设计一个计数器,时钟变化几十个才计数一次。我先用了一个计数器随时钟计数,然后用组合逻辑判断做加法,modelsim仿真可以成功但是上板子后无法实现功能,希望大家能帮忙解决一下。书写的主要代码如下:always@(count)begin if(count==10'd0) beginCNP_ON

2017-03-14 16:49:53

定时器、计数器是什么

对内部时钟信号或外部输入信号进行计数,当计数值达到设定要求时,向CPU提出中断处理请求,从而实现定时或者计数功能的外设。定时/计数器的最基本工作原理是进行计数。作为定时器时,计数信号的来源选择周期性的内部时钟脉冲;用作计数器时,计数信号的来源选择非周期性的外部输入信号。不管是定时器还是计数器,本质上

2022-01-11 07:55:05

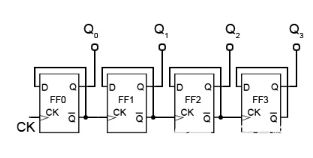

小程序大道理---计数器与行波时钟(转)

之前写过一篇关于 “加法器” 的博文,研究了加法器的底层电路,本来想要研究一下“行波时钟”,由于涉及到计数器,那么就先看看 “计数器” 在FPGA中综合后是什么样的 ?然后再看“行波时钟”的情况

2014-03-24 17:27:51

怎么实现两个32位计数器计数速率高达3GHz

中实现每个计数器的剩余28位。然后将外部4位引入FPGA,并且两个32位计数器将由加法器求和,然后主机处理器可以读取结果。虽然外部4位仍然会在FPGA的频率过高时切换,但在对计数器求和之前,时钟将停止

2019-04-19 13:34:34

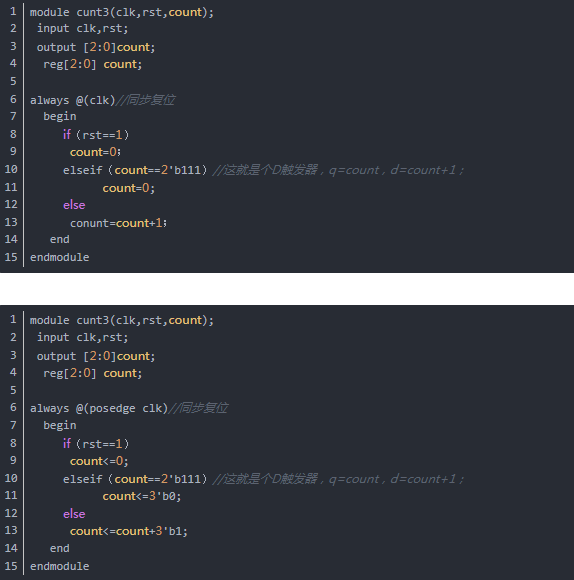

怎么使用D触发器设计计数器verilog

你好,我是verilog /逻辑设计的新手。我不确定问题属于哪里,如果不是,请告诉我,谢谢我想用D触发器构建一个3位计数器我在阅读了“逻辑设计的基本原理(Charles H. Roth)”一书后写了

2019-02-14 06:13:32

怎么用verilog语言设计一个100进制的可逆计数器,可以实现加减,置数,清零,进位,借位功能,大佬求帮助?

怎么用verilog语言设计一个100进制的可逆计数器,可以实现加减,置数,清零,进位,借位功能,大佬求帮助!

2019-05-13 15:41:23

用Verilog实现1602显示的时钟计数器

] data; reg rs,en_sel; reg [7:0] data; reg [7:0] shi,fen,miao; reg [31:0]count,count1;//LCD CLK 分频计数器

2019-07-15 09:39:54

用Verilog语言怎么写一个60进制的计数器然后显示在数码管上

小弟刚学FPGA用的是EP4CE6现在想写一个60进制的计数器 然后在数码管上显示出来用verilog写但想了好几天没想出来去大侠指导下或给个程序看看小弟感激不尽。。。。。拜托了

2014-09-16 18:29:27

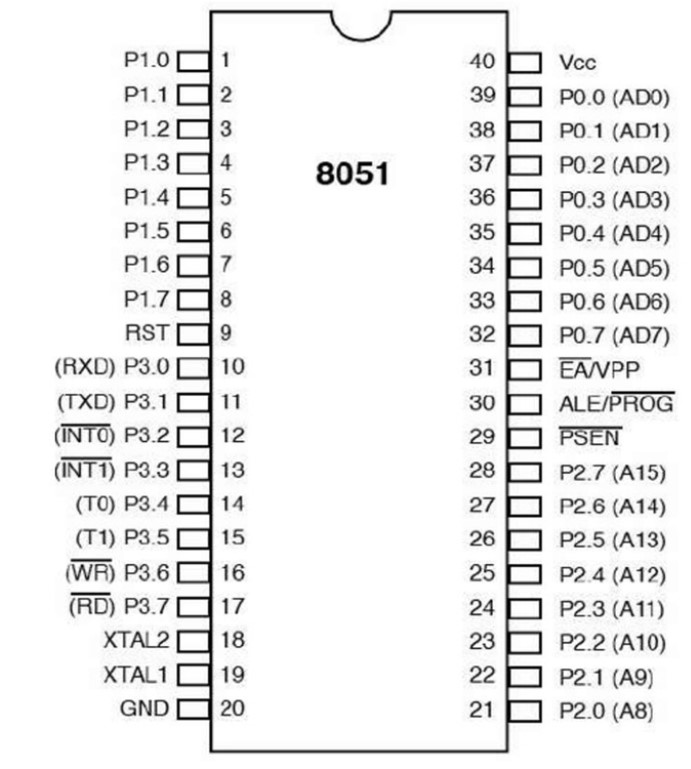

频率计数器的实现原理是什么

这里我们所讲的开发板是CT107D,频率计数器这一部分,比较容易。物理连接上,只需要把单片机开发版上的P34管脚和SIGNAL用跳线连接即可。下面,我们将直接进入代码分析和频率计数器的实现原理分析

2022-02-23 07:36:22

1602液晶的6位计数器程序

;******************************;1602液晶6位计数器:本程序调试通过 *;************************************;* 硬件:此程序

2010-04-21 22:44:19 54

54

54

54什么是二进制计数器,二进制计数器原理是什么?

什么是二进制计数器,二进制计数器原理是什么?

计数器是数字系统中用得较多的基本逻辑器件。它不仅能记录输入时钟脉冲的个数,还可以实现

2010-03-08 13:16:34 30352

30352

30352

30352计数器,计数器的工作原理是什么?

计数器,计数器的工作原理是什么?

在数字系统中使用最多的时序电路是计数器。计数器不仅能用于对时钟脉冲进行计数还可以用于分频、定时,产生

2010-03-08 13:50:14 59934

59934

59934

59934FPGA实现数字时钟

在Quartus Ⅱ开发环境下,用Verilog HDL硬件描述语言设计了一个可以在FPGA芯片上实现的数字时钟. 通过将设计代码下载到FPGA的开发平台Altera DE2开发板上进行了功能验证. 由于数字时钟的通用

2011-11-29 16:51:43 178

178

178

17824进制计数器的设计

集成计数器常见的是多位二进制计数器及十进制计数器,当需要实现其它进制计数器时,通常利用现有的集成计数器进行适当的连接而构成。对于当设计要求没有限定计数器的状态编码时电路设计的灵活性问题已有文献进行

2017-11-09 16:36:16 81

81

81

81基于FPGA的同步复位的3位计数器设计

分析:首先,我们可以看到有哪些信号。复位rst 、计数器3位的、时钟信号。(用到2路选择器。复位和不复位)

其次,怎样实现,一个时钟过来,记一次数就是加一次,保存(用到D触发器),满之后为0;

2019-02-01 07:08:00 2354

2354

2354

2354

MOD计数器和时序图

计数器的工作是通过每个时钟脉冲将计数器的内容提前一个计数来计数。当被时钟输入激活时推进其数字或状态序列的计数器被称为以“递增计数”模式操作。同样,当被时钟输入激活时减少其数字或状态序列的计数器被称为以“倒计数”模式操作。在UP和DOWN模式下工作的计数器称为双向计数器。

2019-06-23 07:47:00 12722

12722

12722

12722

使用单片机实现LCD1602脉冲计数器的程序和仿真电路图免费下载

本文档的主要内容详细介绍的是使用单片机实现LCD1602脉冲计数器的程序和仿真电路图免费下载。

2020-10-09 08:00:00 10

10

10

10FPGA设计中DAC控制的Verilog实现

FPGA设计中DAC控制的Verilog实现(单片机电源维修)-该文档为FPGA设计中DAC控制的Verilog实现资料,讲解的还不错,感兴趣的可以下载看看…………………………

2021-07-26 12:18:48 18

18

18

18基于单片机定时器/计数器的时钟设计及计数设计

基于单片机定时器/计数器的时钟设计以及计数设计第一部分 前言第二部分 定时器/计数器的原理MCS-51定时器/计数器的结构定时器/计数器相关特殊功能寄存器定时器/计数器工作方式第三部分 定时器

2021-11-05 09:06:00 51

51

51

51Johnson约翰逊计数器Verilog实现

扭环形计数器,约翰逊计数器,每次状态变化时仅有一个触发器发生翻转,译码不存在竞争冒险,在n(n≥3)位计数器中,使用2n个状态,有2^n-2n个状态未使用;

2022-06-15 09:27:57 1971

1971

1971

1971异步计数器的主要类型

异步计数器是那些输出不受时钟信号影响的计数器。由于异步计数器中的触发器提供有不同的时钟信号,因此在产生输出时可能会有延迟。设计异步计数器所需的逻辑门数量非常少,所以它们的设计很简单。异步计数器的另一个名称是“波纹计数器”。

2022-10-11 17:16:44 3994

3994

3994

3994

Xilinx Spartan 6 FPGA上的0到999计数器

电子发烧友网站提供《Xilinx Spartan 6 FPGA上的0到999计数器.zip》资料免费下载

2022-11-23 10:27:06 2

2

2

2基于FPGA的十进制计数器

本方案是一个基于 FPGA 的十进制计数器。共阳极 7 段显示器上的 0 到 9 十进制计数器,硬件在 Xilinx Spartan 6 FPGA 板上实现。

2022-12-20 14:52:25 2

2

2

2同步计数器和异步计数器是什么 同步计数器和异步计数器的主要区别?

在数字电子产品中,计数器是由一系列触发器组成的时序逻辑电路。顾名思义,计数器用于计算输入在负或正边沿转换中出现的次数。根据触发触发器的方式,计数器可以分为两类:同步计数器和异步计数器。了解这两种计数器的工作原理以及它们之间的区别。

2023-03-25 17:31:07 18649

18649

18649

18649

PLC计数器例子之3个计数器构成的24小时时钟

控制要求 利用 3 个计数器配合 1s 时钟脉冲标志 M1013,构成一个标准 24 小时时钟。 元件说明 控制程序 程序说明

2023-04-17 15:43:31 0

0

0

0同步计数器和异步计数器的区别主要在哪里

同步计数器和异步计数器的区别详解 同步计数器和异步计数器是数字电路中两种常见的计数器类型,它们在实现方式和功能上存在明显的区别。本文将详细介绍同步计数器和异步计数器的区别,包括其工作原理、特点

2023-12-13 14:54:24 1724

1724

1724

17244017计数器的工作原理

中,我们将详细介绍4017计数器的工作原理。 4017计数器的内部结构非常复杂,但核心的原理相对简单。它包含一个时钟输入引脚(CLK),一个复位输入引脚(RESET),以及10个输出引脚(Q0-Q9)。时钟输入引脚接收来自外部时钟源的时钟信号,当时钟信

2023-12-15 09:24:28 731

731

731

731计数器怎么用 计数器的作用有哪些

计数器是一种被广泛应用于各个领域的实用工具,在我们的日常生活中随处可见。无论是进行时间统计,协助工作任务的完成,还是用于科学研究和编程技术,在各个领域都起到了重要的作用。本文将详细介绍计数器

2024-02-03 10:04:14 589

589

589

589 电子发烧友App

电子发烧友App

评论