1.Virtex6 GTX Transceiver简介 在Xilinx的Virtex6 FPGA中,GTX作为一种低功耗的吉比特收发器,配置灵活,功能强大,并与FPGA内部的其他逻辑资源紧密联系,可用于实现多种高速接口(如XAUI、PCIE等)。V6 系列的FPGA中,GTX工作带宽范围是600 Mb/s到6.6 Gb/s,支持收发双向,且收发双向独立。GTX接收和发送方向均由PMA和PCS两部分组成,PCS提供丰富的物理编码层特性,如8b/10b编码、时钟校准等功能;PMA部分为模拟电路,提供高性能的串行接口特性,如预加重、均衡等功能。GTX同时还提供动态重配置接口,用于动态的修改GTX的配置。

2.GTX时钟与布局在Virtix6 FPGA中,GTX是以Quad为单位组织的,每个Quad包含4个GTX和2对差分时钟输入。当整个芯片多个GTX被使用时,需要合理的分布GTX与时钟输入。从一个Quad输入的时钟往上只能给相邻的一个Quad提供参考时钟,往下也只能给相邻的一个Quad提供参考时钟输入,最多只能驱动三个Quad,当整个芯片多个GTX使用到同样的参考时钟输入时,合理的分布时钟输入可以节省需要的时钟数量,也可以为时钟的提供冗余设计。

因此,基本的原则是同一个物理接口的几个GTX放在一起,由同一个参考时钟作为时钟输入;不同物理接口的GTX如果在同一个参考时钟的驱动覆盖范围内,可以采用同一个参考时钟输入。有条件的情况下,可以做时钟备份;当一个时钟可以覆盖更多个GTX的时候,考虑到时钟驱动能力的不确定性,为留有更多余量,没必要使用到极限(一个时钟驱动12个GTX)。另外在V5的GTP中,关于多个GTP共用同一个参考时钟输入,要求在这个输入时钟的时钟链上,每一个GTP都被使用(即使不需要,也要例化),不允许共用同一个参考时钟的两个GTP中间有一个没有使用的GTP。

3.预加重和均衡当GTX收发器出现信号质量不佳、数据丢包、传输误码等的情形时,为提高信号质量,可以调整GTX的预加重、均衡、输出振幅的值,以及调整采样点的位置,来优化GTX通道的通信质量。在高速串行接口上,高频分量衰减比低频分量更严重,导致信号失真。因此,在数据发送方向可以调整预加重值和输出振幅来提高信号质量。预加重用于增加信号中高频分量的强度,预加重的值由参数TXPREEMPHASIS[3:0]来设定。调整振幅用于增加信号的整体强度,振幅强度由参数TXDIFFCTRL[3:0]来设定。在数据接收方向可以调整均衡的值,还可以调整采样点在采样窗中的位置。均衡用于补偿接收信号中的高频分量,使接收到的信号恢复原状,均衡值由参数RXEQMIX[2:0]。采样点设置可以选择采样窗的眼中,使采样更稳定。以上参数的取值以及各个值的意义,请参见《Virtex-6 FPGA GTX Transceivers User Guide》(UG336)。

4.GTX的调试手段Virtex6 GTX提供了四种不同的环回,分别是近端PCS环回、近端PMA环回、远端PCS环回、远端PMA环回,可用于定位问题出现在GTX的哪个部分。同时,通过观察GTX输出的PLL时钟锁定信号,可以分析问题是否和时钟相关。Xilinx提供了一系列的GTX Transceiver调试手段和工具,最有用的就是使用Chipscope进行IBERT比特流误码率测试(即PRBS,伪随机二进制序列误码率测试)。关于IBERT(PRBS)测试的详细内容,将另有博文来介绍。

Virtex6 GTX设计总结:预加重、均衡、输出振幅的值

- FPGA(591969)

- Xilinx(119164)

相关推荐

8个GTX TX通道的Virtex-6 VC6VLX240TFF1156-3失败

我有一个带有8个GTX TX通道的Virtex-6 VC6VLX240TFF1156-3项目。我正在使用EDK 13.3。根据coregen示例HDL,每个GTX TX通道都有一个相关的用户时钟

2018-10-23 10:30:06

GTX可以生成和接收LVDS信号吗?

亲爱的Xilinx人,我有一些简单的问题要问。我正在使用Virtex 6 SX475T进行PCB设计。我正在考虑添加一个扩展端口,它有2对CML和6对LVDS信号。从用户指南,我认为一个GTX银行

2020-06-13 08:38:27

Virtex-6有专用的clkout(PLL输出)引脚吗?

你好。如今,我设计了使用Virtex-6的主板。我想知道Virtex-6是否有专用的PLL输出引脚(clkout引脚)。我检查了Virtex-6系列概述Virtex-6 FPGA时钟资源用户指南

2020-06-12 10:05:21

Virtex-6电源去耦的疑问如何解答

你好,在阅读Virtex-6 PCB设计UG(ug373)和http://forums.xilinx.com/t5/Virtex

2020-06-15 16:27:01

Virtex6内部错误的解决办法?

你好;我将FPGA代码从Virtext 5(240t)迁移到virtex6(xc6vsx475t-2ff1156)。我在合成期间收到错误消息: 目标设备:xc6

2020-06-03 16:42:14

Virtex6后备故障如何解决

我正在运行一个使用Master SPI配置的virtex6。我的黄金图像位于地址0x000000处,它指向0x100000以供下一个要加载的图像。当地址0x100000具有良好的图像时,它会正确加载

2020-06-15 12:34:36

Virtex6怎么配置寄存器初始值

你好我想配置寄存器初始值。有任何约束(UCF)可以实现吗?环境 -Virtex6 -ISE 14.7以上来自于谷歌翻译以下为原文Hello I want to configure

2018-10-26 15:03:36

Virtex 6 GTX耗尽资源的解决办法?

您好,我正在使用Plan Ahead 14.7和Virtex6 xc6vlx240tff1759-2目标FPGA。我的设备中有一个PCIe内核,它使用了FPGA中可用的24个GTX通道。我有5个通信

2020-06-17 07:46:51

Virtex 6 FPGA的目标阻抗值是什么?

嗨,我目前正在使用75K Virtex-6 FPGA(XC6VLX75T_FFG484)。如果我们看一下Virtex-6 FPGA PCB设计指南(ug373-ver 1.3.1)中的“PCB去耦

2020-06-18 15:30:22

Virtex 6 MMCM输入时钟源问题怎么解决

嗨,我使用Virtex6 LX75T和4个高速DAC设计了一块电路板。我将每个DAC连接到一个FPGA io Bank,我使用MRCC引脚作为MMCM(差分)的时钟输入,4个引脚用于片外反馈。不幸

2020-06-16 10:06:19

Virtex 6 如何使用PCIe端口连接定制板

嗨,我正在尝试将子板连接到Virtex6 ML605评估板的PCI-e端口。我想使用相关的pinas通用IO引脚。我在MAP中遇到错误(包:1107错误)。涉及的符号:BUF符号“b19_IBUF

2020-06-02 16:41:45

virtex-6 FPGA的存储条件是什么

你好我搜索了virtex-6的数据表,但我找不到有关virtex-6XC6VLX240T-1FFG1156C FPGA的存储信息,我想保留一段时间,FPGA的最大值是多少?或者我在哪里可以找到相关信息?谢谢希望你的回答

2020-06-17 13:39:05

virtex6中使用SRIO时遇到了一些问题怎么解决

大家好,我在virtex6中使用SRIO时遇到了一些问题。所以我试着用ibert来测试他的问题所在。但测试也失败了。我不知道出了什么问题.Plase帮帮我!非常感谢你。

2020-06-19 10:15:08

virtex6配置电路设计问题求助

我使用的是virtex6下的HX38OT-1155,并没有使用官方推荐的system ACE配置方式,只采用JTAG配置模式。配置bank0设计原理图和附件,第一次设计硬件,有的地方可能有问题,还希望发现问题的诸位不惜赐教。谢谢!

2014-09-02 15:12:04

预加重是什么意思

预加重是什么意思理论证明鉴频器的输出噪声功率谱按频率的平方规律增加。但是,许多实际的消息信号,例如语言、音乐等,它们的功率谱随频率的增加而减小,其大部分能量集中在低频范围内。这就造成消息信号高频端

2010-03-30 12:13:52

ISE12.3 PAR不完全但LUT使用率仅为38%(Virtex6器件)

嗨,我使用ISE12.3(Virtex6设备)并在我们的设计上多次尝试,所有PAR结果都是不完全路由的信号。我发现时间限制不符合保持时间问题(差异-0.018ns)。如何检查此问题以及综合,PAR或

2018-10-09 15:38:50

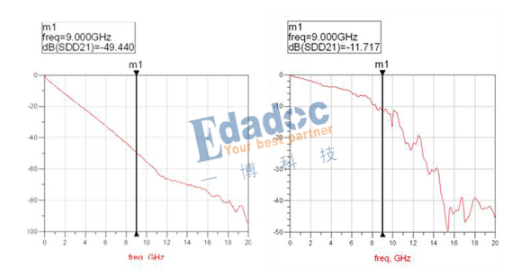

JESD204B 串行链路的均衡器优化

去加重均衡技术来准备供传输的 7.4 Gbps 串行数据。通过配置,用户可以优化输出驱动器的去加重设置 (DEM) 和输出电压摆幅设置 (VOD),以便反向匹配信道特征。实验表明可通过 20 英寸

2015-05-11 10:40:44

LT8631UX HDMI2.0 / 1.4自适应均衡RX输入和预加重TX输出

1.说明Lontium LT8631UX HDMI2.0 / 1.4开关具有符合HDMI2.0 / 1.4规格的3:1开关,最大6Gbps高速数据速率,自适应均衡RX输入和预加重TX输出,以支持长

2022-03-03 14:41:11

LVDS发送器IP可用于Virtex6和Virtex7 FPGA吗

嗨,LVDS发送器IP(基于OpenLDI,像素和控制数据转换为LVDS信号)可用于Virtex6和Virtex7 FPGA吗?谢谢克里希纳

2020-06-17 14:52:28

SFP铜缆预加重驱动器MAX3982相关资料下载

SFP铜缆预加重驱动器MAX3982资料下载内容主要介绍了:MAX3982引脚功能MAX3982功能和特性MAX3982应用范围MAX3982内部方框图MAX3982极限参数MAX3982典型应用电路

2021-04-01 07:05:05

USB3.0信号延长增益

最近在做一个USB3.0的延长方案,一直都只能做到3M长度,始终无法突破,调节各种增益都不行。3.0调节参数无非就是均衡器EQ、预加重(Pre_emphasis)、去加重(De_emphasis

2017-04-11 16:52:03

Unrecognized technology: ”VIRTEX6“

我用synplify去综合,出现了错误,error:Unrecognized technology: ”VIRTEX6“error:Device Part not found:"XC6VSX315T"

2013-11-09 17:11:45

Xilinx Virtex-6系列选型

Xilinx Virtex-6系列选型1 Xilinx公司Virtex-6 FPGA共有3个系列:Virtex-6 LXT – 高逻辑密度,高速串行收发器,高密度IOVirtex-6 HXT – 高

2012-02-28 14:56:59

srio_v5_6 IP核使用发生错误

'srio_icon_gen.i_srio_icon'。引脚名称拼写错误可能导致此问题,缺少edif或ngc文件,块名称与edif或ngc文件名之间的大小写不匹配,或者类型名称的拼写错误。目标'virtex6'不支持符号'srio_icon

2018-10-08 11:10:47

【紧急求助】Xilinx Virtex6 FPGA与PC端千兆网口通信问题

这段时间在调试FPGA与PC的千兆网口通信,用到Virtex6 Tri Mode Ethernet IP Core,遇到诸多问题,例如: 1、我用的是xilinx的virtex6中

2013-12-25 16:40:16

使用Virtex-6 FPGA GTX收发器向导出现错误的解决办法?

嗨,我正在使用Virtex-6 FPGA GTX收发器向导,版本1.12。我使用Web包许可证进行模拟。device = xc6vlx75tdevicefamily = virtex6

2020-06-17 13:58:20

使用Virtex 6和14.4映射错误

我的目标是使用EDK 14.4进行Virtex 6的设计。我收到了自动插入GTX收发器的错误,因此我按照http://www.xilinx.com/support/answers

2018-10-19 14:33:57

使用gtx没有输出

使用GTX核输出一个序列,仿真结果和我想要的结果一致。

如图所示输出结果为一个不到1M的方波。不到1M是防止示波器速率不够。

我的板子有4个GTX,两个在PCIE上,两个在网口上。我把把串行输出

2023-10-12 15:16:22

关于virtex6的XILINX Platform Cable USB 问题

本帖最后由 mr.pengyongche 于 2013-4-30 03:08 编辑

请问各位前辈,我手里有一个XILINX Platform Cable USB 的下载器,能够下载virtex4程序我现在需要下载virtex6 的程序,这个下载器支持virtex6

2012-07-09 09:58:17

具有接收均衡器的1Gbps至10Gbps预加重驱动器MAX3984相关资料下载

的24 AWG电缆* 驱动30in的FR-4* 可选1000mVP-P或1200mVP-P差分输出摆幅* 可选输出预加重* 可选输入均衡* LOS检测内建噪声抑制* 传输关闭* 可热插拔三

2021-05-17 06:16:25

利用IBERT核对GTX收发器板级测试

8b10b编码、时钟校准等功能,PMA部分为模拟电路,提供高性能的串行接口特性,如预加重、均衡等功能。GTX同时还提供动态配置接口,用于动态的修改GTX的配置。

IBERT 工具的环回模式有近端PCS环回

2023-06-21 11:23:12

哪里可以找到有关Virtex-6GTX CDR PLL锁定时间的信息?

eHi亲爱的社区希望你们中的一些人还在身边。有谁知道我在哪里可以找到有关Virtex-6GTX CDR PLL锁定时间的信息?我试图在一段时间内使用GTX暂停模式,这样它只在需要时突发数据包。因此

2019-11-06 06:23:58

在Virtex-5/6 GTP / GTX收发器中如何实现JTAG

你好,关于GTP / GTX收发器的JTAG实现,我有几个问题。1. JTAG是否针对GTP / GTX收发器实现(因此可以驱动和读取引脚以进行电路板验证)2. JTAG组件放在GTP磁贴中的哪个

2020-06-18 14:41:02

在原始GTX E1中应该为Virtex 6 GTX PLL TX_TDCC_CFG使用什么值

我手动配置GTX(GTXE1)的PLL以使用100MHz至125MHz范围内的输入时钟。我已经从文档(ug366)中找到了合法的价值来实现这一目标。但它表示TX_TDCC_CFG的正确值由

2020-07-13 12:46:08

在同一FPGA上运行的两个不同系统是否具有相同的FIT值?

Xilinx器件可靠性报告”时,我看到所有FPGA的FIT值都归类于工艺技术中,而Virtex6的FIT值明显低于Spartan6(约为34%)。我好几天都在搜索这个话题,但我找不到确切的答案。为什么FIT率被

2020-03-12 11:16:18

基于Virtex-5 LXT的串行背板接口设计

速率高达数千兆比特的远距离(通常可达40英寸或更远)信号传输。这两种均衡方法都是通过增强高频信号分量和衰减低频信号分量,来最大限度地降低符号间干扰(ISI)的影响。区别在于,预加重是对线路驱动器输出

2019-04-16 07:00:07

如何使用Virtex6 LX760和ISE13.4

你好,我使用Virtex6 LX760和ISE13.4是否有可能在PAR之后混淆BRAM(类似于将所需的BRAM内容合并到已生成的位文件中)。或者我必须在合成之前做到这一点?提前致谢!

2020-06-16 07:09:04

如何使用相邻GTX磁贴的外部时钟

你好,我在两个通过串行背板连接的Virtex 6 FPGA中实现了一个简单的4通道Aurora 8b / 10b内核。每个磁贴的专用GTX时钟是固定的 - 在FPGA0上为312.5Mhz,在

2020-06-18 10:21:39

如何寻找Virtex6和7Series部件的类似亚稳态参数测量

/Metastable-Delay-in-Virtex-FPGAs/ba-p/7996有Virtex4和Virtex5的测量。我正在寻找Virtex6和7Series部件的类似亚稳态参数测量。是否存在应用说明?我猜猜V6& 7应该比

2020-07-18 16:58:50

如何将Aurora与Virtex-6 LX240t配合使用

嗨,我正在尝试将Aurora与Virtex-6 LX240t配合使用。示例设计是由核心生成器(11.5和12.1)生成的测试代码。当我使用环回模式(近端PCS和PMA)进行测试时,两者都能正常工作

2020-06-02 13:14:40

如何将FX3的Tx去加重设置值设置为 “0”?

,请告诉我怎么做。

例如,是否可以将 Tx 去加重 (dB) 的值设置为 0x00,用于上述社区中描述的 Tx 去加重?

Tx 去加重 (dB) = 20 *log10 [(128 − 2 * tx_去加重值) /128]

2024-02-23 06:05:44

如何将Vitesse交叉点连接到Virtex 6 GTX输入

你好,如何将Vitesse交叉点(VSC3308)连接到Virtex6 GTX输入?交叉点数据输出电压摆幅可在400-1100mVpp之间调节,而共模电压为2V。我不能使用隔直电容。有解决方案的人?

2020-06-18 14:53:12

如何建立Spartan 6和Virtex 6之间的通信?

亲爱的专家 我尝试通过GTP(S6)/ GTX(V6)在SP605(Spartan6)和ML605(Virtex6)之间建立通信, 我想连接两个主板的SFPlight模块,并且定义极光协议,但我

2019-07-31 10:37:43

如何通过JTAG使用iMPACT SW在virtex4设备上执行回读

在网上找到了几个bitgen命令:“-g GLUTMASK_B:0”用于virtex6设备,“ - g write_glutmask_b:yes”用于virtes5设备。这些选项都不

2020-06-19 06:41:40

如何采用Virtex 4的SLC NAND闪存

或SD的SPI接口。我们将推出兼容ONFI的4Gb Micron SLC NAND芯片。似乎Virtex6和Kintex7有一个核心,但它们在AXI总线上。只是想知道是否有人找到了将ONFI闪存

2020-06-17 09:54:32

怎么通过GTX SMA连接器进行FPGA通信?

大家好 我正在尝试在FPGA V6之间建立通信链接。我正在关注“LogiCORE IP Virtex-6FPGA GTX收发器向导v1.9”文档。在测试示例中使用PCIeconnectors但我想

2020-05-19 07:35:21

改变7系列GTX发射器线路速率的步骤谁有吗?

您好,我一直在论坛和互联网上搜索,以及查看UG476,我还没有找到改变7系列GTX发射器(Kintex 7)线路速率的步骤已配置(不进行部分重新配置)。我找到的唯一指南是Virtex5 GTX

2020-07-27 10:28:44

无法将GTX速率设置为高于6.6 Gbps的值

你好当我将7系列收发器向导用于Kintex-7设备(XC7K70T)时,我无法将GTX速率设置为高于6.6 Gbps的值。 Kintex-7 GTX应该以11.3 Gbps的速度运行,但似乎只适用于

2019-03-06 09:49:16

有没有应用IC或电路能够改变GTX的输出共模电压?

我使用Virtex-6 GTX生成LVDS信号来测试我的LVDS接收器能力。我使用交流耦合来阻止GTX直流偏置,并使用上拉电阻将交流电容器连接到新的直流偏置,它可以正常工作。但是当我发送一个特殊

2020-06-10 08:47:41

求virtex5与部分重新配置教程?

嗨,我是学生 我尝试使用virtex5与部分重新配置教程UG702,但本教程设计为virtex6(ML605)所以我需要修复它 为virtex5创建新的综合和网表(从源代码复制.v文件并运行合成

2020-06-16 07:28:38

缺少ISE Design Suite的设备

我为我的班级下载了ISE Webpak,我们使用的是Virtex6系列设备。在家庭下有一个完整的设备列表,但现在只剩下一个(XC6BLX75T)。我重新安装了ISE,甚至为virtex6重新安装并

2019-04-16 13:45:20

请问Virtex7 GTX如何生成PIPE接口PCIE PHY?

选择的情况下,生成以下输入和输出端口的GTX,其在ug476_7Series_Transceivers(GTX).pdf和pg168-gtwizard.pdf中未提及。我想知道如何正确连接这些信号

2020-05-04 09:05:44

请问virtex 6 FPGA的这种电流是否正常?

大家好,当我测试virtex6 FPGA时,我遇到了一些奇怪的事情。我之前从未为FPGA供电,这是第一次为FPGA供电FPGA的电源电压如下:VCCINT:1.0VVCCO:2.5VVCCAUX

2020-06-17 13:50:43

请问GTP和GTX兼容吗?

生成了一个TX唯一的Aurora 8b10b内核(GTP),为Virtex7生成了一个仅限RX的Aurora 8b10b内核(GTX)。我的参考时钟是125MHz,而我的DRP / INIT时钟都是

2020-07-31 11:27:52

请问如何使用virtex6连接外部设备?

Aoa ....我想将外部时钟IC DS1307与我的FPGA板(Virtex ML605)连接。这是我的项目的要求,如果您曾经使用FPGA板连接外部IC /设备,请回复。谢谢

2020-04-29 09:41:33

请问如何将GS3440与GTX端口连接?

我想知道如何将Kintex-7 GTX端口与GS3440(3G / HD / SD自适应电缆均衡器)的差分输出接口。我可以使用直流DC耦合器还是必须使用AC耦合GTX端口?以下是GS3440数据表中的信息。非常感谢。大卫。

2020-07-26 13:29:55

采用XPS 12.3的Virtex6 ML605上的PCIe该怎么使用?

大家好,在获得我的ML605 Virtex6(Production Silicon)开发板之后,我尝试用XPS生成一个系统。我只使用默认设置而不添加或删除任何核心。遗憾的是,PCIe总线

2019-08-26 10:56:44

高速串行接口互联小议分享

)和均衡功能(Equalization)。提起这个去加重,如果接触过Altera带Transceiver的FPGA的同志应该了解,Altera的这些产品中的GXB均有预加重和均衡的功能。所谓预加重是在

2015-01-22 14:20:51

Virtex-6 FPGA GTX收发 User Guide

Virtex-6 FPGA GTX收发 User Guide:This document shows how to use the GTX transceivers in Virtex

2009-12-31 17:05:28 25

25

25

25ADN8102ACPZ-R7是一款均衡器

ADN8102是一款四通道双向CX4电缆/背板均衡器,具有八路PECL/CML兼容型差分输入和八路CML差分输出;输入提供可编程均衡,输出提供可编程输出电平及预加重或去加重。该器件针对NRZ数据

2023-07-11 11:01:52

MAX3987 8.5Gbps四通道均衡器和预加重驱动器

MAX3987 8.5Gbps四通道均衡器和预加重驱动器

MAX3987是4通道接收和发送均衡器(EQ),用于补偿FR4带状线/微带线和/或高速电缆中的传输介质损耗。器件可以

2010-01-15 15:35:17 1102

1102

1102

1102MAX4951C 双通道均衡和预加重

该MAX4951C双通道均衡和预加重和输入缓冲区是理想的redrive内部串行ATA(SATA)的1i,2i的信息,和3i信号以及100万和200万个eSATA信号

2011-04-08 10:22:13 1594

1594

1594

1594Virtex6 FPGA GTX和Spartan6 FPGA GTP收发器的电源模块

bstract: This reference design enables a complete solution for powering Xilinx Virtex-6 FPGA GTX

2017-04-05 10:15:57 17

17

17

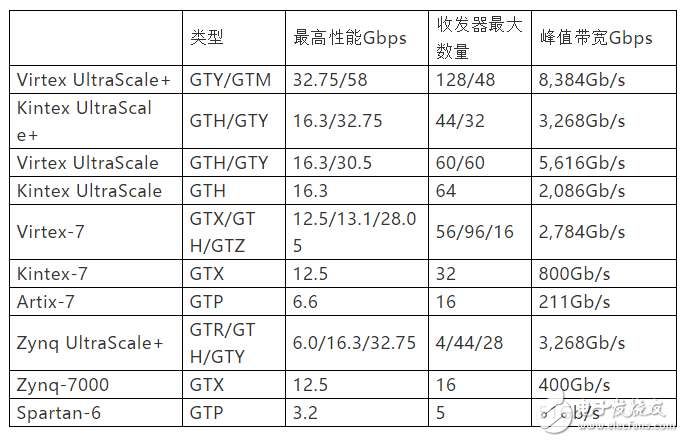

17Xilinx不同FPGA集成的GTx及性能

GTx接收和发送方向均由PCS和PMA两部分组成,PCS提供丰富的物理编码层特性,如8b/10b编码等;PMA部分为模拟电路,提供高性能的串行接口特性,如预加重与均衡。

2018-06-29 08:47:00 10526

10526

10526

10526

比较 Xilinx® Virtex®-7FPGA GTH收发器和Altera Stratix V GX收发器的均衡能力

设计人员呼吁提升10G+ 芯片到芯片和背板性能, 依赖接收机均衡来补偿信号失真。观看视频, 并排比较 Xilinx® Virtex®-7 FPGA GTH 收发器 和 Altera Stratix V GX 收发器的均衡能力。

2018-05-23 15:47:00 3974

3974

3974

3974

virtex-7 GTX的Chipscope集成误码率测试资料说明

用于virtex™-7 FPGA GTX收发器的Chipscope™Pro ibert核心是可定制的,设计用于评估和监控virtex-7 FPGA GTX收发器。该核心包括在FPGA逻辑中实现的模式

2019-02-25 16:43:08 15

15

15

15串行系列:预加重与均衡的优缺点总结

在这对于预加重与均衡的优缺点稍微做一下总结: 1.预加重实现起来比均衡要简单,功耗低一些。 2.预加重增益不能做太大,一个1.1Vpp的输出不可能预加重后转化为5Vpp的输出。 3.预加重会增加通道

2021-04-13 17:34:03 3923

3923

3923

3923

电子发烧友App

电子发烧友App

评论