您编写的代码是不是虽然在仿真器中表现正常,但是在现场却断断续续出错?要不然就是有可能在您使用更高版本的工具链进行编译时,它开始出错。您检查自己的测试平台,并确认测试已经做到100%的完全覆盖,而且所有测试均未出现任何差错,但是问题仍然顽疾难除。

虽然设计人员极其重视编码和仿真,但是他们对芯片在FGPA中的内部操作却知之甚少,这是情有可原的。因此,不正确的逻辑综合和时序问题(而非逻辑错误)成为大多数逻辑故障的根源。

但是,只要设计人员措施得当,就能轻松编写出能够创建可预测、可靠逻辑的FPGA代码。

在FPGA设计过程中,需要在编译阶段进行逻辑综合与相关时序收敛。而包括I/O单元结构、异步逻辑和时序约束等众多方面,都会对编译进程产生巨大影响,致使其每一轮都会在工具链中产生不同的结果。为了更好、更快地完成时序收敛,我们来进一步探讨如何消除这些差异。

I/O 单元结构

所有FPGA都具有可实现高度定制的I/O引脚。定制会影响到时序、驱动强度、终端以及许多其它方面。如果您未明确定义I/O单元结构,则您的工具链往往会采用您预期或者不希望采用的默认结构。如下VHDL代码的目的是采用“sda: inout std_logic;”声明创建一个称为 sda 的双向I/O缓冲器。

tri_state_proc : PROCESS (sys_clk)BEGINif rising_edge(sys_clk) thenif (enable_in = '1') thensda <= data_in;elsedata_out <= sda;sda <= 'Z';end if;end if;END PROCESS tri_state_proc;

当综合工具发现这组代码时,其中缺乏如何实施双向缓冲器的明确指示。因此,工具会做出最合理的猜测。

实现上述任务的一种方法是, 在FPGA的I/O环上采用双向缓冲器(事实上,这是一种理想的实施方式)。另一种选择是采用三态输出缓冲器和输入缓冲器,二者都在查询表 (LUT) 逻辑中实施。最后一种可行方法是,在I/O环上采用三态输出缓冲器,同时在LUT中采用输入缓冲器,这是大多数综合器选用的方法。

这三种方法都可以生成有效逻辑,但是后两种实施方式会在I/O引脚与LUT之间传输信号时产生更长的路由延迟。此外,它们还需要附加的时序约束,以确保时序收敛。FPGA编辑器清晰表明:在图1中,我们的双向I/O有一部分散布在I/O缓冲器之外。

教训是切记不要让综合工具猜测如何实施代码的关键部分。即使综合后的逻辑碰巧达到您的预期,在综合工具进入新版本时情况也有可能发生改变。

应当明确定义您的I/O逻辑和所有关键逻辑。以下VHDL代码显示了如何采用Xilinx? IOBUF原语对I/O缓冲器进行隐含定义。另外需要注意的是,采用相似方式明确定义缓冲器的所有电气特性。

sda_buff: IOBUFg e n e r i c m a p ( I O S TANDARD =>"LVCMOS25",IFD_DELAY_VALUE => "0", DRIVE =>12,SLEW => "SLOW")port map(o=> data_out, io=> sda,i=> data_in, t=> enable_in);

在图2中,FPGA编辑器明确显示,我们已完全在I/O缓冲器内部实施了双向I/O。

异步逻辑的劣势异步代码会产生难以约束、仿真及调试的逻辑。异步逻辑往往产生间歇性错误,而且这些错误几乎无法重现。另外,无法生成用于检测异步逻辑所导致的错误的测试平台。

虽然异步逻辑看起来可能容易检测,但是,事实上它经常不经检测;因此,设计人员必须小心异步逻辑在设计中隐藏的许多方面。所有钟控逻辑都需要一个最短建立与保持时间,而且这一点同样适用于触发器的复位输入。以下代码采用异步复位。在此无法为了满足触发器的建立与保持时间需求而应用时序约束。

data_proc : PROCESS (sys_clk,reset)BEGINif (reset = '1') thendata_in <= '0';elsif rising_edge(sys_clk) thendata_in <= serial_in;end if;END PROCESS data_proc;

下列代码采用同步复位。但是,大多数系统的复位信号都可能是按键开关,或是与系统时钟无关的其它信号源。尽管复位信号大部分情况是静态的,而且长期处于断言或解除断言状态,不过其水平仍然会有所变化。相当于系统时钟上升沿,复位解除断言可以违反触发器的建立时间要求,而对此无法约束。

data_proc : PROCESS (sys_clk)BEGINif rising_edge(sys_clk) thenif (reset = '1') thendata_in <= '0';elsedata_in <= serial_in;end if;end if;END PROCESS data_proc;

只要我们明白无法直接将异步信号馈送到我们的同步逻辑中,就很容易解决这个问题。以下代码创建一个称sys_reset 的新复位信号,其已经与我们的系统时钟sys_clk同步化。在异步逻辑采样时会产生亚稳定性问题。我们可以采用与阶梯的前几级进行了‘与’运算的梯形采样降低此问题的发生几率。

data_proc : PROCESS (sys_clk)BEGINif rising_edge(sys_clk) thenreset_1 <= reset;reset_2 <= reset_1 and reset;sys_reset <= reset_2 and reset_1and reset;end if;if rising_edge(sys_clk) thenif (sys_reset = '1') thendata_in <= '0';elsedata_in <= serial_in;end if;end if;END PROCESS data_proc;

至此,假定您已经慎重实现了所有逻辑的同步化。不过,如果您不小心,则您的逻辑很容易与系统时钟脱节。切勿让您的工具链使用系统时钟所用的本地布线资源。那样做的话您就无法约束自己的逻辑。切记要明确定义所有的重要逻辑。

以下VHDL代码采用赛灵思 BUFG原语强制sys_clk进入驱动低延迟网络(low-skew net) 的专用高扇出缓冲器。

gclk1: BUFG port map (I => sys_clk,O=> sys_clk_bufg);data_proc : PROCESS (sys_clk_bufg)BEGINif rising_edge(sys_clk_bufg) thenreset_1 <= reset;reset_2 <= reset_1 and reset;sys_reset <= reset_2 and reset_1and reset;end if;if rising_edge(sys_clk_bufg) thenif (sys_reset = '1') thendata_in <= '0';elsedata_in <= serial_in;end if;end if;END PROCESS data_proc;

某些设计采用单个主时钟的分割版本来处理反序列化数据。以下VHDL代码(nibble_proc进程)举例说明了按系统时钟频率的四分之一采集的数据。

data_proc : PROCESS (sys_clk_bufg)BEGINif rising_edge(sys_clk_bufg) thenreset_1 <= reset;reset_2 <= reset_1 and reset;sys_reset <= reset_2 and reset_1and reset;end if;if rising_edge(sys_clk_bufg) thenif (sys_reset = '1') thentwo_bit_counter <= "00";divide_by_4 <= '0';nibble_wide_data <= "0000";elsetwo_bit_counter<= two_bit_counter + 1;divide_by_4 <= two_bit_counter(0) andtwo_bit_counter(1);nibble_wide_data(0)<= serial_in;nibble_wide_data(1)<= nibble_wide_data(0);nibble_wide_data(2)<= nibble_wide_data(1);nibble_wide_data(3)<= nibble_wide_data(2);end if;end if;END PROCESS data_proc;nibble_proc : PROCESS (divide_by_4)BEGINif rising_edge(divide_by_4) thenif (sys_reset = '1') thennibble_data_in <= "0000";elsenibble_data_in<= nibble_wide_data;end if;end if;END PROCESS nibble_proc;

看起来好像一切都已经同步化,但是nibble_proc采用乘积项divide_by_4对来自时钟域sys_clk_bufg的 nibble_wide_data进行采样。由于路由延迟,divde_by_4与sys_clk_bufg之间并无明确的相位关系。将divide_by_4转移到BUFG也于事无补,因为此进程会产生路由延迟。解决方法是将nibble_proc保持在sys_clk_bufg域,并且采用divide_by_4作为限定符,如下所示。

nibble_proc : PROCESS (sys_clk_bufg)BEGINif rising_edge(sys_clk_bufg) thenif (sys_reset = '1') thennibble_data_in <= "0000";elsif (divide_by_4 = '1') thennibble_data_in<= nibble_wide_data;end if;end if;END PROCESS nibble_proc

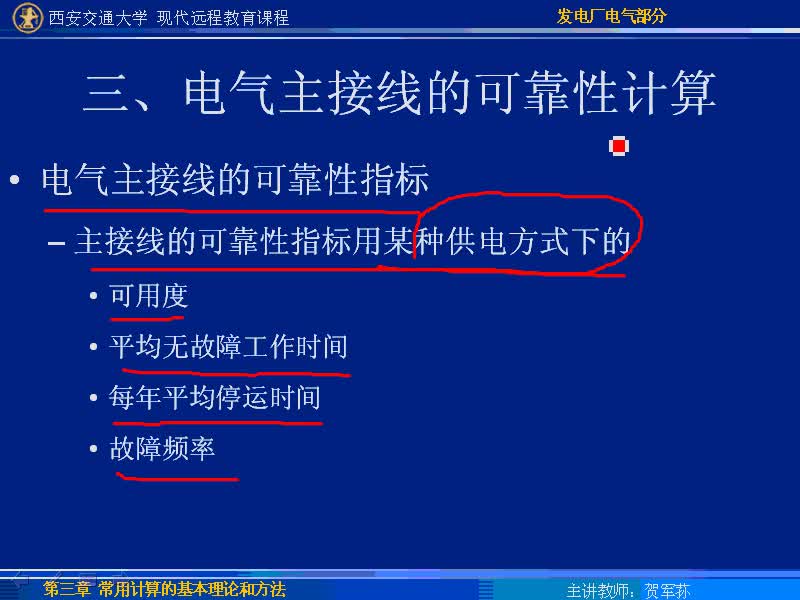

时序约束的重要性

如果您希望自己的逻辑正确运行,则必须采用正确的时序约束。如果您已经慎重确保代码全部同步且注册了全部I/O,则这些步骤可以显著简化时序收敛。在采用上述代码并且假定系统时钟为100MHz时,则只需四行代码就可以轻松完成时序约束文件,如下所示:

NET sys_clk_bufg TNM_NET =sys_clk_bufg;TIMESPEC TS_sys_clk_bufg = PERIODsys_clk_bufg 10 ns HIGH 50%;OFFSET = IN 6 ns BEFORE sys_clk;OFFSET = OUT 6 ns AFTER sys_clk;

请注意:赛灵思FPGA中I/O注册逻辑的建立与保持时间具有很高的固定性,在一个封装中切勿有太大更改。但是,我们仍然采用它们,主要用作可确保设计符合其系统参数的验证步骤。

三步简单操作

仅需遵循以下三步简单操作,设计人员即可轻松实施可靠的代码。

? 切勿让综合工具猜测您的预期。采用赛灵思原语对所有 I/O 引脚和关键逻辑进行明确定义。确保定义 I/O 引脚的电气特性;? 确保逻辑 100% 同步,并且让所有逻辑参考主时钟域;? 应用时序约束确保时序收敛。

只要遵循上述三个步骤,您就能够消除综合与时序导致的差异。扫除这两个主要障碍会让您获得具有100%可靠性的代码。

编写具有100%可靠性代码的几个技巧

- FPGA(591969)

- 赛灵思(130433)

相关推荐

可靠性与失效分析

和电子辅料等可靠性应用场景方面具有专业的检测、分析和试验能力,可为各研究院所、高校、企业提供产品的可靠性检测、失效分析、老化测试等一体化服务。本中心目前拥有各类可靠性检测分析仪器,其中包括

2018-06-04 16:13:50

可靠性工程技术简介

定取决于对产品进行FMEA的总体要求和产品的实际情况。 3. 建立功能框图。建立各模块的功能框图,并对各方框的功能给予标记代码,以便进行分析。 4. 建立可靠性框图。根据功能框图建立相应的可靠性框图,以便

2011-11-24 16:28:03

可靠性是什么?

可靠性是什么?充实一下这方面的知识 产品、系统在规定的条件下,规定的时间内,完成规定功能的能力称为可靠性。 这里的产品可以泛指任何系统、设备和元器件。产品可靠性定义的要素是三个“规定”:“规定

2015-08-04 11:04:27

可靠性检技术及可靠性检验职业资格取证

中国电子电器可靠性工程协会 关于举办“可靠性检技术及可靠性检验职业资格取证”培训班的通知各有关单位: 根据《中华人民共和国劳动法》劳动和社会保障部《招用技术工种

2010-08-27 08:25:03

可靠性汇编

电子可靠性资料汇编内容: 降额设计规范;电子工艺设计规范;电气设备安全通用要求设计规范 ;嵌入式

2010-10-04 22:31:56

可靠性管理概要

管理的特点以上管理活动的五项内容是互相、互相渗透、相辅相成的。可靠性管理在五项活动内容中具有的特点是,更突出了它的综合性、时间性和统计性。(1)综合性:它不是单纯从一个方面来衡量产品的优劣,而是从整体上

2009-05-24 16:49:57

可靠性设计分析系统

可靠性是我们在开展电子产品设计过程中常常绕不开的问题。例如,客户需要我们提供相关的可靠性预计报告,客户需要我们的产品提供相应的可靠性试验报告,或者企业内部需要控制产品质量,制定了一系列的可靠性工作

2017-12-08 10:47:19

可靠性验证

当组件上板后进行一系列的可靠性验证,可靠性验证过程中产品失效时,透过板阶整合失效分析能快速将失效接口找出,宜特协助客户厘清真因后能快速改版重新验证来达到产品通过验证并如期上市。 透过板阶整合失效分析

2018-08-28 16:32:38

GaN可靠性的测试

作者:Sandeep Bahl 最近,一位客户问我关于氮化镓(GaN)可靠性的问题:“JEDEC(电子设备工程联合委员会)似乎没把应用条件纳入到开关电源的范畴。我们将在最终产品里使用的任何GaN器件

2018-09-10 14:48:19

LED驱动电源可靠性设计的研究

000 h.所以LED 灯照明装置能否应用推广的关键环节之一是其驱动电源问题,笔者就提高大功率( 100 ~ 200 W) 驱动电源的可靠性从如下两大方面进行了探讨。 1 防水及降温处理 大功率LED

2019-06-01 15:47:32

LabVIEW开发的测试环境要如何验证自身的可靠性呢

LabVIEW开发的测试环境要如何验证自身的可靠性呢?这个环境是用来测试汽车仪表用的,可是不能保证环境自身的可靠性,那么测试的结果也就没有意义了。请高人指点下~!!

2017-09-26 08:07:49

SiC-MOSFET的可靠性

半导体的测试方法,其可靠性试验结果如下。从结果可以看出,ROHM的SiC-MOSFET具有足够的可靠性。关键要点:・ROHM的SiC-MOSFET与已经普及的Si-MOSFET具有相同的可靠性。

2018-11-30 11:30:41

[原创]可靠性

电子可靠性资料汇编内容: 降额设计规范;电子工艺设计规范;电气设备安全通用要求设计规范 ;嵌入式

2010-10-04 22:34:14

《电路可靠性案例征文》大赛

《电路可靠性案例征文》大赛主办方:硬件十万个为什么信号完整性 电子发烧友论文形式:不限参加方式:文档发送到微信号elecfans008评选标准:案例由《硬件十万个为什么》《信号完整性》《电子发烧友

2016-09-03 15:35:31

【可靠性分析第一步】构造可靠性模型

的,其位置不能变动,而系统的可靠性框图是根据各组成部分的故障对系统的影响来构成的,其位置在何处是没有关系的。 1、 串联系统 串联结构的系统是由几个功能器件(部件)组成,其中任何一个器件(部件

2016-09-03 15:47:58

【PCB】什么是高可靠性?

专业学术组织——可靠性技术组。1950年12月,美国成立了“电子设备可靠性专门委员会”,军方、武器制造公司及学术界开始介入可靠性研究,到1952年3月便提出了具有深远影响的建议;研究成果首先应用于航天

2020-07-03 11:09:11

【技术贴】关于5个9可靠性的疑惑

:不建议直接将可靠性预计值直接代入计算可用性,有条件的情况下,为了更接近现场,通常使用加速测试方案卡方分布单侧置信得出的MTBF值进行计算。说来也巧,在解答了上面的疑问后看到了“可靠性几个9

2018-03-05 13:10:23

为什么华秋要做高可靠性?

及品控规范,剖析可靠性的关键影响因素,定位可靠性的关键管控流程,建立可靠性定向提升体系,用行动践行承诺,全方位保障PCB的高可靠性。1)企业愿景:创造一家具有高度社会责任感的企业立壮志以成就客户!“华

2020-07-08 17:10:00

什么是高可靠性?

1952年3月便提出了具有深远影响的建议;研究成果首先应用于航天、军事、电子等军工工业,随后逐渐扩展到民用工业。60年代,随着航空航天工业的迅速发展,可靠性设计和试验方法被接受和应用于航空电子系统中

2020-07-03 11:18:02

单片机应用系统的可靠性与可靠性设计

现代电子系统的可靠性现代电子系统具有如下特点:嵌入式的计算机系统.智能化的体系结构;以计算机为核心的柔性硬件基础,由软件实现系统的功能;硬件系统有微电子技术的有力支持。单片机应用系统是当前最典型、最广

2021-01-11 09:34:49

单片机应用系统的可靠性特点

可靠性设计是单片机应甩系统设计必不可少的设计内容。本文从现代电子系统的可靠性出发,详细论述了单片机应用系统的可靠性特点。提出了芯片选择、电源设计、PCB制作、噪声失敏控制、程序失控回复等集合硬件系统

2021-02-05 07:57:48

基于FPGA的时统模块可靠性该怎么设计?

高可靠性永远是计算机系统中必不可少的重要需求,尤其是对于整个系统中用来产生统一时间信号的专用设备来说,其可靠性和精准性非常重要。时统模块的功能就是保证整个系统处在统一时间的基准上,它接收时统站发来

2019-08-26 06:27:46

基于集成电路的高可靠性电源设计

高可靠性系统设计包括使用容错设计方法和选择适合的组件,以满足预期环境条件并符合标准要求。本文专门探讨实现高可靠性电源的半导体解决方案,这类电源提供冗余、电路保护和远程系统管理。本文将突出显示,半导体技术的改进和新的安全功能怎样简化了设计,并提高了组件的可靠性。

2019-07-25 07:28:32

如何利用FPGA新特性提升汽车系统高可靠性?

目前,汽车中使用的复杂电子系统越来越多,而汽车系统的任何故障都会置乘客于险境,这就要求设计出具有“高度可靠性”的系统。同时,由于FPGA能够集成和实现复杂的功能,因而系统设计人员往往倾向于在这些系统中采用FPGA。

2019-09-27 07:45:33

如何实现高可靠性电源的半导体解决方案

高可靠性系统设计包括使用容错设计方法和选择适合的组件,以满足预期环境条件并符合标准要求。本文专门探讨实现高可靠性电源的半导体解决方案,这类电源提供冗余、电路保护和远程系统管理。本文将突出显示,半导体技术的改进和新的安全功能怎样简化了设计,并提高了组件的可靠性。

2021-03-18 07:49:20

如何才能获取高可靠性的印制板?

本文拟从印制板下游用户安装后质量、直接用户调试质量和产品使用质量三方面研究印制板的可靠性,从而表征出印制板加工质量的优劣并提供生产高可靠性印制板的基本途径。

2021-04-21 06:38:19

如何提高航空插头的可靠性?

:航空插头的可靠性主要是固有可靠性和使用可靠性这两个方面。航空插头的固有可靠性主要是指电连接器制造完成时所具有的可靠性,主要受电连接器的设计、工艺、制造、治理和原材料性能等诸多因素决定。电连接器在制作

2017-08-01 17:14:15

射频连接器可靠性如何提高

1 引言射频连接器的可靠性问题是整机或系统使用单非常关心和重视的问题。这是因为射频连接器作为一种元件应用在整机或系统中,它的可靠性直接影响或决定着整机或系统的可靠性。射频连接器的可靠性与其结构设计

2019-07-10 08:04:30

嵌入式系统产品的可靠性

通常来讲,在复杂的处理器选择中,最初的工程评估主要集中在性能和成本方面。然而,工业设备制造商的可靠性工程师看重的则是一整套不同的产品规格;这些规格主要侧重于避免并管理这些错误。对于诸如航空航天、军事

2018-08-30 14:43:15

开关电源设计的可靠性研究

波形呈矩形,其上升沿与下降沿包含大量的谐波成分,另外输出整流管的反向恢复也会产生电磁干扰(EMI),这是影响可靠性的不利因素,这使得系统具有电磁兼容性成为重要问题。其产生电磁干扰有三个必要条件:干扰源

2018-09-25 18:10:52

开发高可靠性嵌入式系统的技巧有哪些?

尽管许多嵌入式工程师充满了希望和梦想,但高可靠性的代码不是一蹴而就的。它是一个艰苦的过程,需要开发人员维护和管理系统的每个比特和字节。当一个应用程序被确认为“成功”的那一刻,通常会有一种如释重负

2019-09-29 08:10:15

提高PCB设备可靠性的几个方法?

金百泽技术团队总结了提高PCB设备可靠性的技术措施:方案选择、电路设计、电路板设计、结构设计、元器件选用、制作工艺等多方面着手,具体措施如下: (1)简化方案设计。方案设计时,在确保设备满足技术

2014-10-20 15:09:29

提高PCB设备可靠性的具体措施

提高PCB设备可靠性的技术措施:方案选择、电路设计、电路板设计、结构设计、元器件选用、制作工艺等多方面着手,具体措施如下: (1)简化方案设计。方案设计时,在确保设备满足技术、性能指标的前提下,应尽

2018-09-21 14:49:10

提高开关电源可靠性的技巧

上升沿与下降沿包含大量的谐波成分,另外输出整流管的反向恢复也会产生电磁干扰 (EMI),这是影响可靠性的不利因素,这使得系统具有电磁兼容性成为重要问题。其产生电磁干扰有三个必要条件:干扰源、传输介质

2018-10-09 14:11:30

提高电源可靠性设计的建议

电子产品的质量是技术性和可靠性两方面的综合。电源作为一个电子系统中重要的部件,其可靠性决定了整个系统的可靠性,开关电源由于体积小,效率高而在各个领域得到广泛应用,如何提高它的可靠性是电力电子技术

2018-10-09 14:37:18

机电产品的可靠性探讨

随着科学技术的迅速发展,机电产品在国防、工业、农业、商业、科研和民用等方面的应用种类越来越多,而且都离不开电源技术和其它技术的应用。如果在其应用中忽略了可靠性管理,机电产品的质量也不会得到保证

2011-03-10 14:32:20

浅析无线通信产品的各个阶段可靠性预计与实现

0、引言电子产品的可靠性预计一直是困扰各个无线通信公司的难题之一,目前比较通用的可靠性预计方法是由贝尔实验室在2001年推出的Bellcore-SR332方法。该方法的不足之处在于它仅根据产品

2019-06-19 08:24:45

浅谈手机环境可靠性试验

手机环境可靠性试验的目的 产品可靠性是设计和制造出来的,但必须通过试验予以验证。在手机的研制阶段,为了保证手机具有一定的可靠性水平或提高手机的可靠性,要通过可靠性增长试验暴露手机的缺陷,进而进行分析

2009-11-13 22:31:55

环境试验与可靠性试验的区别

深圳市华耀检测技术服务有限公司环境试验与可靠性试验虽然关系紧密,但它们在试验目的,所用环境应力数量,环境力量值选用准则,试验类型,试验时间,试验终止判据方面存在截然的不同之处。试验目的:环境试验考察

2022-01-13 14:03:37

电子产品可靠性试验的目的和方法

进行评价,并通过质量反馈来提高新产品可靠性水平。3. 筛选试验是一种对产品进行全数检验的非破坏性试验。其目的是为选择具有一定特性的产品或剔早期失效的产品,以提高产品的使用可靠性。产品在制造过程中,由于

2015-08-04 17:34:26

电源可靠性的设计经验分享

影响电源可靠性的因素。1、电压应力电源电压应力是保证电源可靠性的一个重要指标。在电源中有许多器件都有规定最大耐压值,比如:场效应管的Vds和Vgs、二极管的反向耐压、IC的最大VCC电压以及输入输出电容

2016-06-08 15:51:22

电源可靠性设计影响因素

影响电源可靠性的因素。 1、电压应力 电源电压应力是保证电源可靠性的一个重要指标。在电源中有许多器件都有规定最大耐压值,比如:场效应管的Vds和Vgs、二极管的反向耐压、IC的最大VCC电压以及

2018-10-09 10:49:22

电源可靠性设计的几个建议

,脉冲波形呈矩形,其上升沿与下降沿包含大量的谐波成分,另外输出整流管的反向恢复也会产生电磁干扰(EMI),这是影响可靠性的不利因素,这使得系统具有电磁兼容性成为重要问题。 产生电磁干扰有三个必要条件:干扰

2019-02-21 07:14:11

电路可靠性设计与元器件选型

足够强势,不必再由我添加压垮骆驼的那最后一根稻草;②产品的可靠性水平和研发的强势程度成反比;③电路设计错误和器件应用不当占了故障的八成因素。举几个简单例子:一个电解电容紧挨着散热片焊接的,与电解电容

2009-12-04 14:32:45

电路可靠性设计与元器件选型

送给了研发弟兄们几个总结性观点:①在公司里,研发队伍已经足够强势,不必再由我添加压垮骆驼的那最后一根稻草;②产品的可靠性水平和研发的强势程度成反比;③电路设计错误和器件应用不当占了故障的八成因素。举

2009-12-18 16:29:17

电路可靠性设计与元器件选型

队伍已经足够强势,不必再由我添加压垮骆驼的那最后一根稻草;②产品的可靠性水平和研发的强势程度成反比;③电路设计错误和器件应用不当占了故障的八成因素。举几个简单例子:一个电解电容紧挨着散热片焊接

2010-04-26 22:05:30

电路可靠性设计与元器件选型

队伍已经足够强势,不必再由我添加压垮骆驼的那最后一根稻草;②产品的可靠性水平和研发的强势程度成反比;③电路设计错误和器件应用不当占了故障的八成因素。举几个简单例子:一个电解电容紧挨着散热片焊接

2010-04-26 22:20:16

硬件电路的可靠性

我想问一下高速电路设计,是不是只要做好电源完整性分析和信号完整性分析,就可以保证系统的稳定了。要想达到高的可靠性,要做好哪些工作啊?在网上找了好久,也没有找到关于硬件可靠性的书籍。有经验的望给点提示。

2015-10-23 14:47:17

硬件设计说明中的可靠性设计包含哪些?

急求前辈指点!硬件设计说明中的可靠性设计一般包含哪些?现在需要整理项目的一些文档,关于可靠性设计要提供哪些文档一头雾水,求前辈指点一下!不胜感激!

2016-04-22 11:11:09

能提供AEC-Q100可靠性报告吗?

你好,CY7C1021CV33-10ZSXA AEC-Q100认证吗?如果是的话,你能提供我们的AEC-Q100可靠性报告吗?CY7C1021CV33-10ZSXA(AEC-Q100)。γ射线

2018-10-26 15:57:09

请问PCBA可靠性测试有什么标准可循吗?

刚刚接触PCBA可靠性,感觉和IC可靠性差异蛮大,也没有找到相应的测试标准。请问大佬们在做PCBA可靠性时是怎么做的,测试条件是根据什么设定?

2023-02-15 10:21:14

请问硬件设计说明中的可靠性设计包含什么?

急求帮助 硬件设计说明中的可靠性设计包含哪些?现在需要整理项目的一些文档,关于可靠性设计要提供哪些文档一头雾水,求前辈指点一下!不胜感激!

2020-04-08 03:04:58

电子发烧友App

电子发烧友App

评论