与前一段异步FIFO代码的主要区别在于,空/满状态标志的不同算法。

第一个算法:Clifford E. Cummings的文章中提到的STYLE #1,构造一个指针宽度为N+1,深度为2^N字节的FIFO(为便方比较将格雷码指针转换为二进制指针)。当指针的二进制码中最高位不一致而其它N位都 相等时,FIFO为满(在Clifford E. Cummings的文章中以格雷码表示是前两位均不相同,而后两位LSB相同为满,这与换成二进制表示的MSB不同其他相同为满是一样的)。当指针完全相 等时,FIFO为空。

这种方法思路非常明了,为了比较不同时钟产生的指针,需要把不同时钟域的信号同步到本时钟域中来,而使用Gray码的目的就是使这个异步同步化的过 程发生亚稳态的机率最小,而为什么要构造一个N+1的指针,Clifford E. Cummings也阐述的很明白,有兴趣的读者可以看下作者原文是怎么论述的,Clifford E. Cummings的这篇文章有Rev1.1 \ Rev1.2两个版本,两者在比较Gray码指针时的方法略有不同,个Rev1.2版更为精简。

第二种算法:Clifford E. Cummings的文章中提到的STYLE #2。它将FIFO地址分成了4部分,每部分分别用高两位的MSB 00 、01、 11、 10决定FIFO是否为going full 或going empty (即将满或空)。如果写指针的高两位MSB小于读指针的高两位MSB则FIFO为“几乎满”,若写指针的高两位MSB大于读指针的高两位MSB则FIFO 为“几乎空”。

它是利用将地址空间分成4个象限(也就是四个等大小的区域),然后观察两个指针的相对位置,如果写指针落后读指针一个象限(25%的距离,呵呵), 则证明很可能要写满,反之则很可能要读空,这个时候分别设置两个标志位dirset和dirrst,然后在地址完全相等的情况下,如果dirset有效就 是写满,如果dirrst有效就是读空。

这种方法对深度为2^N字节的FIFO只需N位的指针即可,处理的速度也较第一种方法快。

这段是说明的原话,算法一,还好理解。算法二,似乎没有说清楚,不太明白。有兴趣的可以查查论文,详细研究下。

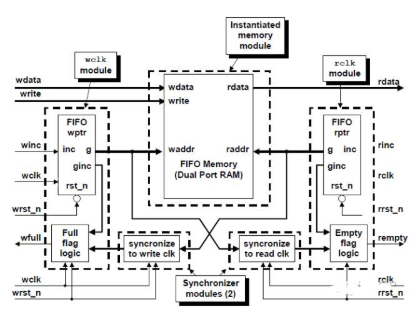

总之,第二种写法是推荐的写法。因为异步的多时钟设计应按以下几个原则进行设计:1,尽可能的将多时钟的逻辑电路(非同步器)分割为多个单时钟的模块,这样有利于静态时序分析工具来进行时序验证。2,同步器的实现应使得所有输入来自同一个时钟域,而使用另一个时钟域的异步时钟信号采样数据。3,面向时钟信号的命名方式可以帮助我们确定那些在不同异步时钟域间需要处理的信号。4,当存在多个跨时钟域的控制信号时,我们必须特别注意这些信号,保证这些控制信号到达新的时钟域仍然能够保持正确的顺序。

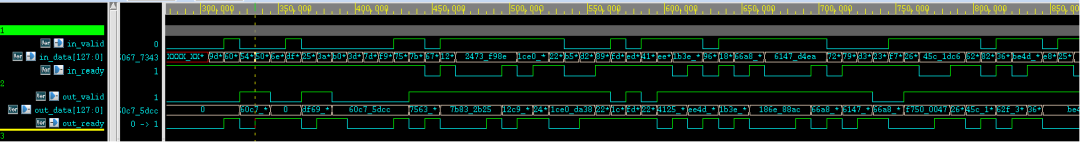

module fifo2 (rdata, wfull, rempty, wdata,winc, wclk, wrst_n, rinc, rclk, rrst_n);parameter DSIZE = 8;parameter ASIZE = 4;output [DSIZE-1:0] rdata;output wfull;output rempty;input [DSIZE-1:0] wdata;input winc, wclk, wrst_n;input rinc, rclk, rrst_n;wire [ASIZE-1:0] wptr, rptr;wire [ASIZE-1:0] waddr, raddr;async_cmp #(ASIZE) async_cmp(.aempty_n(aempty_n),.afull_n(afull_n),.wptr(wptr), .rptr(rptr),.wrst_n(wrst_n));fifomem2 #(DSIZE, ASIZE) fifomem2(.rdata(rdata),.wdata(wdata),.waddr(wptr),.raddr(rptr),.wclken(winc),.wclk(wclk));rptr_empty2 #(ASIZE) rptr_empty2(.rempty(rempty),.rptr(rptr),.aempty_n(aempty_n),.rinc(rinc),.rclk(rclk),.rrst_n(rrst_n));wptr_full2 #(ASIZE) wptr_full2(.wfull(wfull),.wptr(wptr),.afull_n(afull_n),.winc(winc),.wclk(wclk),.wrst_n(wrst_n));endmodulemodule fifomem2 (rdata, wdata, waddr, raddr, wclken, wclk);parameter DATASIZE = 8; // Memory data word widthparameter ADDRSIZE = 4; // Number of memory address bitsparameter DEPTH = 1<

.............................................................

- FIFO 同步、异步以及Verilog代码实现

- fifo(42998)

- 同步(19003)

- 异步(17994)

相关推荐

用FPGA芯片实现高速异步FIFO的一种方法

现代集成电路芯片中,随着设计规模的不断扩大。一个系统中往往含有数个时钟。多时钟带来的一个问题就是,如何设计异步时钟之间的接口电路。异步 FIFO(First In First Out)是解决这个问题的一种简便、快捷的解决方案。##异步FIFO的VHDL语言实现

2014-05-28 10:56:41 3405

3405

3405

3405基于FPGA的异步FIFO的实现

大家好,又到了每日学习的时间了,今天我们来聊一聊基于FPGA的异步FIFO的实现。 一、FIFO简介 FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,它与普通

2018-06-21 11:15:25 6164

6164

6164

6164

基于FPGA器件实现异步FIFO读写系统的设计

异步 FIFO 读写分别采用相互异步的不同时钟。在现代集成电路芯片中,随着设计规模的不断扩大,一个系统中往往含有数个时钟,多时钟域带来的一个问题就是,如何设计异步时钟之间的接口电路。异步 FIFO

2020-07-16 17:41:46 1050

1050

1050

1050

同步FIFO设计详解及代码分享

FIFO (先入先出, First In First Out )存储器,在 FPGA 和数字 IC 设计中非常常用。 根据接入的时钟信号,可以分为同步 FIFO 和异步 FIFO 。

2023-06-27 10:24:37 1199

1199

1199

1199

异步FIFO设计之格雷码

相邻的格雷码只有1bit的差异,因此格雷码常常用于异步fifo设计中,保证afifo的读地址(或写地址)被写时钟(或读时钟)采样时最多只有1bit发生跳变。

2023-11-01 17:37:31 779

779

779

779

FIFO为什么不能正常工作?

FIFO自带的set_max_delay生效? 对于异步FIFO,复位信号的使用要特别注意,如下图所示。复位信号必须和wr_clk同步,如果异步,要在wr_clk时钟下同步释放,否则会出现数据无法写入

2023-11-02 09:25:01 475

475

475

475

握手型接口的同步FIFO实现

按照正常的思路,在前文完成前向时序优化和后向时序优化后,后面紧跟的应该是双向时序优化策略了,不过不急,需要先实现一下握手型同步FIFO。

2023-12-04 14:03:49 263

263

263

263

Verilog基本电路设计(转)收藏

处理,同步FIFO,异步FIFO,时钟无缝切换,信号滤波debounce等等,后面会根据大家反馈情况再介绍新电路。首先介绍异步信号的跨时钟域同步问题。一般分为单bit的控制信号同步,以及多bit的数据

2016-09-15 19:08:15

verilog 异步复位同步释放

fpga 的 异步复位同步释放代码如下module asy_rst(clk,rst_n,asy_rst);input clk;input rst_n;output asy_rst;reg

2013-05-28 13:02:44

同步复位sync和异步复位async

[/td]同步复位sync异步复位async特点复位信号只有在时钟上升沿到来时才能有效。无论时钟沿是否到来,只要复位信号有效,就进行复位。Verilog描述always@(posedge CLK

2011-11-14 16:03:09

同步复位和异步复位的比较

[table][tr][td] 无论同步还是异步复位,在对触发器时序进行分析的时候,都要考虑复位端与时钟的相位关系。对于同步复位,复位信号可以理解为一个普通的数据信号,它只有在时钟的跳变沿才会其作用

2018-07-03 02:49:26

同步复位和异步复位的比较(转载)

。具体方式是:在异步复位后加上一个所谓的“reset synchronizer”,这样就可以使异步复位信号同步化,然后,再用经过处理的复位信号去作用系统,就可以保证比较稳定了。Verilog代码如下

2016-05-05 23:11:23

异步FIFO指针同步产生的问题

如图所示的异步FIFO,个人觉得在读写时钟同步时会产生两个时钟周期的延时,如果读写时钟频率相差不大,某一时刻读写指针相等,当写指针同步到读模块时会产生延时,实际同步到读模块的写指针是两个时钟周期之前的,这样就不会产生空满信号,要两个周期之后才能产生空满信号,结果是写溢出或读空

2015-08-29 18:30:49

异步slave fifo通讯方式的作用是什么?

XINLINX FPGA与CY7C68013通讯,异步slave fifo通讯方式,PKTEND信号的作用是什么,不用的话是不是应该拉高 ,另外由于fifo adr用的都公用地址线,时序上怎么选择,谁能共享一下verilog HDL的例子。

2015-07-10 15:17:28

FPGA片内异步FIFO实例

异步FIFO的读写时序。图9.72 异步FIFO实例功能框图本实例的异步FIFO与上一个实例的同步FIFO有别,这个异步FIFO不仅读写的位宽不同,读写的时钟也不同。异步FIFO对于跨时钟域的应用非常

2019-05-06 00:31:57

xilinx ISE 中异步FIFO ip的使用、仿真及各信号的讨论(图文教程)

` 本帖最后由 Bob-Liu 于 2018-5-2 16:38 编辑

xilinx ISE 中异步FIFO ip的使用、仿真及各信号的讨论(图文教程), 请下载附件。楼主原创帖汇总:1.单总线

2016-07-16 15:09:50

【锆石A4 FPGA试用体验】fifo实验(3)-用verilog实现同步fifo

数据满标志位,fifo写满置1read读使能信号,高电平有效fifo_emptyfifo空标志位,空时置1clock时钟信号fifo_halffifo写数据达到8个,或读数据时,fifo数据小于8个2、仿真波形(一)连续写数据至fifo满(二)连续读数据至fifo空(三)边写边读三、实验代码

2016-11-07 00:18:04

什么是良好的Verilog代码风格?

。2、代码示范为求直观,首先贴上一份示范代码,然后我再进行逐条详细解释。以下代码是我之前做的一个同步FIFO模块,代码如下:接下来,给大家详解一下我在进行这个模块设计的时候遵循了哪些希望向大家

2023-06-02 14:48:35

关于同步fifo做缓存的问题

异步fifo是用于跨时域时钟传输的,但是同步fifo做缓存我就不是很理解了,到底这个缓存是什么意思,这样一进一出,不是数据的传输吗,为什么加个fifo,还有,如果是两组视频流传输,在切换的过程中如何能保证无缝切换?希望哪位好心人帮我解答一下

2013-08-27 19:23:36

关于异步fifo的安全问题:

关于异步fifo的安全问题:1. 虽然异步fifo可以提供多个握手信号,但真正影响安全性能的就两个:2. 一个是读时钟域的空信号rdrempty3. 另一个是写时钟域的满信号wrfull4. 这是

2018-03-05 10:40:33

关于异步fifo里面读写指针同步器的问题,求教

这是网上比较流行的一个异步fifo方案,但是fifo的空满判断不是应该是立即的吗,加上同步器之后变成写指针要延时两个读周期再去个读指针做空比较,而读指针要延时两个写周期再去和写指针做满比较,这样虽然可以避免亚稳态之类的问题,可是这个延时对总体的空满判断没有影响吗,如果没有影响是怎么做到的呢,求解

2016-07-24 16:25:33

关于USB芯片68013的同步与异步的理解

给FIFO里面写数据就好,只要不超过芯片手册里的最大传输速度。看了一些网上写的verilog,表示对他们所表示的各个状态的实现都较难理解。网上说在slrd下沿的时候,进行写数据,我试着写了一个,还没有

2016-12-15 10:34:51

典型电路的Verilog代码介绍

典型电路的模板1 模板代码1.1 输出时序逻辑的模板代码1.1.1 异步复位的时序电路(用的最多)1.1.2 同步复位的时序电路1.2 输出组合逻辑的模板代码1.3 输出整个模块部分代码1.4 输出

2022-02-17 07:11:08

基于Verilog的垂直投影实现

垂直投影进行研究。二、方案基于Verilog的垂直投影的实现,考虑使用双口ram、fifo/shfit_rams 实现,但是使用ram实现时,由于要操作地址,控制逻辑复杂,而且在写回时消耗的拍数比较

2019-03-03 17:51:01

怎么利用异步FIFO和PLL结构来实现高速缓存?

结合高速嵌入式数据采集系统,提出一种基于CvcloneⅢ FPGA实现的异步FIFO和锁相环(PLL)结构来实现高速缓存,该结构可成倍提高数据流通速率,增加数据采集系统的实时性。采用FPGA设计高速缓存,能针对外部硬件系统的改变,通过修改片内程序以应用于不同的硬件环境。

2021-04-30 06:19:52

求助verilog编写实现AXIStream-FIFO功能思路

),要用verilog实现AXI Stream的异步FIFO1、读写不同的时钟,设一个100M,另一个333M2、读写不同的位宽,设写为8bit,读为32bit3、fifo深度为324、控制信号没有

2014-02-21 16:24:45

用两块同步FIFO实现一个异步FIFO功能

也就是说用一个25M频率的FIFO写入数据,用另一个100M(或者不同频)的FIFO读出数据。该如何实现呢?不使用异步FIFO

2020-12-03 20:47:22

详细讨论异步FIFO的具体实现???

我在网上看到一篇利用格雷码来设计异步FIFO,但是看他们写的一些源码,小弟有些不是很理解,在设计时为什么会出现Waddr和wptr两个关于写指针的问题,他们之间的关系是什么????wptr在定义时候为什么比Waddr多一位呀???

2017-05-19 11:04:13

请问一下异步FIFO的VHDL实现方法

本文讨论了在ASIC设计中数据在不同时钟之间传递数据所产生的亚稳态问题,并提出了一种新的异步FIFO的设计方法,并用VHDL语言进行描述,利用Altera公司的Cyclone系列的EP1C6进行硬件实现,该电路软件仿真和硬件实现已经通过验证,并应用到各种电路中。

2021-04-29 06:54:00

异步FIFO结构及FPGA设计

首先介绍异步FIFO 的概念、应用及其结构,然后分析实现异步FIFO的难点问题及其解决办法; 在传统设计的基础上提出一种新颖的电路结构并对其进行综合仿真和FPGA 实现。

2009-04-16 09:25:29 46

46

46

46高速异步FIFO的设计与实现

本文主要研究了用FPGA 芯片内部的EBRSRAM 来实现异步FIFO 设计方案,重点阐述了异步FIFO 的标志信号——空/满状态的设计思路,并且用VHDL 语言实现,最后进行了仿真验证。

2010-01-13 17:11:58 40

40

40

40Camera Link接口的异步FIFO设计与实现

介绍了异步FIFO在Camera Link接口中的应用,将Camera Link接口中的帧有效信号FVAL和行有效信号LVAL引入到异步FIFO的设计中。分析了FPGA中设计异步FIFO的难点,解决了异步FIFO设计中存在的两

2010-07-28 16:08:06 32

32

32

32一种异步FIFO的设计方法

摘要:使用FIFO同步源自不同时钟域的数据是在数字IC设计中经常使用的方法,设计功能正确的FUFO会遇到很多问题,探讨了两种不同的异步FIFO的设计思路。两种思路

2006-03-24 12:58:33 680

680

680

680

异步FIFO结构及FPGA设计

摘要:首先介绍异步FIFO的概念、应用及其结构,然后分析实现异步FIFO的难点问题及其解决办法;在传统设计的基础上提出一种新颖的电路结构并对其进行

2009-06-20 12:46:50 3667

3667

3667

3667

高速异步FIFO的设计与实现

高速异步FIFO的设计与实现

引言

现代集成电路芯片中,随着设计规模的不断扩大.一个系统中往往含有数个时钟。多时钟带来的一个问题就是,如何设

2010-04-12 15:13:08 2790

2790

2790

2790

异步时序亚稳态的消除方法设计

提出一种基于异步比较法产生空满标志位,并利用锁存器实现标志位与时钟同步的 FIFO ,同时还给出了相应的VerilogHDL代码。该方法能提高时钟频率,节约版图面积。

2011-05-31 15:15:24 24

24

24

24异步FIFO在FPGA与DSP通信中的运用

文中给出了异步FIFO的实现代码和FPGA与DSP的硬件连接电路。经验证,利用异步FIFO的方法,在FPGA与DSP通信中的应用,具有传输速度快、稳定可靠、实现方便的优点。

2011-12-12 14:28:22 51

51

51

51基于FIFO实现DSP间的双向并行异步通讯的方法

介绍了利用CYPRESS公司的FIFO芯片CY7C419实现DSP间双向并行异步通讯的方法,该方法简单实用,速度快,特别适用于小数据量的数据相互传送。文中给出了CY7C419的引脚功能以及用FIFO

2017-10-25 11:35:25 0

0

0

0异步FIFO在FPGA与DSP通信中的应用解析

摘要 利用异步FIFO实现FPGA与DSP进行数据通信的方案。FPGA在写时钟的控制下将数据写入FIFO,再与DSP进行握手后,DSP通过EMIFA接口将数据读入。文中给出了异步FIFO的实现代码

2017-10-30 11:48:44 1

1

1

1采用异步FIFO的载波控制字和伪码控制字的方法

传输时发生数据丢失问题得目的,提出采用异步FIFO来缓存大量导航电文数据还有同步器来同步所传输的载波控制字和伪码控制字的方法。通过采用Altera公司的FIFO内核来进行外围接口信号和控制逻辑设计以及两级触发器级联来实现同步器的试验设计方法,得到所设计的缓存

2017-11-06 16:35:27 10

10

10

10异步FIFO的设计分析及详细代码

本文首先对异步 FIFO 设计的重点难点进行分析,最后给出详细代码。 一、FIFO简单讲解 FIFO的本质是RAM, 先进先出 重要参数:fifo深度(简单来说就是需要存多少个数据) fifo

2017-11-15 12:52:41 7993

7993

7993

7993

基于FPGA的异步FIFO设计方法详解

在现代电路设计中,一个系统往往包含了多个时钟,如何在异步时钟间传递数据成为一个很重要的问题,而使用异步FIFO可以有效地解决这个问题。异步FIFO是一种在电子系统中得到广泛应用的器件,文中介绍了一种基于FPGA的异步FIFO设计方法。使用这种方法可以设计出高速、高可靠的异步FIFO。

2018-07-17 08:33:00 7873

7873

7873

7873

基于异步FIFO结构原理

在现代的集成电路芯片中,随着设计规模的不断扩大,一个系统中往往含有数个时钟。多时钟域带来的一个问题就是,如何设计异步时钟之间的接口电路。异步FIFO(Firstln F irsto ut)是解决这个

2018-02-07 14:22:54 0

0

0

0关于一种面向异步FIFO的低开销容错机制研究

异步FIFO(Fist-In-First-Out)是一种先入先出的数据缓冲器[1]。由于可以很好地解决跨时钟域问题和不同模块之间的速度匹配问题,而被广泛应用于全局异步局部同步[2](Globally

2018-06-19 15:34:00 2870

2870

2870

2870

在ASIC中采用VHDL语言实现异步FIFO的设计

异步FIFO广泛应用于计算机网络工业中进行异步数据传送,这里的异步是指发送用一种速率而接收用另一速率,因此异步FIFO有两个不同的时钟,一个为读同步时钟,一个为写同步时钟。

2019-06-11 08:00:00 2788

2788

2788

2788

利用VHDL语言和格雷码对地址进行编码的异步FIFO的设计

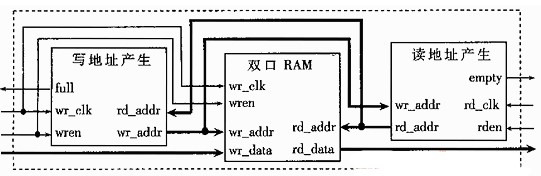

FIFO (先进先出队列)是一种在电子系统得到广泛应用的器件,通常用于数据的缓存和用于容纳异步信号的频率或相位的差异。FIFO的实现通常是利用双口RAM和读写地址产生模块来实现的。FIFO的接口

2019-08-02 08:10:00 1855

1855

1855

1855

FPGA之FIFO练习3:设计思路

根据FIFO工作的时钟域,可以将FIFO分为同步FIFO和异步FIFO。同步FIFO是指读时钟和写时钟为同一个时钟。在时钟沿来临时同时发生读写操作。异步FIFO是指读写时钟不一致,读写时钟是互相独立的。

2019-11-29 07:08:00 1609

1609

1609

1609基于各类二进制代码实现异步FIFO的设计

使相异时钟域数据传输的时序要求变得宽松,也提高了它们之间的传输效率。此文内容就是阐述异步FIFO的设计。 二、设计原理 2.1结构框图 Fig. 2.1.1 如上图所示的同步模块synchronize to write clk,其作用是把读时钟域的读指针rd_ptr采集到写时钟(wr_clk)域,然

2020-07-17 09:38:20 478

478

478

478

基于XC3S400PQ208 FPGA芯片实现异步FIFO模块的设计

问题的有效方法。异步FIFO是一种在电子系统中得到广泛应用的器件,多数情况下它都是以一个独立芯片的方式在系统中应用。本文介绍一种充分利用FPGA内部的RAM资源,在FPGA内部实现异步FIFO模块的设计方法。这种异步FIFO比外部 FIFO 芯片更能提高系统的稳定性。

2020-07-21 17:09:36 1326

1326

1326

1326

如何使用FPGA实现异步FIFO硬件

。本文提出了一种用Xilinx公司的FPGA芯片实现异步HFO的设计方案,重点强调了设计有效、可靠的握手信号EMPTY与FULL的方法,并给出了其VERILOG语言实现的仿真图。

2021-01-15 15:27:00 9

9

9

9如何使用FPGA实现节能型可升级异步FIFO

提出了一种节能并可升级的异步FIFO的FPGA实现。此系统结构利用FPGA内自身的资源控制时钟的暂停与恢复,实现了高能效、高工作频率的数据传输。该系统在Xilinx的VC4VSX55芯片中实现,实际

2021-02-02 15:15:00 16

16

16

16Xilinx异步FIFO的大坑

FIFO是FPGA处理跨时钟和数据缓存的必要IP,可以这么说,只要是任意一个成熟的FPGA涉及,一定会涉及到FIFO。但是我在使用异步FIFO的时候,碰见几个大坑,这里总结如下,避免后来者入坑。

2021-03-12 06:01:34 12

12

12

12详解同步FIFO和异步FIFO

1.定义 FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,他与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序

2021-04-09 17:31:42 4697

4697

4697

4697

异步FIFO用格雷码的原因有哪些

异步FIFO通过比较读写地址进行满空判断,但是读写地址属于不同的时钟域,所以在比较之前需要先将读写地址进行同步处理,将写地址同步到读时钟域再和读地址比较进行FIFO空状态判断(同步后的写地址一定

2021-08-04 14:05:21 3794

3794

3794

3794异步bus交互(三)—FIFO

跨时钟域处理 & 亚稳态处理&异步FIFO1.FIFO概述FIFO: 一、先入先出队列(First Input First Output,FIFO)这是一种传统的按序执行方法,先进

2021-12-17 18:29:31 10

10

10

10【FPGA】异步复位,同步释放的理解

异步复位,同步释放的理解目录目录 同步复位和异步复位 异步复位 同步复位 那么同步复位和异步复位到底孰优孰劣呢? 异步复位、同步释放 问题1 问题2 问题3 问题4 问题5 参考资料同步

2022-01-17 12:53:57 4

4

4

4异步FIFO设计原理及应用需要分析

在大规模ASIC或FPGA设计中,多时钟系统往往是不可避免的,这样就产生了不同时钟域数据传输的问题,其中一个比较好的解决方案就是使用异步FIFO来作不同时钟域数据传输的缓冲区,这样既可以使相异时钟域数据传输的时序要求变得宽松,也提高了它们之间的传输效率。此文内容就是阐述异步FIFO的设计。

2022-03-09 16:29:18 2309

2309

2309

2309同步FIFO之Verilog实现

FIFO的分类根均FIFO工作的时钟域,可以将FIFO分为同步FIFO和异步FIFO。同步FIFO是指读时钟和写时钟为同一个时钟。在时钟沿来临时同时发生读写操作。异步FIFO是指读写时钟不一致,读写时钟是互相独立的。

2022-11-01 09:57:08 1315

1315

1315

1315异步FIFO之Verilog代码实现案例

同步FIFO的意思是说FIFO的读写时钟是同一个时钟,不同于异步FIFO,异步FIFO的读写时钟是完全异步的。同步FIFO的对外接口包括时钟,清零,读请求,写请求,数据输入总线,数据输出总线,空以及满信号。

2022-11-01 09:58:16 1189

1189

1189

1189异步fifo详解

和写入数据(对于大型数据存储,在性能上必然缓慢),其数据地址是由内部读写指针自动加一完成的,不能像普通的存储器一样,由地址线决定读取或者写入某个特定地址的数据,按读写是否为相同时钟域分为同步和异步FIFO,这里主要介绍异步FIFO,主要用于跨时钟域传输数据。 FIFO是

2022-12-12 14:17:41 2790

2790

2790

2790Verilog电路设计之单bit跨时钟域同步和异步FIFO

FIFO用于为匹配读写速度而设置的数据缓冲buffer,当读写时钟异步时,就是异步FIFO。多bit的数据信号,并不是直接从写时钟域同步到读时钟域的。

2023-01-01 16:48:00 941

941

941

941FPGA同步转换FPGA对输入信号的处理

参考博主的verilog异步fifo设计,仿真(代码供参考)异步fifo适合处理不同时钟域之间传输的数据组,但有时不同时钟域之间仅仅传递脉冲,异步fifo就显的有点大材小用的,因此单信号的跨时钟域处理通常有, 两级寄存器串联。 脉冲同步器。

2023-02-17 11:10:08 484

484

484

484如何在同步的Rust方法中调用异步代码呢?

在同步的 Rust 方法中调用异步代码经常会导致一些问题,特别是对于不熟悉异步 Rust runtime 底层原理的初学者。

2023-03-17 09:18:00 1413

1413

1413

1413FIFO使用及其各条件仿真介绍

FIFO(First In First Out )先入先出存储器,在FPG设计中常用于跨时钟域的处理,FIFO可简单分为同步FIFO和异步FIFO。

2023-04-25 15:55:28 2893

2893

2893

2893

FIFO设计—同步FIFO

FIFO是异步数据传输时常用的存储器,多bit数据异步传输时,无论是从快时钟域到慢时钟域,还是从慢时钟域到快时钟域,都可以使用FIFO处理。

2023-05-26 16:12:49 978

978

978

978

基于寄存器的同步FIFO

FIFO,可以直接在自己的设计中配置和使用它,该设计是完全可综合的。 为什么要自己设计FIFO 那么,为什么呢?网上有很多关于 FIFO 的 Verilog/VHDL 代码的资源,过去,我自己也使用过其中的一些。但令人沮丧的是,它们中的大多数都存在问题,尤其是在上溢出和下溢出

2023-06-14 09:02:19 461

461

461

461采用格雷码异步FIFO跟标准FIFO有什么区别

异步FIFO包含"读"和"写“两个部分,写操作和读操作在不同的时钟域中执行,这意味着Write_Clk和Read_Clk的频率和相位可以完全独立。异步FIFO

2023-09-14 11:21:45 545

545

545

545

为什么异步fifo中读地址同步在写时钟域时序分析不通过?

为什么异步fifo中读地址同步在写时钟域时序分析不通过? 异步FIFO中读地址同步在写时钟域时序分析不通过的原因可能有以下几个方面: 1. 读地址同步在写时钟域时序分析未覆盖完全 在时序分析时,可能

2023-10-18 15:23:55 312

312

312

312同步FIFO和异步FIFO的区别 同步FIFO和异步FIFO各在什么情况下应用

简单的一种,其特点是输入和输出都与时钟信号同步,当时钟到来时,数据总是处于稳定状态,因此容易实现数据的传输和存储。 而异步FIFO则是在波形的上升沿和下降沿上进行处理,在输入输出端口处分别增加输入和输出指针,用于管理数据的读写。异步FIFO的输入和输出可同时进行,中间可以

2023-10-18 15:23:58 790

790

790

790请问异步FIFO的溢出操作时怎么样判断的?

请问异步FIFO的溢出操作时怎么样判断的? 异步FIFO是数据传输的一种常用方式,在一些储存器和计算机系统中,常常会用到异步FIFO。作为一种FIFO,异步FIFO经常面临两种情况:溢出

2023-10-18 15:28:41 299

299

299

299如何在同步的 Rust 方法中调用异步代码 | Tokio 使用中的几点教训

在同步的 Rust 方法中调用异步代码经常会导致一些问题,特别是对于不熟悉异步 Rust runtime 底层原理的初学者。

2023-12-24 16:23:29 415

415

415

415verilog同步和异步的区别 verilog阻塞赋值和非阻塞赋值的区别

Verilog中同步和异步的区别,以及阻塞赋值和非阻塞赋值的区别。 一、Verilog中同步和异步的区别 同步传输和异步传输是指数据在电路中传输的两种方式,它们之间的区别在于数据传输的时间控制方式。 同步传输:同步传输是通过时钟信号来控制数据传输的方式。

2024-02-22 15:33:04 202

202

202

202 电子发烧友App

电子发烧友App

评论