逻辑单元在FPGA器件内部,用于完成用户逻辑的最小单元。

2023-10-31 11:12:12 541

541

脍炙人口的诗"春有百花秋有月,夏有凉风冬有雪",意境唯美,简明易懂。好的代码也是让人陶醉的,那么如何写出好的代码?

2024-01-05 11:29:08 564

564

矩阵扫描键盘已经写完了,单个按键按下没问题,如何写两个、多个按键同时按下的程序

2019-10-17 19:51:55

''}; while(TT4_AddAAR(& aAAR)!= SUCCESS); 是否有任何smaple代码来测试AAR读/写。还有各种NDEF格式?提前致谢!RGDS,卢比#android-app #nfc#m24sr

2019-08-16 14:24:07

解如何写DA转化代码:s: 即startADDRESS: 即器件地址(0表示为写)A:表示等待回应CONTROL BYTE: 表示控制字(第二个发送的字节)A:表示等待回应DATE BYTE: 表示写入的电压值(注意如果写入255,其实结果是5v,以此来换算)A:表示等待回应s:

2022-02-16 07:48:44

adxl345如何写单双击中断程序,我写了一个无法进入中断,求教!

2019-09-19 00:44:45

怎样写c代码才能让程序的执行效率更高?同样结构和功能的代码,只是其中的变量的定义方式不同,但程序的执行效率却又天壤之别!能相差10倍!!!所以,想问问怎样写代码,可以让代码的执行效率更高?

2020-07-14 08:00:20

如何写一个Qt版本的Helloworld程序?

2014-05-05 11:07:39

目录1、中断2、复位3、通用I/O及其中断:I/O寄存器I/O中断寄存器默认状态如何写一个中断函数总结所整理归纳仅做分享与记录,从自身角度分析自己身为学生曾在学习中所遇到的问题与需要特别注意的地方

2021-11-29 07:30:15

如何写一个简单的字符设备驱动程序?

2021-12-23 06:26:28

如何写一个简易的printf函数?

2021-04-28 06:47:25

连接是没有问题的。但是我写入*AC? 时仪器报错。我看了说明还是不会如何写?所以请教1.若我要测量市电220vac要怎样写指令,仪器才可以响应测量AC的指令呢?2.附件有34401A的说明书,能否对几个典型的命令做详细的说明。3.请教一下,有没有相关如何写入指令的教程或书籍介绍。

2014-04-30 12:58:03

如何写出可以让人理解的代码(以verilog语言为例)?1. 代码要比较好理解,最容易做到的就是把代码写短,因此在每个always语句块尽可能只处理一个信号,或者只处理一组相关度很高的信号(例如

2012-02-01 11:39:56

按照这样写,可以写出非常高效的代码

2014-01-21 09:47:34

的硬件和逻辑工程师面试中,状态机设计几乎是必选题目。本章在引入状态机设计思 想的基础上,重点讨论如何写好状态机。 本文主要内容如下: 状态机的基本概念; 如何写好状态机; 使用 Synplify Pro 分析 FSM。[hide] [/hide]

2011-10-24 11:43:11

字节而不是128字节。有时也丢失了字节。在PSoC Creator好的例子中,没有使用大缓冲区的UART。请你帮助我,告诉你如何写这个函数。AuthyScB.Cyrkk.Access 02.Zip1.1兆字节

2019-10-14 10:32:36

这个章节包含了定义逻辑单元 (LE) 和逻辑阵列模块 (LAB) 的特性。具体信息体现在 LE如何运作,LAB 如何容纳 LE 组,以及 LAB 接口如何与 Cyclone® IV 器件中的其他模块连接。

2017-11-13 11:25:48

大家好:DSP C6713用McBSP0中的中断程序向FPGA发数据,或者向CE0写数据,(注意:发送数据用EMIF,接收用McBSP0)C语言代码该如何写?紧急多谢!

2020-07-29 09:29:38

减少关键路径的逻辑等级本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 下面要列举的代码示例是一些能够起到

2015-07-02 22:17:18

FreeRTOS中如何写硬件中断程序啊?比如说按键中断,怎么写?能给个具体的例子分析么??感激不尽

2020-07-31 08:00:35

STC90C58AD自带AD程序如何写?1、初始化哪些指令?2、如何设置?3、如何采集及送到LCD屏16284希望高手都来指点下!

2013-01-07 11:14:09

TIVA Cortex——M4如何写代码,如何用库函数?

2015-07-21 10:24:19

TL16C754B 这款芯片如何写Test Plan

2022-09-05 15:59:57

我有一个当前的项目,目录中列出的USET模块的数量突然减少到只有两个。有什么想法吗? 以上来自于百度翻译 以下为原文I have a current project and suddenly

2019-03-21 09:26:00

reg52.h的重复定义。这是我第一次尝试写模块化程序,不知道各个.h文件和.c文件开头怎么写,我是参照一个模板写的,但编译还是出错,请各位大侠指出错误,教小弟如何写模块化程序。能不能把我的程序改一下传给我,或者您给我传一份可以正确编译的模块化程序,让我参考参考,在此谢谢过了!

2013-01-01 19:17:58

reg52.h的重复定义。这是我第一次尝试写模块化程序,不知道各个.h文件和.c文件开头怎么写,我是参照一个模板写的,但编译还是出错,请各位大侠指出错误,教小弟如何写模块化程序。能不能把我的程序改一下传给我,或者您给我传一份可以正确编译的模块化程序,让我参考参考,在此谢谢过了!

2013-01-01 19:20:53

reg52.h的重复定义。这是我第一次尝试写模块化程序,不知道各个.h文件和.c文件开头怎么写,我是参照一个模板写的,但编译还是出错,请各位大侠指出错误,教小弟如何写模块化程序。能不能把我的程序改一下传给我,或者您给我传一份可以正确编译的模块化程序,让我参考参考,在此谢谢过了!

2013-01-01 20:13:36

reg52.h的重复定义。这是我第一次尝试写模块化程序,不知道各个.h文件和.c文件开头怎么写,我是参照一个模板写的,但编译还是出错,请各位大侠指出错误,教小弟如何写模块化程序。能不能把我的程序改一下传给我,或者您给我传一份可以正确编译的模块化程序,让我参考参考,在此谢谢过了!

2013-01-01 20:15:05

am335x裸跑时从nandflash启动的boot如何写,是否有参考的例程

2018-06-04 12:24:27

;"小于"这样的判断语句, 这样会明显增加使用的逻辑单元数量 .看一下报告,资源使用差别很大.例程:always@(posedge clk)begincount1=count1+1

2018-03-24 11:04:41

``msp430g2553开发板在没有外部晶振的情况下,如何写定时一秒的程序??想用12864做个电子钟,但不能准确定时一秒,希望大家帮帮忙``

2014-05-01 19:49:13

omap L138自带的看门狗驱动如何写,哪有这方面的资料,谢谢!

2018-06-21 08:06:18

ubuntu linux操作系统上如何写一个让图随机移动的程序,打印出来?

2014-04-18 16:03:13

`FPGA的逻辑单元_CLB_项目代码文件`

2021-03-31 11:18:02

本人新手,问一个问题。什么控制逻辑单元接受PWM后能产生几个频率稳定的逻辑脉冲?

2012-07-24 08:59:48

什么是Modbus协议?Modbus协议有哪些分类?使用Modbus时有哪些注意事项?如何写稳定的Modbus代码?

2021-07-02 06:54:34

TAS-MRAM概念从磁性随机存取存储器到磁性逻辑单元

2021-03-03 06:10:33

架构漫谈(八):从架构的角度看如何写好代码 + 我的思考

2020-06-18 06:16:04

定义。这是我第一次尝试写模块化程序,不知道各个.h文件和.c文件开头怎么写,我是参照一个模板写的,但编译还是出错,请各位大侠指出错误,教小弟如何写模块化程序,不胜感激!!!

2012-12-30 15:51:55

单片机如何写一段宏来控制外部存储器的访问?

2021-10-29 06:24:53

本帖最后由 人间烟火123 于 2018-6-15 11:45 编辑

请教下专家们我用的IPNC rdk 4.1编写了一个自己的驱动,我想把它单独编译成一个ko文件,如何写make?

2018-06-15 01:16:41

1.在Virtex5LX中,有多少门数等于1Logic ce。2.如何从逻辑单元计算Gatecounts。

2020-05-28 06:08:44

嗨,我目前正在对设计进行初步分析。我正在研究关于实现不同功能所需资源的不同FPGA。我找不到一种方法来将设计使用的LUT数量相关联,并将其转换为virtex和spartan范围的逻辑单元格。如果可能

2019-01-08 10:18:36

我想通过按键实现复位,能不能提示下怎么写外部复位逻辑啊?

2015-01-20 21:37:58

我在以前的代码基础上,又加入部分的代码。加入的部分代码只是为了增加部分的新功能(原来的代码没有改动),编辑后逻辑单元使用量竟然比原代码的使用量减少了,求告知使用语言: verilog环境: quartusii芯片: CPLDAltera

2016-08-13 09:40:24

数字逻辑功能单元数字逻辑最终是需要通过数字电路的形式来实现的缓冲门:是仅具有缓冲功能的基本门电路,仅有一个输入端口,也仅有一个输出端口功能:将输入端口的信号电平原封不动地搬移到输出端口,输入为0

2021-07-29 08:04:47

我想知道我是否可以使用逻辑单元(Spartan 6)的verilog代码,这样我就不必花时间为逻辑单元编写verilog代码。这可以节省我的时间,让我专注于其他部分内容,因为我有一个很短的时间来完成

2020-03-10 09:45:39

求助。ssrp主板。如何写程序。有赏服务。我有一个维基站,在国内可以用。拿到加拿大,频率不一样,需要更新程序。有会的大牛吗。有赏服务。***微信同号。

2021-08-19 08:19:19

23 DBCD 11)发送给MCU。比如,原命令是16位hex命令包,转码完后会变成18位的命令包,这样的情况,用labview如何写呢?有个大体思路,是先拆分数据,然后一位一位比较,若遇到特殊数据就转码,最后把这些比较完的数据再合成。用for循环,实在是写不出来,请大神帮想想法子。

2019-08-29 23:25:15

本文不说底层原理,只说蓝桥杯中模块相应代码该如何写,一定要自己敲出来,测试出相应的结果。模块练熟了再去敲往年的赛题,毕竟九尺之台,起于累土main主函数部分,这个把各个模块融合在一起,可以最后再看

2022-01-12 07:06:30

,解析一下普通的Io按键驱动如何写和实现,如果有大神看出有错误的东西,请指教。此篇作为学习和交流之用。谢谢大家。 首先普通的io 口按键来说的话,主要分为两种情况,一种是低推...

2021-12-10 08:13:03

我在获取最大逻辑单元时返回了01, 按理说应该有两个盘符啊,怎么只有一个呢,奇怪。枚举都成功了有大侠帮忙指点指点,谢了!如图所示: 2013-3-25 17:30 上传下载附件 (907.61 KB) 逻辑单元返回值为1

2013-03-26 16:18:21

请教一下各位:在TL2515_CAN例程中,CAN接收采用查询方式,能不能提示一下CAN中断接收的初始化、接收部分代码如何写?

2020-05-20 07:17:30

, pTxData, APP_PAYLOAD_LENGTH)的RECEIVE_ADDR 可以决定哪一个接收端但如果是多对1 要如何写,因为在1对1裡 接收端的程式好像没有

2018-06-01 02:04:55

社区送的ESP8266开发板如何写程序?是像stm32那样用Keil编程么?

2023-10-31 06:53:29

labview如何写一个心形动态曲线图,求源代码,抖音见别人用MATLAB实现过

2020-05-18 01:11:22

项目需要用同一个定时器的两个输入捕获通道,现在分配的是TIM1 的CH3 和CH4,芯片为 STM32F103C8T6,用CUBEMX生成的代码,现在不知如何写捕获的中断回调函数。有谁能给个基于HAL的例子吗?万分感谢!

2018-11-19 08:46:05

嗨,我的设计在合成中使用141.5 BRAM瓦片。但是,在Zynq中可以使用140 BRAM瓦片。实施后,这个数量下降到133瓦。我的问题是vivado如何减少这一数量?实施?这点可以导致未来

2018-10-31 16:17:40

我想知道“逻辑单元”的意思..我知道“Block RAM”,“分布式RAM”“CLB”......以及ETC ..但是,我不知道“Logic Cell”..请让我知道..谢谢!

2019-11-08 16:38:38

请问有什么方法可以减少PIN脚数量?

2021-06-22 08:15:34

嗨朋友们, 我想知道在Virtex 5 LX110中有多少门数等于1个逻辑单元?此外,从逻辑单元计算栅极数量的公式也是必须的。请尽快发给我。还要把附件文件和我的问题的答案一起发给我。再见,MUTHU

2020-05-28 17:18:52

请问谁有如何写test bench的资料么,麻烦发一份 谢谢

2015-11-02 21:20:07

用的ads1231, 其测量正电压值范围0-0.5VREF/128,我取参考电压2.5V这样电压值voltage=AD_DATA*0.009765625/83886077fffff=8388607这个在c 语言里面该如何写啊??这样子写恐怕是不好处理的啊

2019-06-12 08:18:13

如何写好状态机:状态机是逻辑设计的重要内容,状态机的设计水平直接反应工程师的逻辑功底,所以许多公司的硬件和逻辑工程师面试中,状态机设计几乎是必选题目。本章在引入

2009-06-14 19:24:49 96

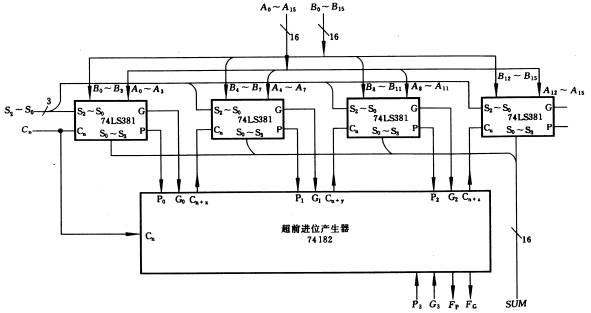

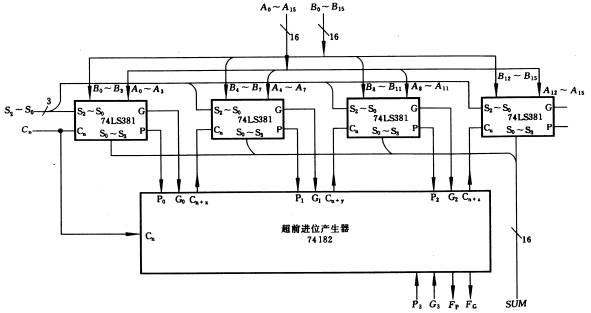

96 集成算术/逻辑单元举例

集成算术/逻辑单元(ALU)能够完成一系列的算术运算和逻辑运算。74LS381

2009-04-07 10:39:27 1255

1255

如何写好SCI论文,真的经典啊啊啊啊啊啊

2016-05-13 15:39:49 2

2 电子专业单片机相关知识学习教材资料之Cyclone_IV器件的逻辑单元

2016-09-02 16:54:40 0

0 尽量不要使用"大于""小于"这样的判断语句, 这样会明显增加使用的逻辑单元数量 .看一下报告,资源使用差别很大.

2017-02-11 11:31:11 941

941 内容提要: 本章系统地介绍数字电路的基本逻辑单元门电路,及其对应的逻辑运算与图形描述符号,并针对实际应用介绍了三态逻辑门和集电极开路输出门,最后简要介绍TTL集成门和CMOS集成门的逻辑功能、外特性

2017-10-26 17:27:59 9

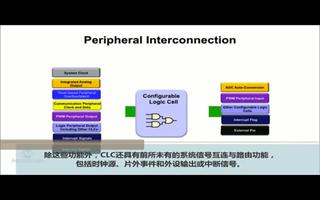

9 本视频介绍了可配置逻辑单元(CLC),该灵活外设可用于整合片上和片外逻辑信号,用来产生不同的输出值,可以在多种条件下将器件从低功耗休眠模式唤醒。嵌入式设计人员还可以利用时序逻辑特性开发简单的状态机,而无需CPU干预。此外,CLC还具有系统信号互连与路由功能,包括时钟源、片外事件和外设输出或中断信号。

2018-06-07 02:46:00 4224

4224

在这篇文章中将介绍如何写一个简短(200行)的 Python 脚本,来自动地将一幅图片的脸替换为另一幅图片的脸。

2018-07-09 10:48:47 4198

4198 CLB是xilinx基本逻辑单元,每个CLB包含两个slices,每个slices由4个(A,B,C,D)6输入LUT和8个寄存器组成。

2022-04-24 14:48:55 3407

3407 逻辑单元(Logic Element,LE)在FPGA器件内部,用于完成用户逻辑的最小单元。一个逻辑阵列包含16个逻辑单元以及一些其他资源, 在一个逻辑阵列内部的16个逻辑单元有更为紧密的联系,可以实现特有的功能。

2022-06-15 16:50:21 2604

2604 电子发烧友网站提供《如何写出高效优美的C语言代码.pdf》资料免费下载

2023-11-18 10:55:13 0

0

正在加载...

电子发烧友App

电子发烧友App

评论