【Number of Input Trigger Ports】下拉列表框:选择ILA核输入触发端口数目,ILA核最多支持16个输入触发端口。每个触发端口的参数在下方列出,包括触发宽度、触发匹配条件判断类型和数目。

TRIGn选项组:

【Trigger Width】编辑框:触发端口由一条或者多条信号线组成,信号线的总数成为触发宽度,最大为256。

【# Match Unit】下拉列表框:触发比较匹配单元是个比较器,和触发端口相连,用于检测触发端口是否满足设定的条件。每个触发端口可以有1~16个触发匹配单元。触发匹配设置单元设置的越多,触发事件就越灵活,但是要占用更多的内部资源。在满足条件的情况下,尽量减少触发匹配单元的数量。

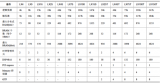

【MatchType】下拉列表框:请参见表9-1。

【Count Width】下拉列表框:匹配单元计数器宽度,用于选择满足匹配条件的次数,最大32位。

Trigger Condition Settings选项组

【Enable trigger condition sequencer】复选框:设臵是否使能触发队列器和队列器深度。触发序列是为了增加触发的复杂性,使触发的条件更加特殊,我们可以把若干个状态组合起来形成触发条件,这样就能更好的使用有限的资源存储有用的数据。

【Max Number of Sequencer levels】下拉列表框:设臵最大的触发条件序列级数。

Storage qualification condition Settings选项组

【Enable Storage Qualification】复选框:存储器限制条件。请参考9.2.2小节中的相关内容。

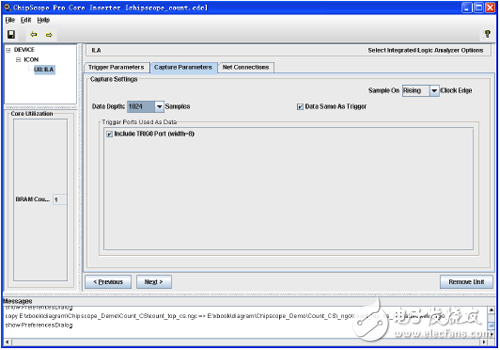

Captures Parameters选项卡:采样参数选项卡(参见图9-33)。

图9-33 【Captures Parameters】参数设置界面

【Sample On】下拉选择框:设臵在时钟的上升沿或者下降沿采集数据。

【Data Depth】下拉选择框:设臵ILA核存储的最大数据采样个数。

【Data Same as Trigger】复选框:设臵ILA触发端口和数据采集端口是否相同。请参考9.2.2小节中的相关内容。

Trigger Port Used As Data选项组:

如果选中了【Data Same As Trigger】复选框,那么在数据选项的每个TRIGn端口前都会出现一个【Include TRIGn Port】复选框,选中该选项,表明数据和触发端口合并。

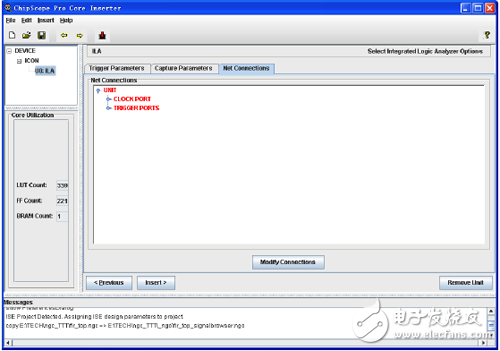

Net connections选项卡(参见图9-34)。

图9-34 【Net connections】网络连接界面

Net Connections选项组:用于将集成逻辑分析仪ILA核的输入信号与设计中的网线连接起来。如果触发和数据信号分离,那么必须指定数据、时钟和触发端口。双击【CLOCK PORT】或者单击【CLOCK PORT】左边的加号(+)。如果还没连接,该选项显示为红色。如图9-34所示,包括【CLOCK PORT】和【TRIGGER PORTS】两组端口的连接。

【Modify Connections】按钮:单击该按钮弹出【Select Net】对话框,对话框很容易地将ILA核工作时钟、触发信号、数据信号与设计中的网线连接起来,如图9-35所示。

【Structure/Nets】窗格:列出设计的层次结构。

【Net Name】:EDIF网表中的网络名,由于重命名或者综合中的优化原因,可能和HDL中的源码名字不一样。

【Source Instance】:当前综合结果中较低层次的元件例化名称。

【Source Component】:【Source Instance】选项中描述的组件。

【Base Type】:最底层的组件类型,基本类型为原语(primitive)或黑盒子。

【Pattern】编辑框和【Filter】按钮:通过这两个选项,可以有选择地显示设计中可用于ChipScope的网线。

【Remove Connections】按钮:删除当前的连接。

【Move Nets Up】按钮:向上移动连接的位臵。

【Move Nets Down】按钮:向下移动连接的位臵。

【Make Connections】按钮:连接所选择的网络节点和ChipScope内核。

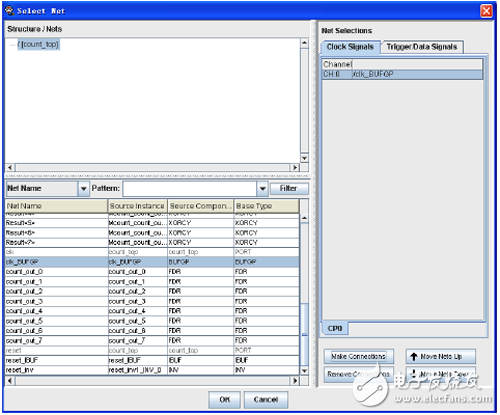

图9-35 【Select Net】界面

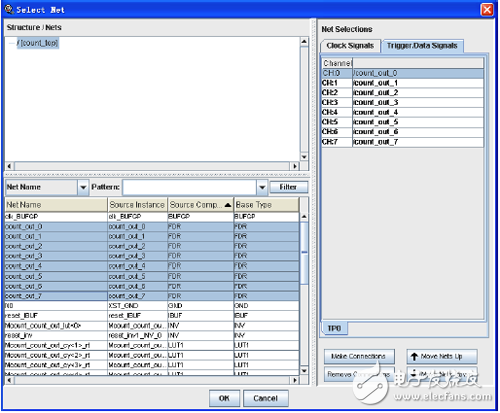

在【Structure/Nets】中,选择想要连接到ChipScope核的网络节点(可以配合Shift/Ctrl键,选择多个网线)。在【Net Selections】中选择【Clock Signals】、【Trigger Signals】或【Data Signals】选项卡,选择想用于连接网络节点的通道,例如CH0,单击【Make Connections】按钮建立网络节点与ChipScope内核的连接,如图9-36所示。

图9-36 【Select Net】界面

ChipScope Pro只能分析FPGA内部逻辑信号,不能直接连接到FPGA的输入,所以输入信号全部以灰色显示,如图9-35所示的clk、reset信号。如果要观察输入信号,可连接此输入信号的输入缓冲器的输出来实现,时钟信号选择相应的BUFGP,如图9-36所示的clk_BUFGP信号,普通信号选择相应的IBUF。

连接完成后,单击“OK”按钮返回连接显示界面,发现所有提示字符“UNIT”、【CLOCK PORT】以及【TRIGGER PORTS】没有红色,则单击【Return Project Navigator】,退出Chipscope,返回到ISE 中。

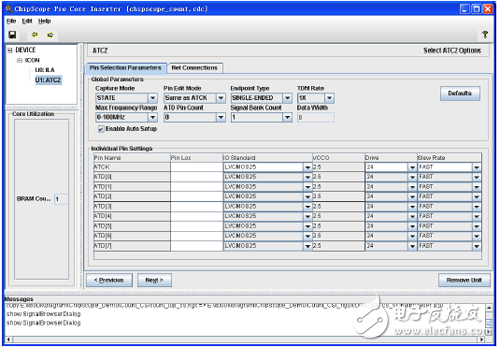

(4) 在图9-30中单击【New ATC2 Unit】,弹出ATC2的选项和参数设置界面,如图9-37所示。

图9-37 ATC2【Pin Selection Parameters】参数设置界面

Pin Selection Parameters选项卡。

【Capture Mode】下拉选择框:可以设臵成STATE模式和Timing模式,STATE模式用于和CLK输入信号同步的数据捕获。数据信号经ATC核输出到FPGA引脚上的通道由流水线触发器和CLK组成。Timing模式用于异步数据捕获。数据信号经ATC核输出到FPGA引脚上的通道由组合逻辑组成。

【Max Frequency Range】下拉列表框:ATC2核的最大频率范围。有效的最大频率选项为0~100 MHz、101~200 MHz、201~300 MHz和301~500 MHz。当【Capture Mode】设臵成【State】,【Max Frequency Range】的选择对ATC2核实现有效。

【Pin Edit Mode】下拉列表框:引脚编辑模式,用于设臵引脚是否为一组,如果设臵成【Same as ATCK】一组,那么所有ATD的IO标准、驱动、Slew斜率都和ATCK相同。设臵成【Individual】,则要设臵每个引脚的属性。

【ATD Pin Count】下拉列表框:ATD输出引脚数,范围为4~128。

【Endpoint Type】下拉列表框:ATCK和ATD输出驱动类型为单端或者差分。

【Signal Bank Count】下拉列表框:ATC2核内部包含了一个实时可切换的多路数据信号组选通器,【Signal Bank Count】代表了多路信号选通器的输入信号组数量。有效的信号组为1、2、4、8、16、32或64。

【TDM Rate】下拉列表框:ATC2核不用片上存储器资源来存储捕获的数据,Agilent逻辑分析仪通过一个专用探头和FPGA引脚连接传送捕获的数据。ATC2内核数据传送到FPGA引脚上的速率可以和ATC2输入端口DATA的速率相同或者是2倍速率。只有当目标数据捕获方式设臵成【State】时,TDM速率才可以设臵成2倍。

【Data Width】:ATC2核的每个输入信号组数据宽度与捕获模式及TDM速率相关。在【State】模式,每个信号组数据端口的宽度等于【ATD Pin Count】ATD引脚数和【TDM Rate】TDM速率的乘积。在【Timing】模式下,每个信号组数据端口的宽度等于(【ATD Pin Count】ATD引脚数+1)和【TDM Rate】TDM速率的乘积。

【Enable Auto Setup】复选框:使能Agilent逻辑分析仪自动设臵ATC2核引脚和逻辑分析仪POD的连接。这个属性使得Agilent逻辑分析仪能自动设定每个ATC2引脚的相位和采样电压偏移。缺省状态为使能。

Individual Pin Settings选项组。

【Pin Name】引脚名。

【Pin Loc】编辑框:设臵引脚的位臵。

【IO Standard】下拉列表框:设臵ATCK或每个ATD引脚的I/O标准,标准根据器件和驱动器终端类型而定。

【VCCO】:选择【IO Standard】后,VCCO会自动显示该标准对应的输出电压。

【Drive】下拉列表框: 设臵引脚输出驱动器的最大输出驱动电流,2~24mA。

【SKEW Rate】下拉列表框:设臵ATCK和ATD引脚的信号边沿斜率为FAST或SLOW。

Net connections选项卡:ATC2核网络连接,操作和ILA的网络连接部分一样。

Net Connections选项组:用于将ATC2核的输入信号与设计中的网线连接起来。

【Modify Connections】按钮:单击该按钮弹出【Select Net】对话框,对话框很容易地将ILA核工作时钟、触发信号、数据信号与设计中的网线连接起来。

4. 单击【Return Project Navigator】,退出内核插入器的配置,返回ISE中。

5. 在ISE的【Process】中双击【Implement】和【Generate Programming File】,可以生成比特流,并将刚才插入的各类核包含在比特文件中。如果只对ChipScope内核插入器修改,不需要重新【Sythesize】综合。

6. 打开ChipScope Analyzer,对采样数据进行分析。ChipScope Analyzer在后面小节中介绍。

电子发烧友App

电子发烧友App

评论