设计Testbench文件,得到了正确的结果。现在,在将实例设计实现到virtex 5板之后,我应该创建* .cdc文件来分析板上的输出。在示例设计文件中删除,没有* .cdc文件。如果我使用chipscope withput * .cdc文件进行分析,没有触发端口,也没有结果。 !

2020-04-07 14:52:25

3个对“RAMB16_S9_S9”的引用。ISE 13.3是否使用RAMB16-s作为逻辑?或者为什么“太多太多”被ISE流程链中的“Map”映射到了?/ dindea以上来自于谷歌翻译以下为原文

2019-07-26 14:40:53

修改就可以成为一个针对这个工程的很好的用于仿真的脚本。当然我们可以自己手动来编写类似的脚本,用ISE自动生成主要是为了涂个省事。2.调用ModelSim进行仿真在图2中,Process窗口中双击

2019-06-03 09:11:11

将设计上传到FPGA中。但是当我尝试使用chipScope Pro进行分析时,它会返回一条警告,表示没有连接Xilinx平台的USB电缆。我使用的是Windows 10。请告诉我们可以做些什么。问候

2019-04-18 12:38:46

嗨,大家好。我在安装ISE13.1并运行完全在ISE12.1中的项目后遇到如下问题,我在ISE13.1中检查了.cdc文件是否正确。那么有人可以给我一些建议吗?加载CDC项目F

2018-12-12 10:41:37

问题描述:我要通过spi获取ADC ROM中的内容。在综合后进行仿真,其结果和想要的结果一致,如图1所示。然后加入chipscope进行数据的抓取,但出现如下图的结果。其中FPGA的输入

2018-06-04 10:34:29

工程环境:ise 14.7FPGA板:Xilinx xc6slx25-3ftg256项目:在工程top文件中调用硬宏出现的问题:对工程进行综合时,报如下错误。

2022-03-04 09:34:29

请问书上这里写的“实现了newlib的移植和支持”,是指可以在SDK中直接include这个newlib库里的所有头文件吗?有大佬调用过吗

2024-01-10 07:35:16

我用的是C8051F300 准备在线调试,该用哪个口进行在线下载程序?

2019-06-04 05:55:54

作为一个新手,我想请问各位大神,CCS3.3如何进行在线实时仿真

2013-10-28 18:57:28

带来一定的不便。下面就分别以Xilinx公司的逻辑分析仪ChipScope和Altera公司的SignalTap做以下总结:一、使用Xilinx公司的ChipScope 在ChipScope中添加一些

2016-08-22 16:45:00

资源足够的情况下,设计者往往习惯于使用开发软件提供的在线逻辑分析仪进行调试,如ISE的Chipscole和QuartusII的SignalTappII,它们的功能都很强大,并且非常的简单实用。它们相较

2015-09-02 18:39:49

1 功能概述该工程实例内部系统功能框图如图所示。我们通过IP核例化一个FIFO,定时写入数据,然后再读出所有数据。通过ISE集成的在线逻辑分析仪chipscope,我们可以观察FPGA片内FIFO

2019-04-08 09:34:42

、ram、rom、fifo)的调用;8、掌握FPGA在线逻辑分析仪SignalTap/ChipScope使用方法;9、了解FPGA基本开发技巧;课程大纲: 第一阶段FPGA的工艺结构及其特点;FPGA

2012-09-07 14:19:38

、ram、rom、fifo)的调用;8、掌握FPGA在线逻辑分析仪SignalTap/ChipScope使用方法;9、了解FPGA基本开发技巧;课程大纲: 第一阶段FPGA的工艺结构及其特点;FPGA

2012-10-12 09:29:00

磁盘阵列 (RAID) 是磁盘阵列的管理工具。阵列迁移是将阵列模式升级到更高级的模式,首先需要添加硬盘数量。单盘,RAID 1/5 适用。TNAS如何进行在线阵列迁移1.前往TOS桌面-控制面板

2021-03-23 17:07:12

大家好!请问在使用RT-Thread studio进行在线仿真的时候,如何将程序复位?在Keil中进行在线仿真的时候,有一个程序复位按钮,可以回到程序运行最开始的地方。RT-Thread

2023-02-10 14:23:21

舰载综合处理系统由哪些模块组成?RapidlO逻辑层中直接IO/DMA和消息传递这两种传输方式有何差异?

2021-12-23 08:27:02

简介STM32支持连接调试器进行在线Debug调试,可以用于一步步的排查程序的错误STM32F1系列的Cortex-M3 支持两种调试主机接口(debug host interface ) :第一个

2022-01-26 07:09:06

,将捕获到的数据通过下载器回传给我们的用户界面,以便我们进行观察。在逻辑分析仪使用的过程中,我们一般常用的调用方法有两种:1、IP核2、mark debug标记信号接下来我们先说一下第一种方法。这种

2023-04-17 16:33:55

之前一直无法在win11上安装ise14.7,网上搜索也无果,所有一直vmware虚拟机使用。直到最近看了水木上jesce的回复,试了下果然可以直接安装使用的。但这样安装后只能编译,不能vivado

2024-02-27 14:25:22

我使用ISE 13.4对设计的代码进行逻辑综合和布局布线等。写的测试文件调用了一个RAM IP核,见图1。其中test_HRV_top为测试文件,调用了RAM_fangzhen这个IP核和设计顶层

2015-08-29 16:55:16

Xilinx ISE 12.2调用 Modelsim 进行行为仿真详解最近闲来无事,整点东西,以飨各位。第一步:新建工程: File->New Project 创建工程 cnt_for_sim

2012-02-29 10:17:25

本帖最后由 eehome 于 2013-1-5 09:54 编辑

Xilinx ISE 12.2 调用Modelsim进行行为仿真详解

2012-03-05 16:05:08

'ila_pro_0'.XST失败。错误:Xst:错误:sim:877 - 在执行IP'ILA期间发现错误(ChipScope Pro - 请参阅CoreGen日志/*/par1/results

2020-05-04 12:09:30

。Chipscope内嵌逻辑分析仪则是通过JTAG线缆连接到PC的ISE软件中查看信号波形。 3 硬件装配和其他实例不同,本实例的超声波测距模块需要和我们的板子进行装配连接。如图所示,在SF-SP6开发板的右上角插座P7用于连接超声波模块。 `

2015-11-23 11:24:49

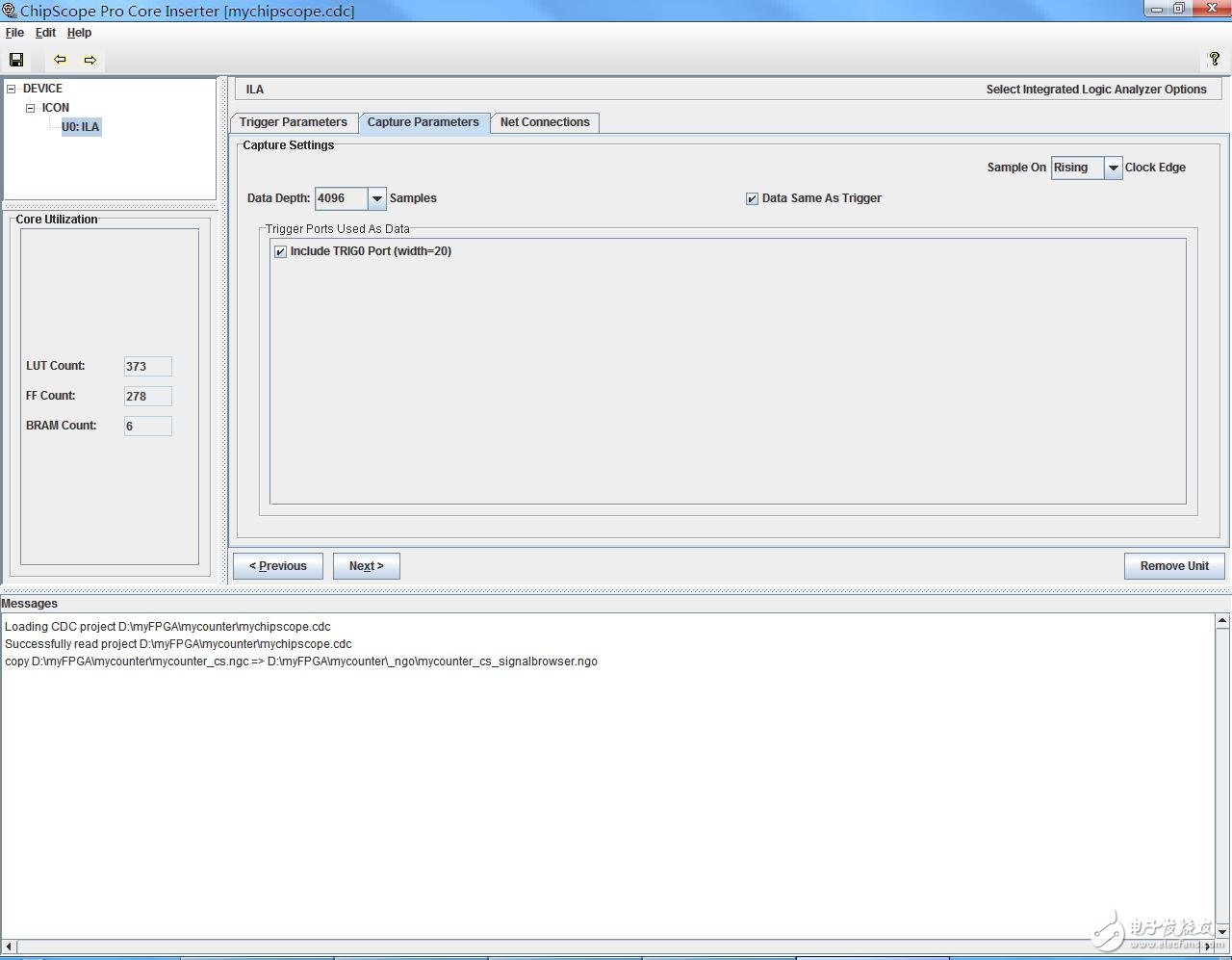

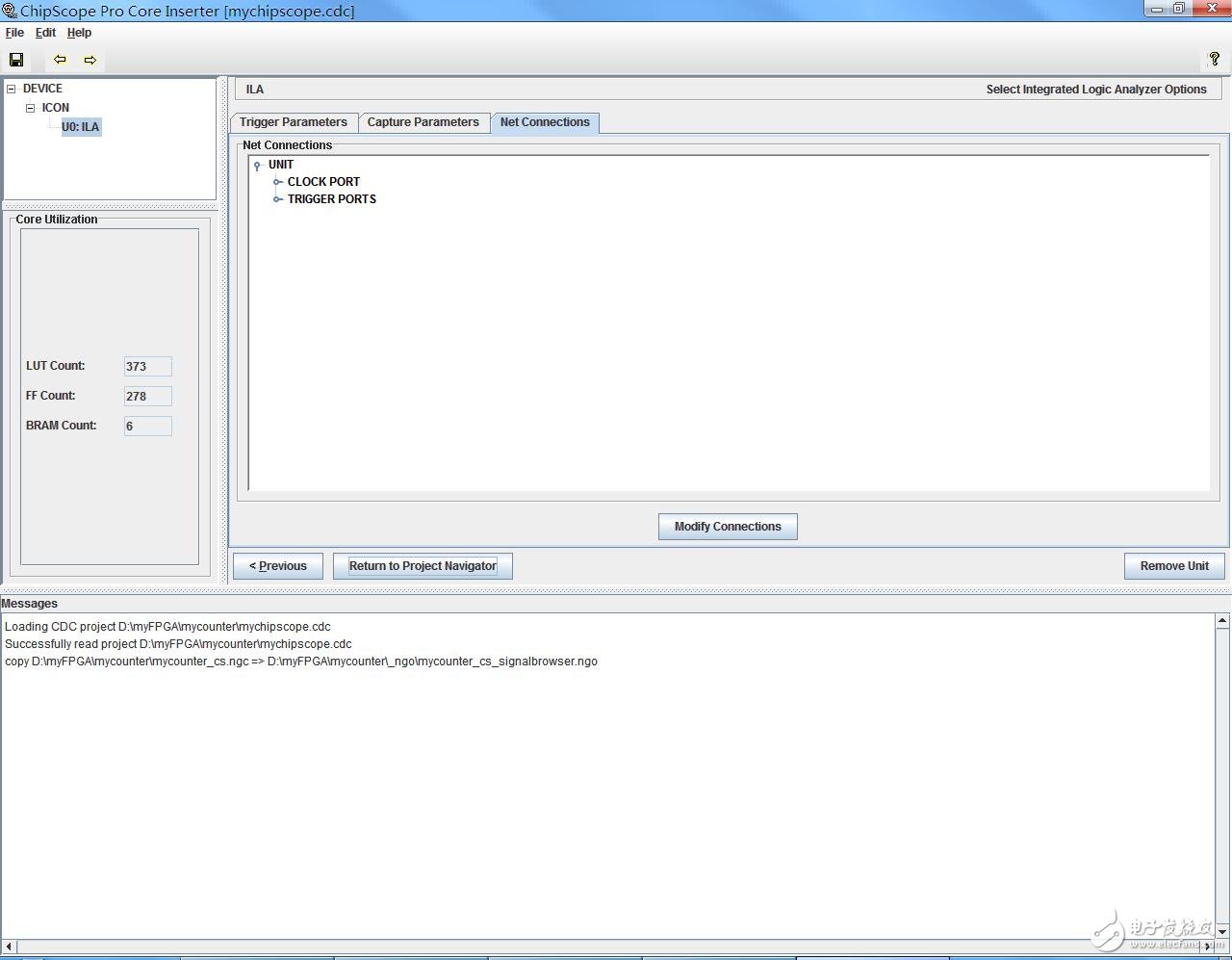

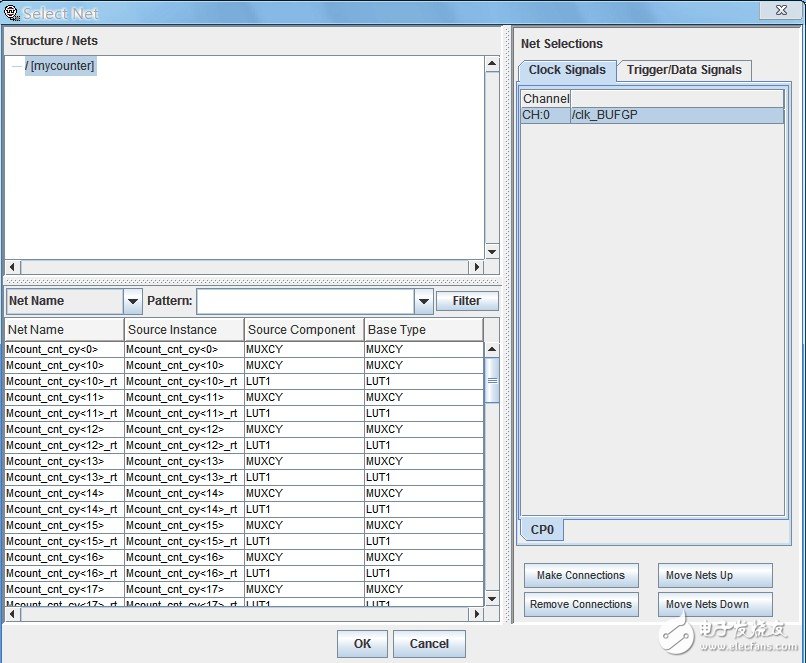

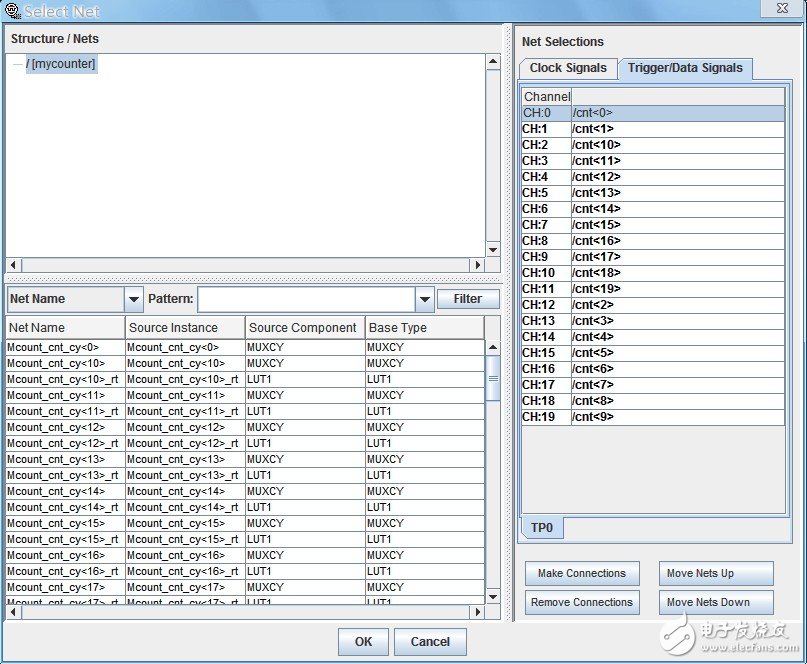

“chipscope_debug.cdc”的文件,如图所示。 3 Chipscope配置 双击“chipscope_debug.cdc”文件,可以进行chipscope基本参数的配置。第1个页面,如图所示

2015-11-25 13:45:30

`Xilinx FPGA入门连载40:SRAM读写测试之Chipscope在线调试特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1

2015-12-25 15:04:32

实例内部系统功能框图如图所示。我们通过IP核例化一个ROM,定时遍历读取其所有地址的数据。通过ISE集成的在线逻辑分析仪chipscope,我们可以观察ROM的读时序。 2 模块划分本实例工程模块层次

2016-01-06 12:22:53

`Xilinx FPGA入门连载46:FPGA片内ROM实例之chipscope在线调试特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm

2016-01-18 12:30:14

实例内部系统功能框图如图所示。我们通过IP核例化一个RAM,定时遍历写入其所有地址的数据,然后再遍历读出所有地址的数据。通过ISE集成的在线逻辑分析仪chipscope,我们可以观察FPGA片内RAM

2016-01-20 12:28:28

Xilinx FPGA入门连载50:FPGA片内RAM实例之chipscope在线调试特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1

2016-01-27 13:10:35

实例内部系统功能框图如图所示。我们通过IP核例化一个FIFO,定时写入数据,然后再读出所有数据。通过ISE集成的在线逻辑分析仪chipscope,我们可以观察FPGA片内FIFO的读写时序。 2 模块

2016-02-26 10:26:05

`Xilinx FPGA入门连载54:FPGA 片内FIFO实例之chipscope在线调试特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s

2016-03-04 13:13:12

。●fifo_test.v模块例化FPGA片内FIFO,并产生FPGA片内FIFO读写控制信号和写入数据,定时读出FIFO中的数据。●Chipscope_debug.cdc模块引出FIFO的读写控制信号和地址、数据总线,通过chipscope在ISE中在线查看FIFO的读写时序。 `

2016-03-07 11:32:16

`Xilinx FPGA入门连载58:FPGA 片内异步FIFO实例之chipscope在线调试特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s

2016-03-16 12:13:05

内存储器之间进行数据交互所必须的控制信号。●Chipscope_debug.cdc模块引出ROM、FIFO和RAM的读写控制信号和地址、数据总线,通过chipscope在ISE中在线查看其读写时序。 `

2016-03-16 12:43:36

内存储器之间进行数据交互所必须的控制信号。●Chipscope_debug.cdc模块引出ROM、FIFO和RAM的读写控制信号和地址、数据总线,通过chipscope在ISE中在线查看其读写时序。

2019-01-10 09:46:06

ChipScope 分析仪的用户界面6.4.2 ChipScope Analyzer的基本操作6.5 在ISE中直接调用ChipScope的应用实例6.5.1 在工程中添加ChipScope Pro文件

2012-04-24 09:23:33

完整的FPGA设计工程,以满足能够下载到FPGA器件中进行在线调试;Ⅱ、使用.stp文件在该工程中建立嵌入式逻辑分析仪,并进行相关设置,包括指定采集时钟、采样深度、触发条件、存储器模式、触发级别和添加

2019-12-04 10:30:42

调试核, 通过JTAG 硬核组件将采集信号发送到IDE进行调试。上一篇演示了LED流水灯,这一篇我们基于此进行在线逻辑分析仪调试体验。 过程菜单栏 Tools->Inserter 右下角点击

2023-02-05 21:40:57

为什么我用ISE进行fPga引脚约束时调用不出PlanAhead呢?真是好无语啊

2015-01-11 13:10:21

分析仪,可以帮助我们在线分析芯片内部逻辑。而且操作简单方便,但是往往因为某些原因,有些信号在综合的时候就会被优化掉,就可能会导致我们的设计失败,当然在为逻辑分析仪添加观察信号的时候也无法找到该信号

2023-05-16 17:48:23

请有人做“使用ChipScope分析设计”我的附加项目与ISE并通过电子邮件发送给我整个项目。因为当我做“使用ChipScope分析设计”我的项目时,cpj文件没有制作,我不知道为什么!?sallysoli @ gmail.comLgoicAnalyzer1.rar 814 KB

2020-04-10 10:53:27

我在使用chipscope编译ISE(webtpack)期间遇到以下错误。 (我刚刚购买了ChipScope并安装了许可证)。有什么想法吗?我很欣赏这个。错误:NgdBuild:1317- 使用核心

2018-11-28 15:12:01

使用ST-Link进行在线下载程序和调试使用正点原子提供的源代码移植到IAR上,有人说,为啥要移植到IAR上呢,也没啥,总有需要嘛。如下图所示为所有的库函数源代码...

2021-08-24 07:29:33

大家好。我使用VIO IP在ISE Design SUite软件中调试设计。当我运行工具有以下错误:检查扩展设计...错误:NgdBuild:604 - 类型为'chipscope_vio'的逻辑块

2019-08-02 08:10:22

大牛们,你们好!新手想请教一下,我在使用chipscope的export命令输出.prn文件,输出的数据是1个触发时钟1个。现在想让它100个时钟才输出一个数据,方便我在matlab工具中进行操作,请问这怎么弄啊 ?急求,在线等

2014-05-06 16:23:45

小弟我在Xilinx ISE webpack里的projrct navigator创建chipscope文件时出现了SRL和RPMs选项,由于教程是英语,所以还是不明白这两个参数的实际意义。有哪位大神知道的请帮帮忙解释下。谢!

2013-06-15 02:14:00

自己写的,用于将MDK的axf文件、IAR的out文件转换成bin文件,bin文件用产品代号、软件版本号、编译日期、bin文件size等信息命名,方便软件版本管理。可以在keil工程中直接调用。

2022-01-10 14:09:39

中的生成编程文件。我在Console中收到消息“Process”生成编程文件“已成功完成”。之后,我用iMPACT配置了目标器件(FPGA XC3S700A)。最后,我想分析一下我的设备

2018-12-11 11:15:26

嗨,如果我们为Chipscope购买许可证,我们可以在ISE webPACK中使用它(我们需要维护我们的旧设计)和Vivado webPACK吗?以上来自于谷歌翻译以下为原文Hi, if we

2018-12-14 11:30:42

于MCU串口设置不匹配,如串口号,波特率等信息。 2:单片机只能使用串口0进行在线仿真,不可以使用其他串口。仿真时可以先测试串口是否正常,先用串口调试工具下发0XA5,单片机正常跑DEBUG程序的时候会

2022-06-23 09:37:50

我是7系列FPGA的新手。最近开始使用Xilinx VC707板。在此之前,我曾经在Virtex 5上工作。我有一个ISE项目,使用Xilinx ISE和Chipscope使用Vitex 5板进行

2020-07-28 10:18:04

调用chipscope pro和EDK的命令。在此先感谢您的帮助。消息由johnsonwang编辑于09-23-2009 07:42 AM以上来自于谷歌翻译以下为原文Hi all I am

2019-03-28 14:26:03

putty+ssh,实现在windows中直接使用Ubuntu功能描述配置步骤步骤一:在ubuntu上配置SSH步骤二:在windows上通过SSH连接ubuntu功能描述如果你在你的windows

2021-12-24 08:23:13

请问怎么在AD的PCB文件中直接加元件呢?

2019-06-06 05:35:38

嗨,我是ZYNQ-7 ZC702评估板的新手,并按照ZYNQ 7000教程来习惯它。但是我在第4章(使用SDK和ChipScope调试)中遇到了麻烦,无法弄清楚问题是什么以及如何解决它......在

2019-11-08 15:21:30

你好: 我想在ISE中进行模块化设计,但是在TCL脚本方法中,还有其他方法可以进行模块化设计吗?以上来自于谷歌翻译以下为原文hello:I want to do modular design

2018-10-10 11:46:40

我们购买了ChipScope pro版本9.2i +串行IO工具套件(2008年底)。有没有办法获得使用当前ISE13.2的许可证,还是需要购买使用此版本ISE的新版ChipScope?如果是:我该

2018-11-22 11:45:04

STM32的启动流程是怎样的?怎样通过IAP来对STM32进行在线升级呢?

2021-11-30 07:39:28

你好,当我在Windows中双击Analyzer图标时,Windows 10工具栏中会出现一个非常短暂的小图标(几分之一秒),然后消失。没有其他对话框或消息出现,并且Chipscope无法启动

2020-05-25 07:30:04

安装ISE10.1完成后,新建文件时出现如图所示的选择框,没有chipScope文件格式,求大神指点

2013-09-22 09:42:38

最近在尝试使用chipscope对波形信号进行抓取,然后在网上找来点资料来看,有2个方法实现一种是使用 IP Core Generator,一种是使用chipscope Inserter

2016-09-29 16:26:57

各位大侠,请问一下,就是我在用IAR7.51A给CC2530进行在线仿真时,IAR就无响应了,这是什么问题。

2014-03-16 20:41:43

我有一个ISE 14.7的完整注册安装。我试图第一次使用Chipscope,它说我没有正确的许可证。如果我有完整的ISE14.7,是否需要单独的Chipscope许可证?我必须购买或者我可以评价一段时间吗?

2020-04-26 06:46:54

使用PrimeTIme进行时序分析,满足设计要求后即可进行FPGA芯片投片前的最终物理验证。6)调试与加载配置设计开发的最后步骤就是在线调试或者将生成的配置文件写入芯片中进行测试。在ISE中使用iMPACT。

2021-06-24 08:00:01

实用FPGA的调试工具—ChipScope Pro

ChipScope Pro应用于FPGA调试阶段,它具有传统逻辑分析仪的功能,可以观察FPGA内部的任何信号,触发条件,数据宽度和深度等的设

2010-02-09 15:10:46 95

95 本教程假定用户已有安装好仿真、综合、ISE 和相应的Chipscope,教程使用的环境如 下: 仿真:Modelsim 5.8 综合:Synplify pro 7.5.1 布局:ISE 6.2 分析:Chipscope 6.2

2011-05-10 14:49:52 0

0 2013-01-21 14:49:38 19

19 chipscope是一款在线逻辑分析仪,可实时有效的检查FPGA内部设计电路各需求中间节点的信号波形。

2015-11-23 11:36:24 2

2 Xilinx chipscope使用方法,针对刚刚开始接触FPGA的同学,零基础学习。

2016-03-21 16:57:04 1

1 老版本的ISE中曾经有stateCAD这个组件,可以很方便地进行FSM的设计;从ISE11开始,不再直接支持使用stateCAD进行设计了(也有绕过去的办法,见 ?board.id

2019-10-06 15:47:00 3426

3426

ISE中如何在未综合实现的前提下双击Analyze Design Using ChipScope打开ChipScope ?

2017-02-10 15:48:11 1252

1252

本节将简单介绍在PlanAhead工具中如何应用ChipScope核和分析工具进行逻辑调试与验证。先通过一个向导将ChipScope核插入设计中,选择待测试的网线,并进行例化、连接和综合,最后,导入布局和时序报告,产生位流文件,用ChipScope分析器进行验证。

2017-02-11 06:24:35 678

678

前几天在一个设计中,因为想对实际的硬件实现中的一些变量进行观测,而使用传统逻辑分析仪存在价格过于昂贵、并且需要大量探头,一些内部变量还不容易观测到等缺陷,所以想到了使用chipscope软件进行在线逻辑分析调试。

2017-02-11 12:26:59 3558

3558 关于chipscope中各模块的说明、调用等方法在以上的参考资料中都有详细说明,在这里就不详细叙述了。

2017-02-11 12:27:30 4824

4824

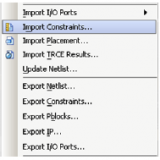

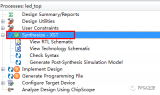

然后可以打开下载电缆和开发板的电源了。接下来在ISE Project Navigator的工程文件夹视图中点击“Analyze Design Using ChipScope”,ISE即可自动完成翻译

2017-02-11 12:31:19 1262

1262 文件包含.c和.h文件,可直接到工程中调用

2017-04-16 09:53:35 30

30 本文介绍了ise中chipscope的使用

2017-09-15 17:38:51 8

8 该教程则是向有一定 FPGA 基础的广大 FPGA 爱好者介绍现在非常流行的一种调试方法——利用逻辑分析仪 Chipscope 在线调试。

2017-12-11 14:55:52 18

18 本文档内容介绍了基于chipscope使用教程以及FPGA在线调试的方法,供参考

2018-03-02 14:09:49 9

9 在线考试系统旨在实现考试的无纸化管理,对一些科目的考试可以通过互联网络或局域网进行,方便校方考务的管理,也方便了考生,尤其适合考生分布广,不易集中的远程教育。我主要开发系统的后台管理系统—JAVA

2019-01-09 18:15:00 10

10 一、gcc 内联汇编 内联汇编即在C中直接使用汇编语句进行编程,使程序可以在C程序中实现C语言不能完成的一些工作,例如,在下面几种情况中必须使用内联汇编或嵌入型汇编。 程序中使用饱和算术运算

2021-11-16 09:26:27 6693

6693 教你怎么进行在线修复辊压机轴头磨损

2021-11-24 09:32:17 5

5 一般情况下ILA和VIO都是用在chipscope上使用,VIO可以作为在chipscope时模拟IO。

2022-06-12 15:51:54 1682

1682 电子发烧友网站提供《Gowin在线逻辑分析仪用户指南.pdf》资料免费下载

2022-09-15 15:31:29 0

0 有3种逻辑运算符:与(AND),或(OR),非(NOT)。在basic和Pascal等语言可以在程序中直接用and,or,not作为逻辑运算符。在C语言中不能再程序中直接使用,而是用其他符号代替。

2023-03-09 10:49:08 1891

1891 ChipScope是Xilinx提供的一个校验FPGA设计的工具。它的本质是一个虚拟的逻辑分析仪,能调用FPGA内部的逻辑资源对代码中的各个变量进行抓取分析。

2023-05-08 16:55:20 3792

3792

正在加载...

电子发烧友App

电子发烧友App

评论