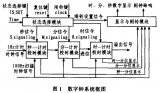

FPGA CPLFPGA CPLD 数字电路设计经验分享FPGA/CPLD数字电路设计经验分享摘要:在数字电路的设计中,时序设计是一个系统性能的主要标志,在高层次设计方法中,对时序控制的抽象度也相应

2012-08-11 10:17:18

系统是行之有效的,通过许多设计实例证明采用这种方式可以使电路的后仿真通过率大大提高, 并且系统的工作频率可以达到一个较高水平。本文档为你讲述FPGA/CPLD 数字电路设计经验和一些设计方法:[hide] [/hide]

2012-02-02 15:40:10

本帖最后由 xianer317 于 2014-6-21 19:34 编辑

FPGA/CPLD数字电路设计经验分享

2014-06-21 19:33:20

是行之有效的,通过许多设计实例证明采用这种方式可以使电路的后仿真通过率大大提高,并且系统的工作频率可以达到一个较高水平。FPGA数字电路设计经验分享[hide][/hide]

2012-03-05 16:33:30

是行之有效的,通过许多设计实例证明采用这种方式可以使电路的后仿真通过率大大提高,并且系统的工作频率可以达到一个较高水平。关键词:FPGA 数字电路 时序 时延路径 建立时间 保持时间

2011-05-03 11:46:03

` 本帖最后由 eehome 于 2013-1-5 10:00 编辑

FPGA经验谈(西安大唐电信)`

2011-09-29 11:05:40

FPGACPLD数字电路设计经验分享

2012-08-07 21:46:49

本帖最后由 eehome 于 2013-1-5 10:04 编辑

FPGA各种数字电路模拟

2012-08-11 11:32:00

本帖最后由 qiang6 于 2012-8-17 09:59 编辑

fpga经验谈(西安大唐电信)https://bbs.elecfans.com/forum.php?mod=viewthread&tid=266102&fromuid=483505

2012-08-17 09:49:14

fpga经验谈(西安大唐电信)

2012-08-18 07:25:33

接入点(AP)组成。系统组网方式可分为胖AP组网与瘦AP组网。目前大唐电信WLAN产品体系主要分为:胖AP系列、瘦AP系列及胖瘦可转型系列产品,为用户提供全面的无线局域网应用解决方案。大唐电信是中国移动

2019-06-14 06:30:32

数字电路-数字时钟电路设计 希望大家喜欢。

2016-12-06 09:46:39

数字电路设计与Verilog HDL

2015-07-16 16:21:19

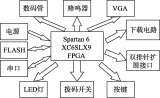

数字电路作为一门专业基础课,除了介绍数字电路的理论知识外,更需要通过配套的实验平台将理论知识和实践环节相结合,培养学生的动手能力和实践创新能力。为此,自主开发了基于 FPGA 的数字电路“口袋实验室

2020-09-04 17:04:34

在数字电子技术基础课程中,数字电路设计的数学基础是布尔函数,并利用卡诺图进行化简。卡诺图只适用于输入比较少的逻辑函数的化简。数字电路的设计方法是:组合电路设计:提出问题→确定逻辑关系→列真值表→逻辑

2019-02-27 11:55:00

电路设计[FPGA]设计经验

2012-05-23 19:49:45

电路设计[FPGA]设计经验

2012-08-20 15:37:36

电路设计[FPGA]设计经验

2019-01-03 14:19:28

《数字电路》课程口袋型FPGA实验板

2021-01-28 06:58:12

《HELLO+FPGA》-+数字电路篇

2017-09-27 10:07:03

关于数字电路设计的一些经验

2015-03-17 21:27:38

,英语4级以上,对数字电路设计有强烈爱好;2、具有扎实的单片机、数字电路、模拟电路理论知识,精通数字电路设计和PCB板设计,精通Protel/Altium Designet (ORCAD或PADS等

2017-10-16 10:57:04

数字逻辑电路分类数字电路的特点数字电路的应用

2021-04-06 09:08:57

分享一款不错的基于可编程逻辑器件PLD的数字电路设计方案

2021-04-30 06:34:54

本帖最后由 gk320830 于 2015-3-5 00:03 编辑

华为《高速数字电路设计教材》

2012-08-20 13:23:04

华为《高速数字电路设计教材》这本书是专门为电路设计工程师写的。主要描述模拟电路原理在高速数字电路设计中的分析应用

2014-09-01 23:09:11

华为《高速数字电路设计教材》这本书是专门为电路设计工程师写的。主要描述模拟电路原理在高速数字电路设计中的分析应用

2014-09-01 23:20:19

本帖最后由 gk320830 于 2015-3-5 07:26 编辑

华为高速数字电路设计-华为黑魔书

2012-08-28 17:04:52

本帖最后由 eehome 于 2013-1-5 10:02 编辑

就算作一个数字电路设计,附有 protuse仿真图还有 相关用到的资料

2012-06-08 14:12:12

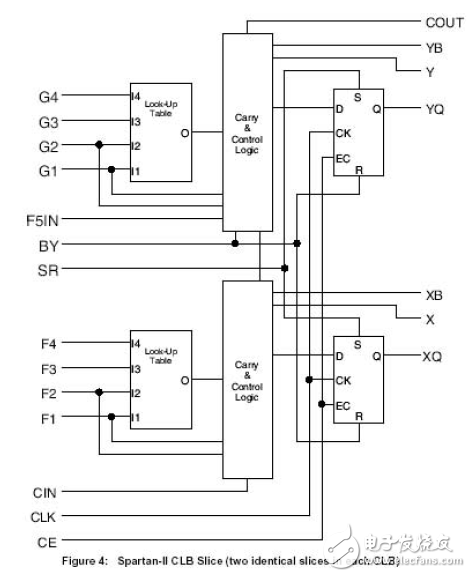

FPGA芯片是由哪些部分组成的?如何去实现一种基于FPGA芯片的可重构数字电路设计?

2021-11-05 08:38:57

射频和数字电路设计的区别是什么?

2021-05-18 06:05:19

FPGA/CPLD 数字电路设计经验 技术交流讲义FPGA/CPLD数字电路设计经验分享摘要:在数字电路的设计中,时序设计是一个系统性能的主要标志,在高层次设计方法中,对时序控制的抽象度也相应

2012-10-26 17:24:58

数字系统的设计人员擅长在其印制电路板上用FPGA和CPLD将各种处理器、存储器和标准的功能元件粘合在一起来实现数字设计。除了这些数字功能之外,FPGA和CPLD还可以使用LVDS输入、简单的电阻电容(RC)电路和一些FPGA或CPLD的数字逻辑单元实现共模功能,从而构建模数转换器(ADC)。

2019-08-19 06:15:33

怎么实现基于可编程逻辑器件的数字电路设计?

2021-05-06 08:36:18

大家好,我是电子爱好者新手,现在想学点数字电路设计。刚把数字电路这么课程学完。我想学电路设计,不知道如何下手。比如FPGA什么的,这些都怎么开始学习啊。请知情者指点下。谢谢

2013-08-02 08:17:31

数字集成电路设计ASIC设计/验证经验;2.熟悉逻辑/时序电路的原理和设计;3.精通verilog语言;熟练使用Cadence,Modelsim,NC-Verilog,DC等设计验证工具;4.有较强的责任心

2015-02-27 10:52:58

为什么淘宝上这本书的销量那么低?有其他数字电路设计的实用书也可以推荐~谢谢!

2017-10-19 17:18:52

模拟电路与数字电路的定义及特点模拟电路与数字电路之间的区别模拟电路和数字电路之间的联系如何实现模拟和数字电路的功能

2021-03-11 06:58:41

了“创新设计性实验优秀论文、作品评奖制度”,对经专业教师评审选出的优秀论文、创新作品的学生给予表彰、奖励。 3结束语 通过开设数字电路设计性实验教学,不仅加强了学生的电子系统设计能力、制作能力和工程

2012-10-25 11:59:02

,这种实验教学模式禁锢了学生的创新思维,失去了“实验”真正的含义,培养出来的学生实践技能差,无法达到高职教育人才培养的要求〔2)0 2开设数字电路设计性实验采取的措施 通过多年来的实验教学改革实践

2012-10-28 14:58:16

【简介】本书从高速数字电路的定义谈起,介绍了传输线的基本理论,并涉及到了如何运用Grounding/Guard降低噪声等内容,还以高速数字电路电气特性,如串扰、反射及时钟脉冲不对称等为例,阐述了一些

2017-12-12 08:51:55

《高速数字电路设计及EMC设计》分享。

2015-08-04 11:50:33

高速数字电路设计的几个基本概念高速数字电路设计的基本要求是什么

2021-04-27 06:19:05

基于LabVIEW的数字电路设计和仿真

数字电路设计和仿真是电子工程领域的基本技术。介绍了基于LabV IEW的数字电路设计和仿真的原理和方法,比较了其与专业EDA软

2010-03-30 16:09:49 123

123 摘要:在数字电路课程设计中引入先进的EDA技术是数字电路实验教学改革的方向,本文通过一个数字电路课程设计的实例,说明了基于EDA技术中的VHDL语言和CPLD/FPGA器件进行数字系

2010-04-26 10:08:50 23

23 当利用CPLD/FPGA开发系统完成数字电路或系统的开发设计并仿真校验通过之后,就需要将获得的CPLD/FPGA编程配置数据下载到CPLD/FPGA芯片中,以便最后获得所设计的硬件数字电路或系

2010-06-01 10:14:46 23

23 本书是专门为电路设计师工程师写的

它主要描述模拟电路原理在高速数字电路设计中的分析应用

1-3章分别介绍了模拟电路术语、逻辑门高速特性和标准高速电路测量

2010-06-23 18:02:57 63

63 流水线技术在高速数字电路设计中的应用

2010-07-17 16:37:21 6

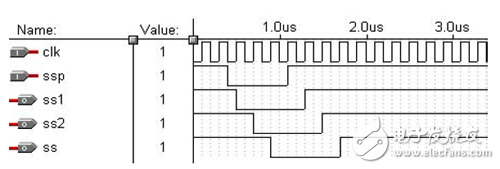

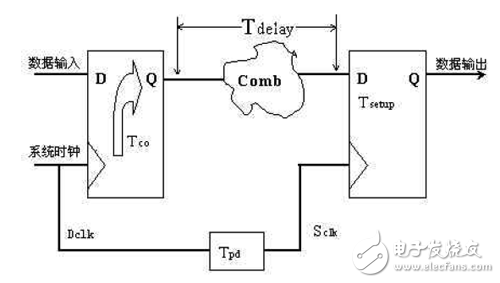

6 摘要:在数字电路的设计中,时序设计是一个系统性能的主要标志,在高层次设计方法中,对时序控制的抽象度也相应提高,因此在设计中较难把握,但在理解RTL电路时序模型的

2010-08-13 14:53:34 1680

1680 这本书是专门为电路设计工程师写的。它主要描述了模拟电路原理在高速数字电路设计中的分析应用。通过列举很多的实例,作者详细分析了一直困扰高速电路路设计工程师的铃

2010-11-08 16:49:54 0

0 高速数字电路设计

关于高速数字电路的电气特性,设计重点大略可分为三项 : Ø 正时 (Timing) :由于数字电路大多依据时脉信号来做信号间的同

2007-10-16 17:22:57 2746

2746 数字电路设计

关于高速数字电路的电气特性,设计重点大略可分为三项:

正时(Timing) :由于数字电路大

2009-08-26 19:08:06 2665

2665 基于可编程逻辑器件的数字电路设计

0 引 言

可编程逻辑器件PLD(Programmable Logic De-vice)是一种数字电路,它可以由用户来进行编程和进行配置,利用它可以

2009-11-16 10:46:41 1473

1473

基于FPGA和CPLD数字逻辑实现ADC技术

数字系统的设计人员擅长在其印制电路板上用FPGA和CPLD将各种处理器、存储器和标准的功能元件粘合在一起来实现

2010-05-25 09:39:10 1309

1309

《VHDL与数字电路设计》是有卢毅、赖杰主编的,主要介绍涉及数字系统设计的多方面原理、技术及应用,主要内容有数字系统的基本设计思想、设计方法和设计步骤, VHDL 硬件描述语言

2011-07-11 15:54:27 0

0 主要内容有:第1 章实验基本知识、第2 章 PROTEUS 仿真软件快速入门、第3 章数字电路基础实验、第4 章数字电路综合设计实验、 第5章VHDL 语言基础、第6 章 数字电路的CPLD/FPGA 实现。在教

2011-09-07 16:29:53 0

0 2015-07-02 15:50:46 14

14 高速数字电路设计及EMC设计!资料来源网络,如有侵权,敬请见谅

2015-11-19 14:48:57 0

0 数字电路中的FPGA和verilog教程,好东西,喜欢的朋友可以下载来学习。

2016-01-18 17:44:30 42

42 高速数字电路设计及EMC设计(华为),下来看看。

2016-03-29 15:41:20 52

52 电路设计[FPGA]设计经验,有需要的下来看看

2016-05-20 11:16:35 46

46 电子专业单片机相关知识学习教材资料——FPGACPLD数字电路设计经验,感兴趣的小伙伴们可以瞧一瞧。

2016-09-13 17:46:48 0

0 高速数字电路设计大全

2017-01-17 19:54:24 55

55 数字电路设计方案中DSP与FPGA的比较与选择

2017-01-18 20:39:13 15

15 在数字电路的设计中,时序设计是一个系统性能的主要标志,在高层次设计方法中,对时序控制的抽象度也相应提高,因此在设计中较难把握,但在理解RTL电路时序模型的基础上,采用合理的设计方法在设计复杂数字系统

2017-02-11 13:04:32 1291

1291

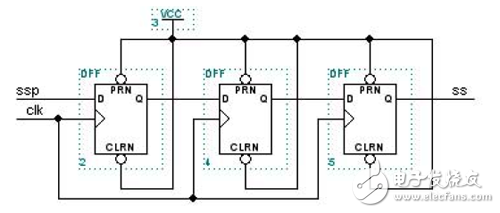

异步设计不是总能满足(它们所馈送的触发器的)建立和保持时间的要求。因此,异步输入常常会把错误的数据锁存到触发器,或者使触发器进入亚稳定的状态,在该状态下,触发器的输出不能识别为l或0。如果没有正确地处理,亚稳性会导致严重的系统可靠性问题。

2017-02-11 13:11:49 700

700

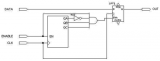

当你需要将FPGA/CPLD内部的信号通过管脚输出给外部相关器件的时候,如果不影响功能最好是将这些信号通过用时钟锁存后输出。因为通常情况下一个板子是工作于一种或两种时钟模式下,与FPGA/CPLD相连接的芯片的工作时钟大多数情形下与FPGA的时钟同源,如果输出的信号经过时钟锁存可以起到如下的作用:

2017-02-11 13:18:12 1948

1948

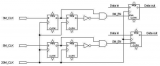

当产生门控时钟的组合逻辑超过一级(即超过单个的“与”门或“或”门)时,证设计项目的可靠性变得很困难。

2017-02-11 13:28:49 1409

1409

电子天平中数字电路的CPLD实现_顾申申

2017-03-19 11:29:00 2

2 ,或是硬件描述语言自由的设计一个数字系统。通过软件仿真,我们可以事先验证设计的正确性。在PCB完成以后,还可以利用FPGA/CPLD的在线修改能力,随时修改设计而不必改动硬件电路。 使用FPGA/CPLD来开发数字电路,可以大大缩短设计时间,减少PCB面积,提高系统的可靠性。 FPGA/CPLD还

2017-10-09 09:52:20 14

14 这本书是专门为电路设计工程师写的。它主要描述了模拟电路原理在高速数字电路设计中的分析应用。通过列举很多的实例,作者详细分析了一直困扰高速电路路设计工程师的铃流、串扰和辐射噪音等问题。

2018-09-10 08:00:00 61

61 用VHDL语言设计交通灯控制系统,并在MAX+PLUS II系统对FPGA/CPLD芯片进行下载,由于生成的是集成化的数字电路,没有传统设计中的接线问题,所以故障率低、可靠性高,而且体积小。体现了EDA技术在数字电路设计中的优越性。

2018-11-05 17:36:05 23

23 .docx DC-DC升压电路.docx FPGACPLD数字电路设计经验分享.docx MIC电路工作总结.docx MOS管驱动电路详解.docx PCB电路设计指南(经典).docx PLC输出电路

2019-01-11 18:19:38 0

0 高速数字电路设计跟低速数字电路设计不同的是:他强调组成电路的无源部件对电路的影响。这些无源器件包括导线、电路板和组成数字产品的集成电路。在低速设计中,这些部件单纯

的只是电路的一部分,根本不用多做考虑,可是在高速设计中,这些部件对电路的性能有着直接的影响。

2019-04-11 11:38:32 3581

3581

采用FPGA进行的数字电路设计具有更大的灵活性和通用性,已成为目前数字电路设计的主流方法之一。

2019-07-24 09:06:12 4289

4289

可编程逻辑器件PLD(Programmable Logic De-vice)是一种数字电路,它可以由用户来进行编程和进行配置,利用它可以解决不同的逻辑设计问题。

2020-04-28 11:18:49 2324

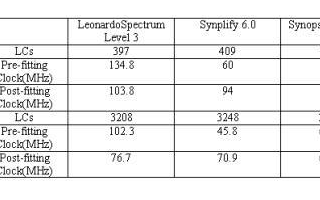

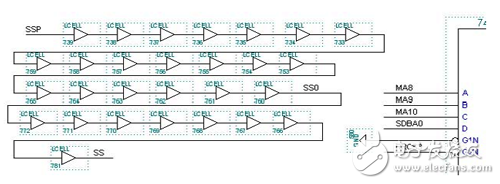

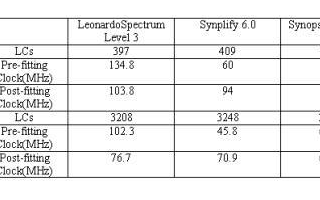

2324 在使用FPGA做数字电路设计的流程中,综合是其中非常重要的一个步骤。同样的设计源代码,无论是VHDL或Verilog HDL,采用不同的综合工具综合会产生不同的结果。

2020-07-24 15:47:00 1836

1836

数字电路作为一门专业基础课,除了介绍数字电路的理论知识外,更需要通过配套的实验平台将理论知识和实践环节相结合,培养学生的动手能力和实践创新能力。

2020-08-16 12:03:45 6487

6487

大唐电信的子公司有:11个,分别是:西安大唐电信有限公司、大唐半导体设计有限公司、广州要玩娱乐网络技术股份有限公司、大唐电信(香港)有限公司、大唐终端技术有限公司、大唐终端设备有限公司、江苏

2020-08-17 10:10:41 12095

12095 在当今电子技术行业发展过程中,对高速电路数字设计十分关注,高速数字电路是利用多个电子元件组成的,可以让计算机高速数字电路技术进一步提高,因此在计算机中使用高速数字电路设计技术也就更加普遍。

2020-08-21 17:41:10 2924

2924 在数字电路的设计中,时序设计是一个系统性能的主要标志,在高层次设计方法中,对时序控制的抽象度也相应提高,因此在设计中较难把握,但在理解RTL电路时序模型的基础上,采用合理的设计方法在设计复杂数字系统

2021-01-20 14:26:03 14

14 高速数字电路设计-华为

2021-04-21 15:45:08 0

0 华为高速数字电路设计教材资源下载

2021-06-04 11:06:00 86

86 FPGA CPLD数字电路设计经验分享.(电源技术发展怎么样)-FPGA CPLD数字电路设计经验分享

2021-09-18 10:58:03 51

51 直接说正题,帮助一下刚刚入门的朋友们,也算是学习IC设计的一个总结吧。 一、首先要知道自己在干什么? 数字电路(fpga/asic)设计就是逻辑电路的实现,这样子说太窄了,因为asic还有不少是模拟

2021-11-06 11:36:01 18

18 实用电子电路设计与调试数字电路教材资料免费下载。

2022-04-07 14:46:38 26

26 黑魔书 351页- 高速数字设计PDF版,华为内部数字电路设计教材

2022-06-08 14:33:25 0

0 高速数字电路设计教材-华为

2022-06-13 14:55:54 0

0 数字电路设计是数字电路最为关键及重要的一步,今天我们将从各个流程为大家介绍完整的数字电路设计!

2022-07-10 17:14:16 6047

6047 数字电路是现代电子领域中最基础和重要的一部分,工程师的数字电路水平不仅关系到电路设计的质量,还关系到整个系统的稳定性和性能。如何提高数字电路水平,成为一名优秀的数字电路设计工程师呢?下面我们就来探讨一下。

2023-02-17 10:20:39 270

270 高速数字电路设计

2022-12-30 09:22:18 19

19 高速数字电路设计教材-华为

2022-12-30 09:22:18 41

41 电子发烧友网站提供《FPGA/CPLD数字电路设计经验分享.pdf》资料免费下载

2023-11-21 11:03:12 3

3

正在加载...

电子发烧友App

电子发烧友App

评论