1、 应用背景

基于ARM+FPGA的高速同步数据采集方案,解决了数据采集的同步性问题,与以往

2010-07-22 16:36:17 1326

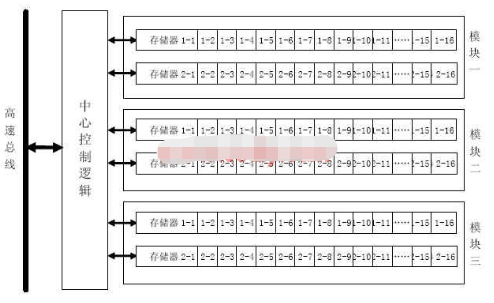

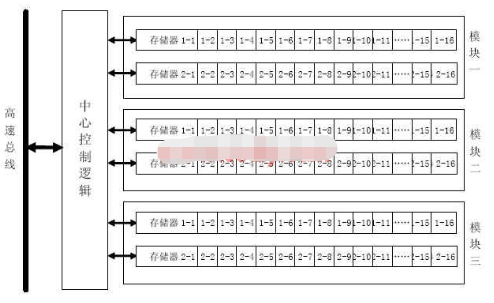

1326 本文介绍了一种以FPGA作为控制器,FLASH MEMORY作为主存储器的大容量高速存储系统方案,并对关键技术及实现途径进行了论述,在存储容量及存储速度上实现了突破。

2020-07-30 17:53:54 1917

1917

FPGA高速收发器设计原则高速FPGA设计收发器选择需要考虑的因素

2021-04-09 06:53:02

大容量、高速率和低功耗已成为FPGA的发展重点。嵌入式逻辑分析工具无法满足通用性要求,外部测试工具可以把FPGA内部信号与实际电路联合起来观察系统真实运行情况。随着FPGA技术的发展,大容量、高速

2019-08-07 07:50:15

什么是传输线效应?高速DSPs的PCB电路板该怎样去设计?

2021-04-25 06:27:07

高速FPGA PCB设计指南

2012-08-16 17:01:22

高速DAP仿真器 BURNER

2023-03-28 13:06:20

最近看了一篇文章,也转到了我的博里了,讲的是LVDS、CML以及PECL接口以及相互之间的对接。个人总结这种差分高速串行接口互联应该注意下面三个问题:交流耦合或者直流耦合以使信号传输;直流偏置以满足

2015-01-22 14:20:51

咨询一个初级A/D问题:AD9684中DCO时钟的用法(FPGA控制)。AD9684与FPGA用LVDS模式接口互联时,FPGA端如何使用?手册中没有详细说明,是DCO上升沿捕获数据,作为数据同步

2023-12-13 09:01:52

PCIE高速传输方案传输的带宽利用率可达到90%以上,延迟可达到理论的最低延迟值。该方案已经应用到航天航空、雷达等领域。一、 高效率传输方案 该采集方案 Demo 基于 VC709 开发板

2021-05-19 08:58:02

面临比赛 , 我想利用STM32做一个高速的DA的模块 。 因为从手册上看到 , STM32自带的DA速度只有1M 。 我想问一下 , 谁有STM32做高速DA的方案 。思路也行。还有能推荐几款

2013-08-11 11:41:24

mcu和mpu、DSPs有什么区别?处理器分为微处理器(MPU)、控制器(MCU)、数字信号处理器(DSPs)微处理器(MPU)不为特定计算目的实际的芯片。最常见的微处理器是Motorola的68K

2021-11-10 07:16:27

对数据采集与处理系统提出了新的更高的要求,即高速度、高精度和高实时性。对数据采集与处理系统的设计,有以下3种方案可供选择:(1)A/D+DSP方案在传统的高速信号处理中,大多采用这种方案。将A/D、D

2019-07-05 06:41:27

SEED-HPS6678(HPS6678)是北京艾睿合众科技有限公司新推出的新一代高端DSP+FPGA应用方案。DSP采用TI公司首颗最高主频为10GHz的8核浮点DSP芯片TMS320C6678

2019-09-24 08:29:12

本文根据当前FPGA的高速总线测试和分析,提供了最新的方法和工具。

2021-05-11 06:24:02

FPGA数字信号处理——基于FPGA和高速DAC的DDS设计与频率调制(一)——X现如今,随着高速模数-数模转换技术和FPGA的发展。FPGA的高速性、并行性、高数据吞吐量与高速数模-模数转换技术

2021-07-23 08:06:59

本帖最后由 eehome 于 2013-1-5 10:01 编辑

基于FPGA的高速AD转换

2012-08-06 12:50:15

高速LVDS数据传输方案和协议基于FPGA的高速LVDS数据传输本人在北京工作6年,从事FPGA外围接口设计,非常熟悉高速LVDS数据传输,8B/10B编码等,设计调试了多个FPGA与FPGA以及

2014-03-01 18:47:47

高速传输,但DSP价格过于昂贵。而利用FPGA和USB接口芯片结合的方案,具有功耗低、时钟频率高、速度快、效率高、组合形式灵活等特点,是单片机和DSP所无法比拟的。

2019-09-05 07:22:57

基于FPGA的通用高速串行互连协议设计基于FPGA的通用高速串行互连协议设计

2012-08-11 15:46:52

基于高速FPGA 的PCB 设计技巧

2012-08-06 12:57:11

FPGA配置的功能有哪些?FPGA的配置速度怎样?如何使用高速NOR闪存对FPGA进行配置?

2021-08-03 06:51:30

高速连续数据采集系统的背景及功能是什么?如何利用FPGA实现高速连续数据采集系统设计?FPGA在高速连续数据采集系统中的应用有哪些?

2021-04-08 06:19:37

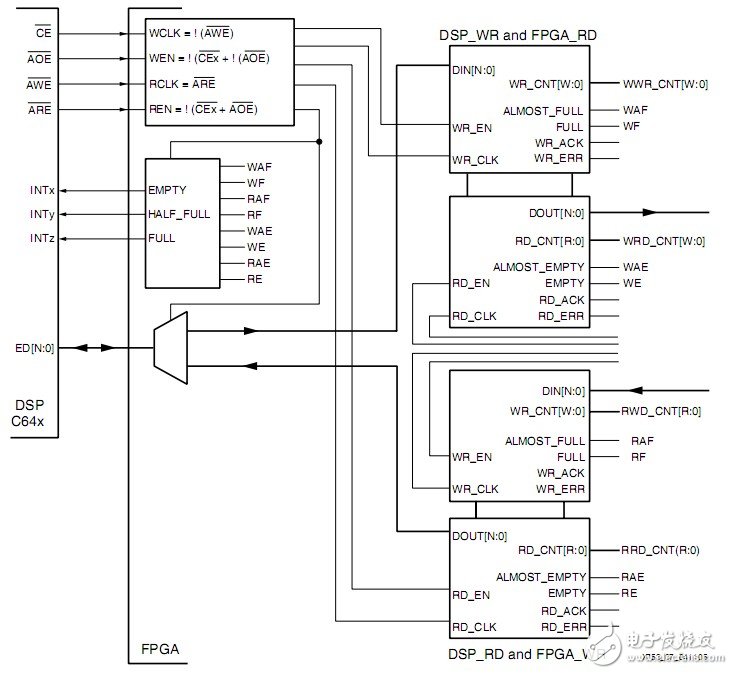

一种FPGA与DSP的高速通信接口设计与实现方案

2021-06-02 06:07:16

5G、云和数据中心带来前所未有的互联体验:惊人的速度、大规模的连接、超高可靠与低时延,爆炸性增长的数据最终将搭上5G这个高速无线列车,进入到生活的方方面面。从而此次连接革命所产生的影响将超越智能手机

2018-04-17 10:08:46

寻求一个FPGA与stm32高速通讯的方案。速度要求达到USB2.0速度。48m原设计通过。stm32+u***达到48m可是FPGA与32通行的速度没有找达到48m方案。或者FPGA,u***上位机通讯可以直接打到。48m那位高手做过这样的方案,请推荐一下。

2020-11-03 21:05:29

本文针对铁路点多、线长,站点分布较散,呈线形分布等特殊情况,充分利用铁路现有的SDH有线传输设备SBS622,通过设计的固定在火车站上的基地台与高速列车上的移动台之间的无线接口以及加顶圆盘天线等技术,实现了铁路高速列车互联网络DS-CDMA无线传输系统。

2021-05-31 06:22:25

如何使用宽频率范围矢量网络分析仪去应对高速互联测试的挑战?

2021-04-30 07:25:40

本文的创新点是提出了一种基于FPGA的高速数据中继器设计方案,并综合分析了ASIC和NP等方法设计的高速网络中继器设计方法,在设计的功能和灵活性两方面做了很好的权衡。

2021-04-29 06:45:51

速度最高可达到 5 GBaud;(4) FPGA 采集卡支持双通道 250MSPS12Bit 高速高精度 ADC,一路 175MSPS12Bit 高速高精度 DAC,满足多种数据采集需求;(5)支持

2022-09-15 17:41:29

求大神分享一种高速突发模式误码测试仪的FPGA实现方案

2021-04-29 06:58:18

紫光的FPGA哪些系列支持高速接口?相关接口有哪些免费的IP可以使用呢?性能怎么样?

2024-03-20 16:58:29

赛灵思 Artix-7 FPGA 是业界唯一的在低端器件上整合了高速收发器的方案,该方案提供了自适应均衡、2D 眼图以及IBIS-AMI仿真模型来简化针对成本敏感型应用的高速串行设计,观看视频,4分钟教您搞定高速SerDes端口设计。

2016-07-27 17:29:59

各位大神请问FPGA和arm互联的硬件电路是怎么样的啊,我想做到高速的数据交换,需要注意什么,还有电路中的总线驱动器是必须的吗求原理图,网上原理讲很多,可是对我这种菜鸟不顶用

2022-04-28 10:16:13

我们设计的系统里面需要实现DSP28377和ARM之间的高速互联,目前拟定的方案有双口RAM并行总线互联和SPI总线互联,请问还有其它高速总线互联方式吗?

2018-09-20 14:14:15

TI 相关技术支持专家 你们好 : 我在一个项目中使用了DM385 作为视频的解压缩方案,现在要将压缩后的视频流传输到fpga 基带,通过无线发送。想问一下,dm385 能不能通过u*** 实现互联

2020-08-18 07:03:22

各位大神请问FPGA和arm互联的硬件电路是怎么样的啊,我想做到高速的数据交换,需要注意什么,还有电路中的总线驱动器是必须的吗求原理图,网上原理讲很多,可是对我这种菜鸟不顶用

2022-06-07 15:53:01

请问小基站解决方案能否满足4G时代移动互联的需求?

2021-04-19 09:32:45

XC7K325T作为协处理单元,可支持两个标准HPC接口FMC子卡,两片DSP之间通过HyperLink进行高速互联,两片FPGA与两片DSP通过1个8端口的SRIO交换芯片连接至背板,板与板之间通过VPX背板

2016-03-02 13:52:47

XC7K325T作为协处理单元,可支持两个标准HPC接口FMC子卡,两片DSP之间通过HyperLink进行高速互联,两片FPGA与两片DSP通过1个8端口的SRIO交换芯片连接至背板,板与板之间通过VPX背板

2016-03-09 10:12:15

XC7K325T作为协处理单元,可支持两个标准HPC接口FMC子卡,两片DSP之间通过HyperLink进行高速互联,两片FPGA与两片DSP通过1个8端口的SRIO交换芯片连接至背板,板与板之间通过VPX背板

2016-03-16 11:00:00

XC7K325T作为协处理单元,可支持两个标准HPC接口FMC子卡,两片DSP之间通过HyperLink进行高速互联,两片FPGA与两片DSP通过1个8端口的SRIO交换芯片连接至背板,板与板之间通过VPX背板

2016-03-30 11:12:53

XC7K325T作为协处理单元,可支持两个标准HPC接口FMC子卡,两片DSP之间通过HyperLink进行高速互联,两片FPGA与两片DSP通过1个8端口的SRIO交换芯片连接至背板,板与板之间通过VPX背板

2016-04-07 10:40:35

XC7K325T作为协处理单元,可支持两个标准HPC接口FMC子卡,两片DSP之间通过HyperLink进行高速互联,两片FPGA与两片DSP通过1个8端口的SRIO交换芯片连接至背板,板与板之间通过VPX背板

2016-04-14 11:09:20

XC7K325T作为协处理单元,可支持两个标准HPC接口FMC子卡,两片DSP之间通过HyperLink进行高速互联,两片FPGA与两片DSP通过1个8端口的SRIO交换芯片连接至背板,板与板之间通过VPX背板

2016-04-25 11:21:12

作为协处理单元,可支持两个标准HPC接口FMC子卡,两片DSP之间通过HyperLink进行高速互联,两片FPGA与两片DSP通过1个8端口的SRIO交换芯片连接至背板,板与板之间通过VPX背板

2016-03-23 11:03:18

DVI[1]接口标准作为新一代的数字显示技术通讯标准,以全数字化的数据码流在传输信道上传输,本文针对DVI 接口标准提出了一种基于FPGA 的高速实时的数据传输方案。方案中重

2009-09-22 10:12:34 15

15 本文介绍了一种基于FPGA 的高速多路数据采集系统的设计方案,描述了系统的主要组成及FPGA 的实现方法。在硬件上FPGA 采用ACEX1K100 器件,用于实现A/D 转换器的控制电路、多路

2009-12-19 16:02:33 50

50 高速互联链路中参考时钟的抖动分析与测量

在高速互联链路中,发送器的参考工作时钟的抖动是影响整个

2010-04-15 14:01:39 19

19 利用国际空间数据系统咨询委员会(CCSDS)高级在轨系统(AOS)建议,提出了两级复用的方案,设计了一种具有载荷数据存储功能的高速实时/回放分级复接器。该方案采用FPGA技术,对星上载荷

2010-07-28 16:51:47 14

14 FPGA高速收发器设计原则

高速收发器(SERDES)的运用范围十分广泛, 包括通讯、计算机、工业和储存,以及必须在芯片与

2009-04-07 22:26:14 986

986 基于FPGA的高速定点FFT算法的设计方案

引 言 快速傅里叶变换(FFT)作为计算和分析工具,在众多学科领域(如信号处理、图像处理、生物信息学、计算物理

2010-02-09 10:47:50 992

992

FPGA设计的高速FIFO电路技术

本文主要介绍高速FIFO电路在数据采集系统中的应用,相关电路主要有高速A/D转换器、FPGA、SDRAM存储器等。图1为本方案的结构框图。在大容量

2010-05-27 09:58:59 2226

2226

帧存 是图形显示系统的核心部件之一,帧存的设计关系到系统的整体性能。介绍了一种高速图形帧存的设计方法。该高速帧存采用SRAM作为存储体,应用 FPGA实现双帧存交替切换、上电清

2011-07-13 17:57:47 95

95 随着微电子和半导体技术的发展,DSPs已运用在了众多领域。由于DSPs的强大数字信号处理能力,越来越受到开发人员的青睐。

2011-08-16 10:51:22 1223

1223

本内容详细介绍了基于DSPs的系统开发过程

2011-09-29 17:28:18 136

136 基于高速FPGA 的PCB 设计技巧 如果高速PCB 设计能够像连接原理图节点那样简单,以及像在计算机显示器上所看到的那样优美的话,那将是一件多么美好的事情。然而,除非设计师初入P

2012-05-15 11:26:34 0

0 恒颐基于ARM+FPGA的高速同步数据采集方案,解决了数据采集的同步性问题,与以往的数据采集方案相比,具有高精度、高速率、多参数同步测量、实时处理、网络传输不受区域限制等特点

2012-11-27 10:51:24 1198

1198 TCAM在高速路由查找中的应用及其FPGA实现,TCAM在高速路由查找中的应用及其FPGA实现

2015-11-04 16:32:39 15

15 TMs320C6000系列DSPs原理与应用

2016-05-09 10:59:26 48

48 基于FPGA的高速DMUX设计,下来看看

2016-05-10 11:49:02 16

16 基于FPGA的高速A_D转换控制器设计。

2016-05-10 13:45:28 30

30 基于FPGA的高速数据采集硬件系统设计.

2016-05-10 17:06:40 43

43 基于FPGA的高速数据采集系统接口设计.

2016-05-10 17:06:40 27

27 基于FPGA的高速数据采集系统的设计,下来看看

2016-05-10 17:06:40 19

19 基于FPGA的通用高速串行互连协议设计。

2016-05-11 09:46:01 18

18 基于FPGA高速数据采集的解决方案,下来看看

2016-05-11 09:46:01 13

13 基于FPGA的高速数据采集系统设计,用ad芯片和sdram构成高速数据采集系统。

2016-05-17 09:49:51 35

35 基于FPGA的多通道高速CMOS图像采集系统

2016-08-30 15:10:14 8

8 基于FPGA的高速图像采集系统的研究与设计

2016-08-30 15:10:14 6

6 基于FPGA的高速固态存储器优化设计_杨玉华

2017-01-13 21:40:36 1

1 基于FPGA的高速多通道AD采样系统的设计与实现_徐加彦

2017-01-18 20:23:58 12

12 (Xilinx)FPGA中LVDS差分高速传输的实现

2017-03-01 13:12:04 64

64 基于双DSP和双FPGA的高速图像处理系统设计_吴雷

2017-03-16 09:28:51 2

2 采用FPGA实现对AD 输出数据的高速采集

2017-08-30 17:16:02 35

35 基于FPGA和DSP的高速图像处理系统

2017-10-19 13:43:31 19

19 提出了基于Xilinx公司Virtex-5系列FPGA中RocketIO GTP收发器设计的一个高速串行传输实现方案,详细阐述了硬件设计要点和软件实现概要,系统实测表明,该方案能在某信号处理系统两个板卡之间稳定地进行1.6 Gb/s的数据传输,误码率优于10e-12,传输距离大于1米。

2017-11-21 10:16:00 7689

7689 复接器设计方案。该方案能够实现高速载荷数据接收合路、NAND flash大容量数据存储控制、数据复接,数据信道低密度奇偶校验编码(LDPC)等功能。设计过程中对电路进行优化,实现了高速并行数据处理和高可靠性目标。通过FPGA的原型验证,本方案设计

2018-04-03 15:23:30 0

0 DSPs处理器在复位后起始阶段,把程序从外部慢速、窄位的存储器自动加载到片上的高速、宽位的程序存储器中执行,这种程序加载的方式称为程序自加载(Boot_root)。

2018-04-09 16:57:17 5

5 本文提出了一种实现信号采集方案,介绍了由ARM 处理器S3C2410 和EP2C8 FPGA 组成的高速信号采集系统的系统设计,并着重介绍前端硬件的设计,并就ARM 处理器和FPGA 的互联设计进行探讨。利用FPGA 硬件控制A/D 转换,达到了较好的效果,实现了信号的采集与存储。

2018-11-02 15:46:01 10

10 在FPGA高速AD采集设计中,PCB布线差会产生干扰。今天小编为大家介绍一些布线解决方案。

2019-03-07 14:52:24 6086

6086 本文档的主要内容详细介绍的设计DSPs硬件开发的学习教程课件免费下载包括了:1.DSPs硬件系统组成,2.DSPs芯片的选择,3.DSPs最小系统设计,4.DSPs的结构及外设接口,5.DSPs系统设计

2019-06-27 08:00:00 7

7 基于FPGA的高速大容量FLASH存储(单片机底层嵌入式开发)-该文档为基于FPGA的高速大容量FLASH存储总结文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-07-30 16:46:45 12

12 系统架构确定,下一步就是FPGA与各组成器件之间互联的问题了。通常来说,CPU和FPGA的互联接口,主要取决两个要素。

2022-10-08 11:37:08 1749

1749 直播主题 Molex莫仕 高速互联电缆测试验证方案 直播时间 2023年9月20日(周三)1400 立即预约 长按识别上方二维码 直播福利 · 现场互动,讲师现场解答并送小礼品 · 直播中不定时抽奖

2023-09-13 15:10:06 328

328

FPGA技术的发展,大容量、高速率和低功耗已经成为FPGA的发展重点,也对FPGA测试提出了新的需求。本文根据FPGA的发展趋势,讨论了FPGA测试面临哪些挑战?测试方案是什么? FPGA处于高速发展期 FPGA技术正处于高速发展时期。目前其产品的应用领域已经扩展到

2023-10-23 15:20:01 460

460

正在加载...

1917

1917 1917

1917

电子发烧友App

电子发烧友App

评论