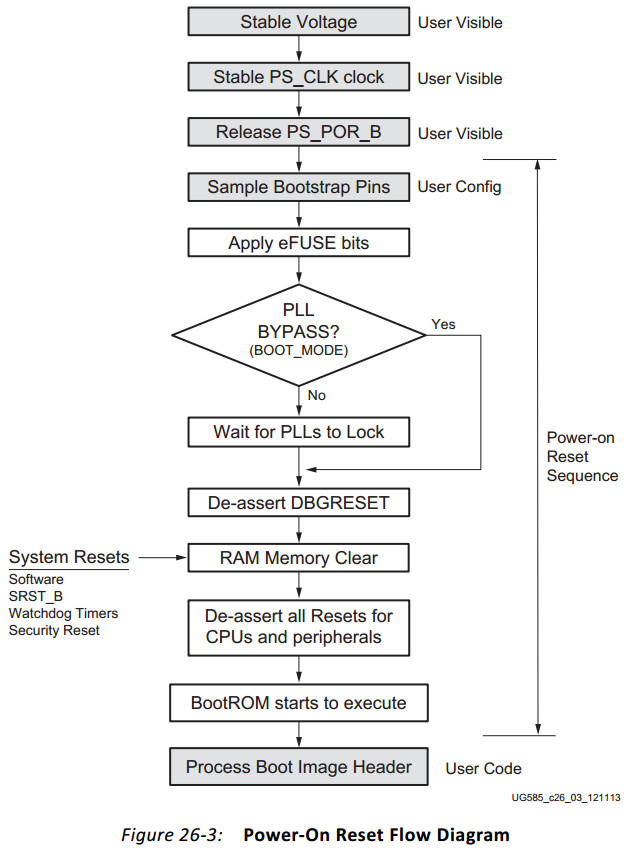

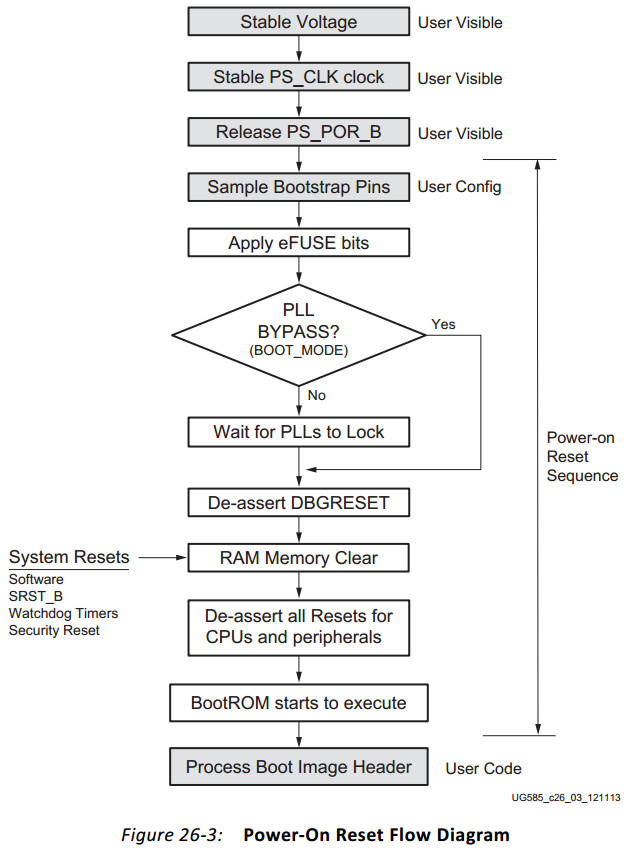

本文主要介绍zynq启动过程,主要包括BootROM和FSBL等的执行过程。 硬件启动过程 1. 重新上电或POR复位后进行硬件启动过程 2. 扫描启动引脚设置,并存入只读寄存器

2020-11-23 14:53:52 8313

8313

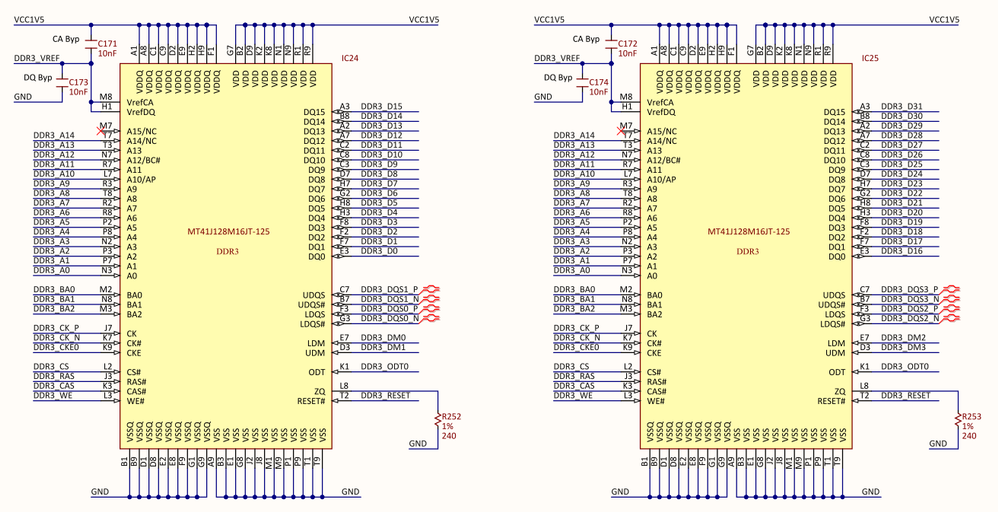

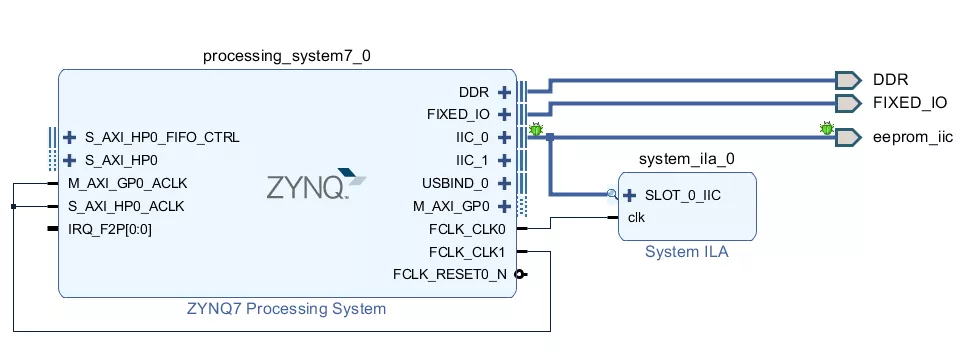

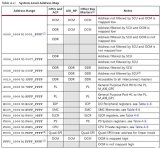

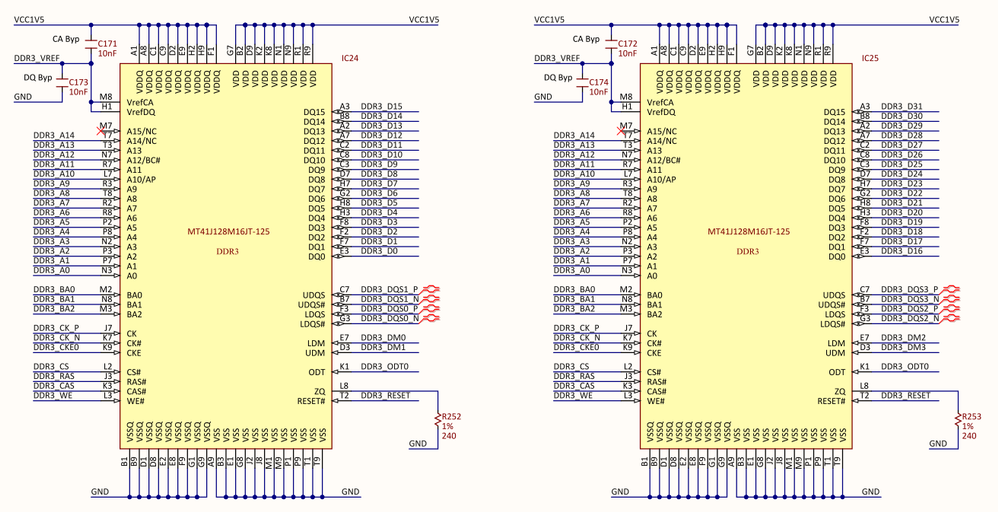

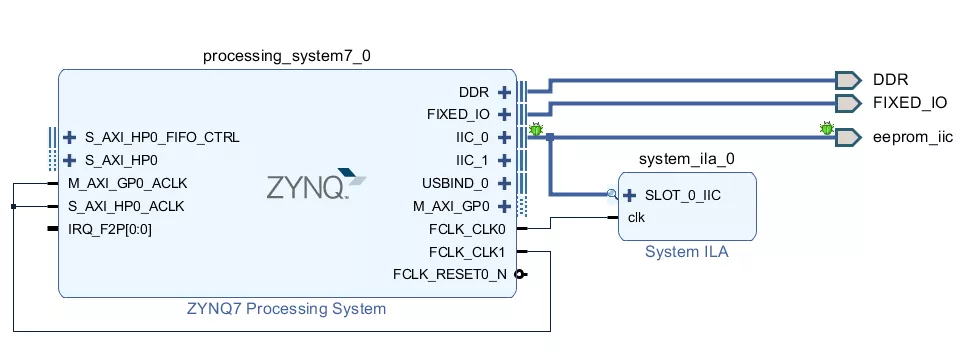

Controller接口,如果外部硬件连接了DDR器件,于是在ZYNQ Processing System中正确配置了相应的信号和参数后,DDR就可以成为ZYNQ的内存,在SDK中可以直接使用memcpy

2020-11-27 12:18:15 6687

6687

基于zynq7020器件来搭建Linux系统,描述搭建Linux系统过程中PL侧的配置以及对u-boot,kenel,桌面系统的配置和

2020-11-30 11:56:01 3490

3490

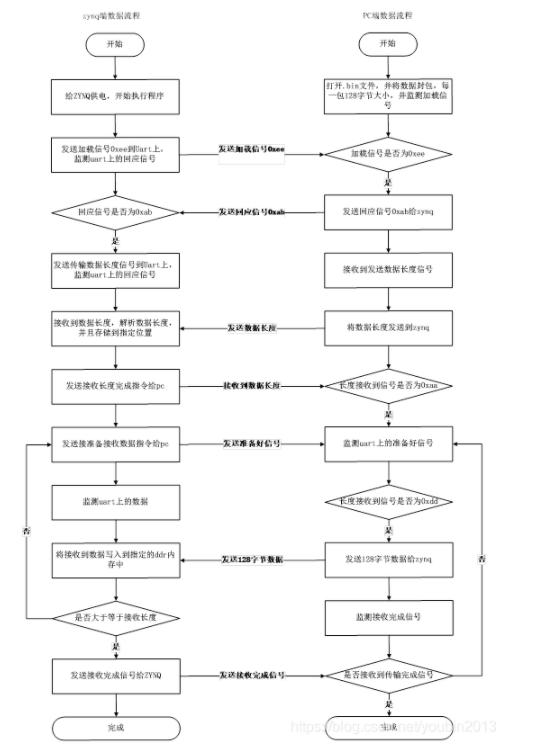

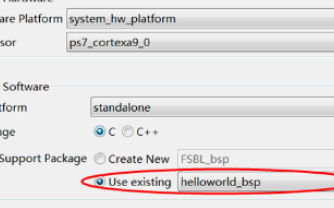

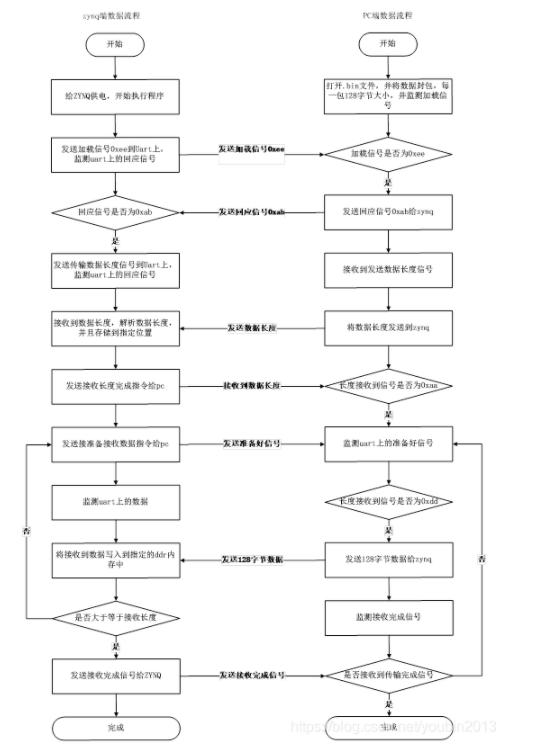

加载方法 ZYNQ的启动镜像是由FSBL程序(bootloader),PL配置文件(硬件比特流文件),应用层软件三个部分组成,其通过SDK的软件生成工具把三个部分按规定的格式拼凑成一个.bin文件

2020-12-05 10:15:37 4952

4952

Zynq可扩展处理平台是赛灵思新一代 FPGA的可编程技术的产品系列。与采用嵌入式处理器的FPGA不同,Zynq产品系列的处理系统不仅能在开机时启动,而且还可根据需要配置可编程逻辑。采用这种方法

2020-12-25 14:15:48 5212

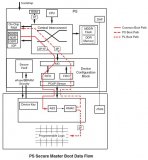

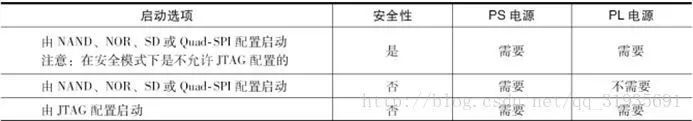

5212 Zynq-7000AP SOC器件有效利用了片上CPU来帮忙配置,在没有外部JTAG的情况下,处理系统(PS)与可编程逻辑(PL)都必须依靠PS来完成芯片的初始化配置。 ZYNQ的两种启动模式:从BootROM主动启动,从JTAG被动启动。

2023-08-02 09:33:09 736

736

在 AMD SoC 器件(AMD Zynq 7000 SoC,AMD Zynq UltraScale+ MPSoC,AMD Versal Adaptive SoC),常见的启动方式是通过加载外部

2023-12-22 10:27:25 506

506

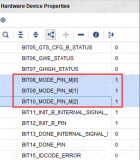

51一样应用,那么你可以参考一下。参考文章EBAZ4205 ZYNQ 7Z010 裸机程序NAND固化 JTAG调试方法如果本文有地方写的不清楚可以跳转过去看下。本文主要是硬件改动,软件烧录与测试方法与参考文章并无区别。可以先看完本文的硬件改动后再看参考文章,改动的地方主要是原理图中标红色框的这两个电阻(

2022-01-06 07:52:41

User Defined文件夹处右击,并在弹出的菜单中点击“New Target Configuration”新建目标配置文件:在打开的目标配置文件中,需要配置仿真器类型、器件型号,我们实验用的仿真器为

2023-02-21 14:51:50

本帖最后由 一语奔驰 于 2016-11-25 15:18 编辑

我ZYNQ外接的PHY是88E1512,现在有一个系统,外接的是88E1510的PHY,但是我想使用88E1512来实现光口

2016-11-25 14:21:28

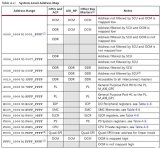

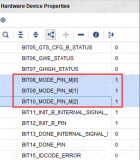

ZYNQ 分为 PS 和 PL 两部分,那么器件的引脚(Pin)资源同样也分成了两部分。ZYNQ PS 中的外设可以通过 MIO(Multiuse I/O,多用输入/输出)模块连接到 PS 端的引脚

2022-02-08 07:27:16

XinesC6657.gel。设置完Gel文件后,点击Save: 1.1.3.2.2.2 启动目标配置文件在已经创建并设置好的目标配置文件处右击,并在弹出的菜单中点击Launch Selected Configuration

2023-02-02 21:43:20

说一下配置的过程,如何从PDF中拿出参数来首先看一下Zynq MPSoC支持的DDR,这里的手册是UG1085,首先是最大支持多少

2022-04-19 17:56:03

Zynq®UltraScale+™MPSoC USB 3.0控制器由两个独立的双角设备(DRD)控制器组成。两者都可以单独配置为在任何给定时间用作主机或设备。USB 3.0 DRD控制器通过高级可

2019-01-03 09:59:50

与内置于 TE0720 系列 Trenz Electronic SoM(采用 Zynq Z-7014S 和 Zynq Z-7020 器件)中的 FPGA 容量相比,集成到 TE0723-03M

2018-08-31 14:43:05

是怎样实现对自己的配置? 这也是本文将要和大家共同讨论的问题。 Zynq的启动流程 在无 JTAG 的模式下,Zynq 是通过片上CPU完成对芯片的配置,也就是PS和PL的配置是通过 PS 处理器

2021-01-08 16:33:01

本文主要与大家分享了Zynq在非JTAG模式下的启动配置流程,旨在让大家对Zynq的三阶段启动模式有一个具体的认识,希望大家多多交流。

2021-03-17 07:36:30

为了确保正确回退到金启动,AR#67221规定QSPI闪存的D2和D3数据条应连接到4K7上拉。但是看看Zynq xc7z030fbg676,这些引脚也可用作配置模式引脚。QSPI D2 =模式引脚

2020-06-09 17:24:31

各位i大神,小弟最近遇到了zynq上无法启动linux的问题,不知道哪里的错误都是按照xilinx官网做的。。thanks

2014-07-07 12:40:30

你好我想制作一个具有中断信号的自定义IP。我正在寻找这个中断信号的规格。我在哪里可以找到这个规格?例如水平或边缘检测器如果它是水平检测器,它应该停留多长时间?我正在使用ZYNQ ZC706板。如果你

2019-04-10 11:49:23

zynq是xilinx的新一代的嵌入ARM硬核的SOC,请问1、这种FPGA器件相对以往传统FPGA有哪些优势和劣势?2、针对图像和视频处理的,这两类哪一种器件更适合?3、相同价格的情况下,ARM硬核的引入相比传统FPGA是否会降低zynq的性价比和灵活度?

2022-11-07 15:28:45

Zynq-7000 AP SoC ZC706 XC7Z045 Zynq®-7000 FPGA + MCU/MPU SoC 评估板

2024-03-14 20:42:29

Xilinx-ZYNQ7000系列-学习笔记(3):系统复位与启动一、复位ZYNQ-7000 SoC系统中的复位可以由硬件、看门狗定时器、JTAG控制器或软件产生,可用于驱动系统中每个模块的复位信号

2022-01-25 07:05:36

大家好,我正在与SoC迈出第一步,我目前正在使用Zybo Zynq开发板。我有一个简单的问题:是否可以创建多个设备配置,为每个配置生成比特流并将比特流存储在内存或其他内容中,以便创建一个说“配置库

2020-05-20 10:44:19

因为最近要用到zynq芯片,我希望能在zynq芯片上使用freeRTOS,但是弄不明白怎么移植进去。一般xillinx sdk在工程里面添加操作系统的方法是,在repository里先安装相应的库

2020-06-11 04:35:29

大家好,我使用zynq 7020开发板,其自定义架构不支持SD卡,但支持QSPI闪存。我通过在SDK中使用以下bif文件创建zynq启动映像来构建.msc文件 [bootloader] zynq

2020-07-30 16:24:39

Zynq-7000 Extensible Processing Platform,是一个可扩展处理平台,简单说就是有个FPGA做外设的A9双核处理器。所以,它的启动流程自然也和FPGA完全不同,而与

2015-07-22 20:42:50

做一遍也不害怕!Zynq7000,是一个可扩展处理平台,简单说就是有个FPGA做外设的A9双核处理器。所以,它的启动流程自然也和FPGA完全不同,而与传统的ARM处理器类似。Zynq7000支持从多种设备

2015-05-27 20:50:06

使用source命令执行petalinux的环境配置脚本settings.sh,如下所示:source /home/zynq/petalinux/v2018.3/settings.sh图 31.1.2 运行

2020-09-15 15:24:44

Xilinx官方ZYNQ EVK开发板对应的Linux内核,发现其不可以在正点原子的ZYNQ开发板上启动,所以本节我们就参考Xilinx EVK开发板的设置,修改相应的配置使其在正点原子的领航者开发板上能启动

2020-09-14 15:42:54

1、ZYNQ调试时内存读写的一般方法假设查看的数据从地址0x0开始,大小为4个字节。打开示例工程并启动调试。在菜单栏选择Window->Show View->Memory打开内存视图。原作者: 嵌入式男单第九名 刘广信

2022-07-05 15:30:17

嗨,PCIe-Spec定义在稳定供电后100ms,PCIe设备必须为链路训练做好准备。使用7系列Zynq设备无法达到此时间。我使用了两种方法来减少启动时间: - 优化FSBL以达到SPI控制器的最大

2020-06-09 16:42:15

大家好,有没有一种简单的方法可以使用IMPACT(ISE)将比特流下载到Zynq设备中而无需启动ARM?我知道这可以用Vivado完成。TIA

2020-07-21 15:11:31

[/td][td]关于zynq启动的问题,求达人解答![img][/img]查阅了些资料,发现zynq是分部启动的。1)其中arm部分是否可以软重启,自己收到复位命令后进行从新加载PS部分;2)有

2013-08-23 10:49:00

如何使用Windows在Zynq 7000主板上启动linux?在Linux中我有终端可以请你建议是否有任何Windows终端以上来自于谷歌翻译以下为原文How can I boot linux

2019-04-09 13:12:21

`玩转Zynq连载1——Zynq的linux启动过程更多资料共享 链接:https://share.weiyun.com/5s6bA0s1概述 简单的,以ug585中的一张图来看,从大的方面说

2019-04-16 06:56:32

`玩转Zynq连载22——[ex03] 基于Zynq PL的PLL配置实例更多资料共享腾讯微云链接:https://share.weiyun.com/5s6bA0s百度网盘链接:https

2019-09-06 08:13:18

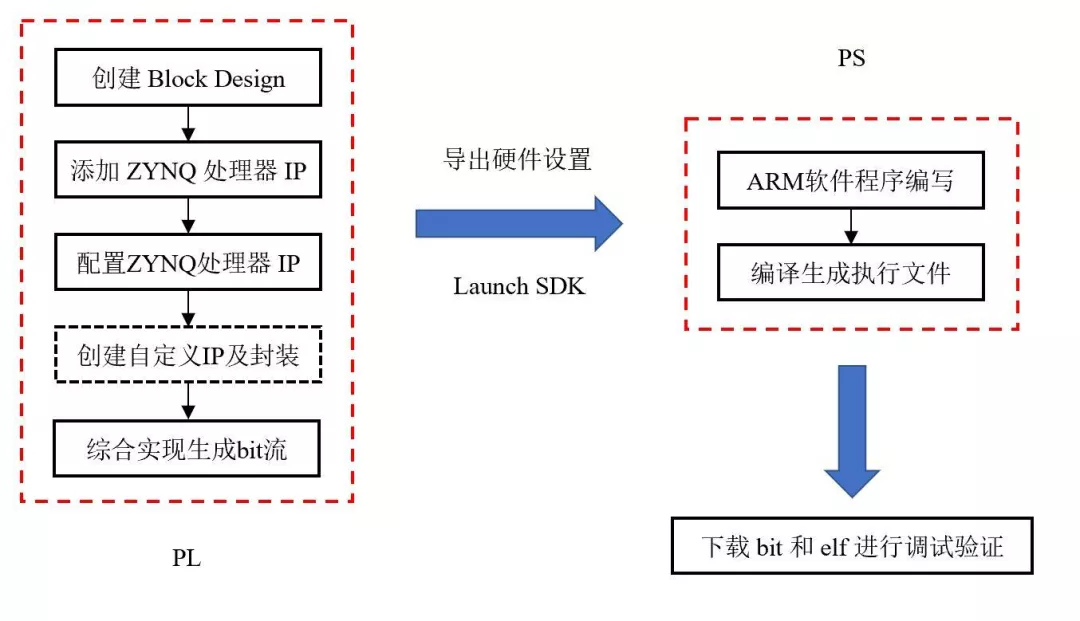

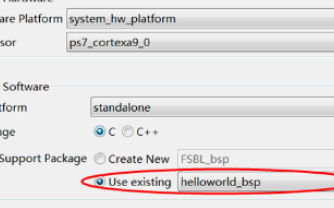

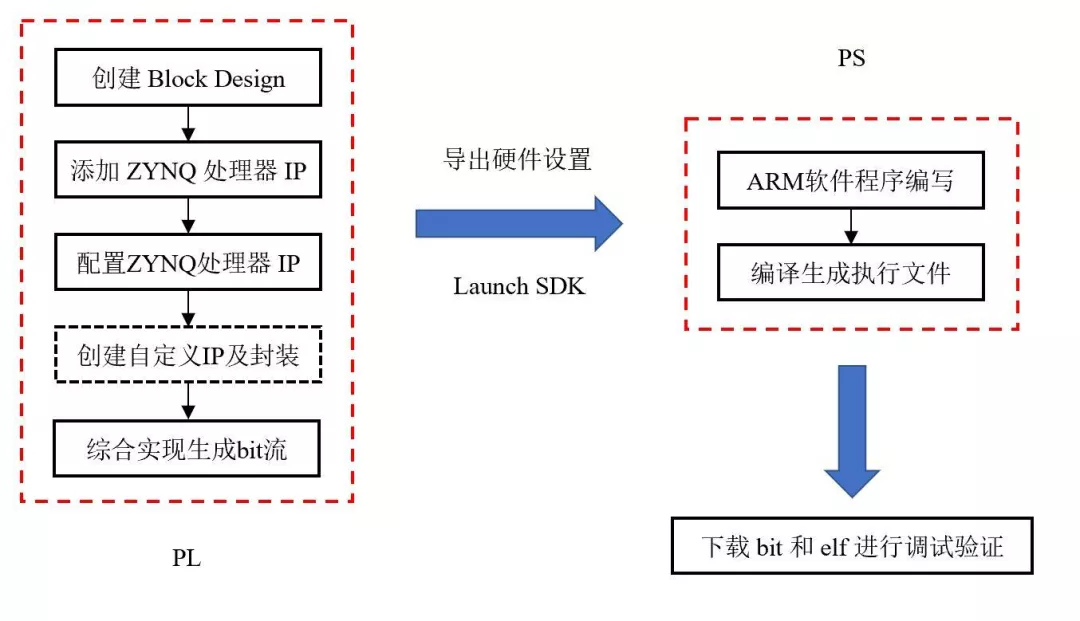

Zynq,而是如何新建Zynq系统模块、配置PS的参数、导出硬件、新建软件工程并且在线板级运行起来。流程很重要,大家在开始的时候总要先走一遍流程了解开发的全貌,然后再细细把玩,逐个精通。 2 新建

2019-09-30 12:57:32

Zynq的启动原理,建议参考文档《玩转Zynq-基础篇:Zynq的启动过程.pdf》。 2 导出硬件信息并启动SDK参考文档《玩转Zynq-工具篇:导出PS硬件配置和新建SDK工程》。 3 创建FSBL工程

2019-09-30 14:11:59

喜如何用zqq的irq no 52到MIO26(gpio中断)引脚配置中断线?我正在使用以下devicetree配置i2c1:i2c @ e0005000 {compatible =“cdns

2020-04-24 09:43:51

我正在使用zynq芯片和VIRTEX-7设计电路板。我想知道在Zynq PL引脚和Virtex-7 IO引脚之间选择配置数据线(例如Slave SelectMAP X8,X16,X32)的方法。在

2020-06-05 10:31:19

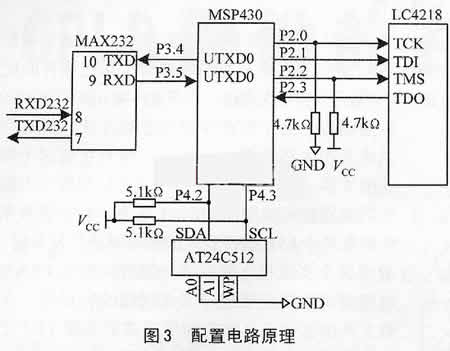

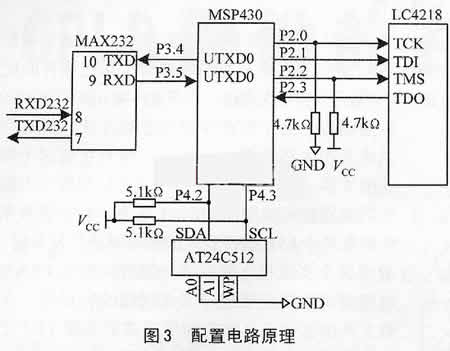

摘要:介绍基于SRAM LUT结构的FPGA器件的上电配置方式;着重介绍采用计算机串口下载配置数据的方法和AT89C2051单片机、串行EEPROM组成的串行配置系统的设计方法及实现

2006-03-13 19:36:49 448

448 以下是引用片段: 摘要: 介绍一种利用微控制器动态配置CPLD器件的方法。将配置文件存放在存储器中,配置文件中的控制代码驱动在微处理器中运行的配置引擎;将配置文件中的配置信息通过JTAG口移入

2009-06-20 10:44:21 3034

3034

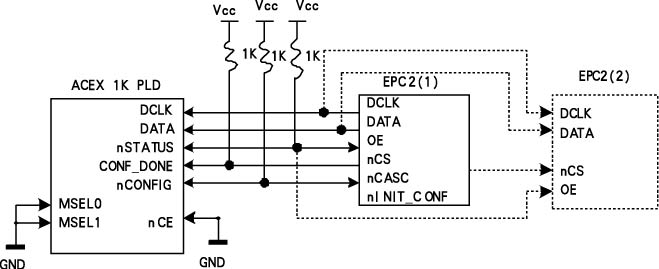

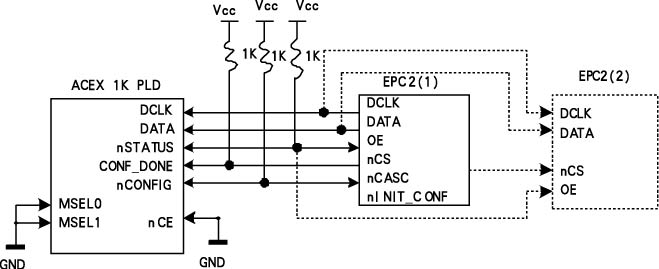

摘 要 :介绍ACEX 1K系列器件的配置方法,对几种方法进行了分析对比,并着重论述了应用配置器件配置 ACEX 1K系列器件的优点。

关键词 :CPL

2009-06-20 10:51:54 478

478

摘要: 介绍基于SRAM LUT结构的FPGA器件的上电配置方式;着重介绍采用计算机串口下载配置数据的方法和AT89C2051单片机、串行EEPROM组成的串行配置系统的设计方法及

2009-06-20 10:57:26 1062

1062

Realview MDK不仅提供了默认的启动代码,而且这些启动代码可以通过图形化界面配置。启动代码的图形化配置界面非常类似于Web网页的界面,甚至后台处理的脚本也与Html语言十分接近。下面将详细的解析图形化界面的设计与配置。 启动代码的配置界面是由程序中的

2011-02-24 16:06:53 86

86 FPGA Cyclone器件中PLL的配置方法

2016-02-23 11:04:13 5

5 网络资料收集,关于启动流程的一些注意点,关于开发板ZYNQ系列的包括MIZ702

2016-05-11 17:30:15 3

3 基于单片机的复杂可编程逻辑器件快速配置方法

2017-01-18 20:35:09 8

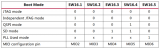

8 今天,赛灵思 Zynq-7000 SoC 和 Zynq UltraScale+ MPSoC 迎来一个新的产品系列及三款最新器件! 新的产品系列被称为Zynq Z-7000S系列,三款新器件分别为

2017-02-08 04:25:13 517

517

作者:Hello,Panda Part 2 : Zynq UltraScale+ MPSoC启动 熊猫君在这里讨论启动(Boot),主要是想聊它的启动设备和启动方式。看看启动设备是否广泛支持,启动

2017-02-08 08:31:11 358

358

作者:Hello,Panda Part 2 : Zynq UltraScale+ MPSoC启动 熊猫君在这里讨论启动(Boot),主要是想聊它的启动设备和启动方式。看看启动设备是否广泛支持,启动

2017-02-08 08:31:11 339

339

在《ZYNQ-7000使用总结(3)——PS和PL部分配合使用》中,我们已经可以将PL与PS部分一起使用,并且通过JTAG下载到板子运行。对于ZYNQ,有多种启动方式,比如从JTAG启动、从QSPI

2019-10-06 16:48:00 2095

2095

在电子系统设计中,无任是用CPU作为系统的主要器件,还是用FPGA作为系统的主要器件,系统设计中首先要考虑到的问题就是处理器的启动加载问题。

2018-07-12 08:27:00 9919

9919

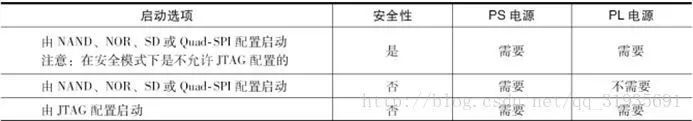

ZYNQ 7系列所有可编程器件均可以在安全模式下通过静态存储器配置或者在非安全模式下通过JTAG或者静态存储器配置。 (1)JTAG模式主要用于开发和调试 (2)NAND、并行NOR、串行NOR

2017-11-17 10:25:52 22027

22027

ZYNQ7000与传统FPGA有着巨大的差异,它将自己定位为一款All Programmable Soc(软硬件可编程片上系统),视其为以FPGA作为外设的双核ARM A9处理器更加准切。它的启动

2017-11-17 16:04:37 7989

7989 Zynq系列器件。如果是Mircroblaze器件请忽略。产生的“.BIN”启动文件可以利用(PROM programmer)拷贝到Flash或直接拷贝到SD第一个FAT分区。

2017-11-21 11:41:15 968

968 基于Zynq器件的嵌入式开发时,我们不可避免地需要规划设计使用什么样类型和多大地内存与FLASH,本文就ZYNQ器件的存储控制器作一个抛砖引玉的描述,以期大家对它有个基本了解,如有不当或需要补充之处

2017-11-22 08:23:54 6195

6195

Zynq™-7000 All Programmable SoC在单个器件上实现了ARM处理功能与FPGA逻辑独特的组合,因此需要双重的配置过程,同时需要考虑处理器系统和可编程逻辑。工程师会发

2018-01-12 11:17:15 5494

5494 本文试图搞清楚在 Xilinx 基于 ARM 的 Zynq-7000、Zynq UltraScale+ MPSoC 和 Zynq UltraScale+ RFSoC 器件中是否存在任何漏洞。

2018-06-28 15:53:00 2492

2492 ZYNQ-7000如何生成从Flash和SD卡启动的镜像文件 将PL与PS部分一起使用,并且通过JTAG下载到板子运行。对于ZYNQ,有多种启动方式,比如从JTAG启动、从QSPI(即Flash

2018-05-28 11:42:14 5883

5883

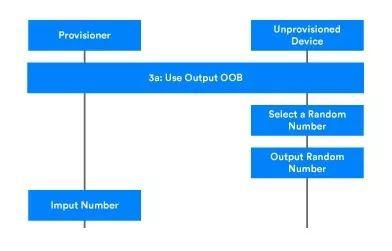

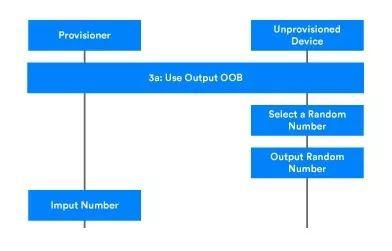

1、发送Beacon信号:如果未经启动配置的设备支持PB-ADV承载层,则其作为未经启动配置设备Beacon进行广播;如果使用的是PB-GATT承载层,则发送可连接的广播数据包。这就向启动配置设备(Provisioner)表明未经启动配置的设备已做好准备,可进入启动配置流程。

2018-09-28 08:22:00 5578

5578

在本视频中,我们将学习如何使用Xilinx SDK启动电路板,利用每个驱动程序提供的应用示例并测试各种外设。

我们将详细介绍Zynq DRAM测试,并了解如何利用它进行测试。

2018-11-29 06:50:00 4666

4666 了解如何配置和练习U-Boot的USB主机功能。

这允许在Zynq上使用USB记忆棒进行数据存储和检索,包括二次启动。

2018-11-29 06:38:00 2554

2554 了解设计人员在使用Zynq-7000 All Programmable SoC器件时可用的不同I / O,从标准I / O到串行收发器以及模拟输入。

2018-11-26 06:36:00 2547

2547 了解Xilinx FSBL如何操作以启动Zynq器件。

包括程序执行概述,调试技巧以及有关特定引导设备的信息。

还包括FSBL角度的启动安全性简要概述。

2018-11-23 06:32:00 4237

4237 ZYNQ-7000如何生成从Flash和SD卡启动的镜像文件 将PL与PS部分一起使用,并且通过JTAG下载到板子运行。对于ZYNQ,有多种启动方式

2018-12-01 08:38:18 7278

7278

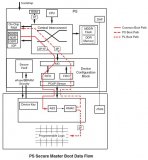

在ps的控制下,可以实现安全或非安全的配置所有ps和pl。通过zynq提供的JTAG接口,用户可以在外部主机的控制下对zynq进行配置,zynq不支持最开始就配置pl的过程。

2019-05-15 11:41:31 7190

7190

本文主要介绍zynq启动过程,主要包括BootROM和FSBL等的执行过程。

2019-10-27 10:47:16 6952

6952

ZYNQ是一个可扩展平台,就是有FPGA作为外设的A9双核处理器,它的启动流程与FPGA完全不同,而与传统的ARM处理器类似,ZYNQ的启动配置需要多个处理步骤。

2020-12-05 10:48:58 5388

5388 Xilinx 用两个 96 位独特器件标识符(称为器件 DNA)为每个 Zynq UltraScale+ 器件编程。一个 DNA 值位于可编程逻辑 (PL) 中,另一个 DNA 值位于处理系统 (PS) 中。这两个 DNA 值是不同的,但每个 DNA 都有以下属性及读取访问方法。

2022-02-08 14:19:49 1149

1149

初学 Zynq 的时候,都是按照惯例打开 Vivado 软件,然后实现 Zynq 可编程逻辑硬件部分PL的设置后,把硬件部署导出,再打开 SDK 进行 ARM 核的软件部分 PS 编程设计,最后再将

2022-02-08 11:48:37 1021

1021

初学 Zynq 的时候,都是按照惯例打开 Vivado 软件,然后实现 Zynq 可编程逻辑硬件部分PL的设置后,把硬件部署导出,再打开 SDK 进行 ARM 核的软件部分 PS 编程设计,最后再将

2021-01-26 07:30:29 20

20 。如图2.1所示,在相对较高层次对比了三种器件。Zynq MPSoC的PS部分比Zynq的PS部分面积更大,也更复杂。本章,将介绍这三种器件的特点。 2.1 技术时间线 进一步介绍之前,需要指出这三种

2021-04-02 17:20:14 13783

13783

在本篇博文中,我们将探讨如何在 Vitis 中调试 Zynq UltraScale 器件启动镜像。这些启动镜像包括 ARM 可信固件 (ATF) 和 U-boot。 本篇博文乃是系列博文中

2021-06-01 15:35:45 2709

2709

为处理海量数据、复杂算法、超低延时的应用提供数字化加速驱动力是赛灵思一直的目标,为此,赛灵思研发 Bootgen 工具支持将二进制文件缝合在一起并生成器件启动镜像。定义了多个属性和参数作为创建启动

2021-08-27 14:11:30 2832

2832 FPGA CPLD可编程逻辑器件的在系统配置方法(深圳市村田电源技术有限公司)-FPGA CPLD可编程逻辑器件的在系统配置方法

2021-09-18 10:51:20 13

13 功耗域2.2 低功耗域2.3 全功耗域2.4 PL功耗域2.5 PMU一、电源优化方法相对于上一代Zynq器件,Zynq UltraScale+更加...

2021-11-06 21:06:04 6

6 在 Xilinx Zynq 器件中,硬件可编程逻辑 PL 是作为一项外设挂载在 ARM 处理器系统中的,那么 PL 硬件的配置自然也就由处理器负责。本文...

2022-02-07 11:18:27 1

1 ZYNQ7000 SOC 芯片可以从 FLASH 启动,也可以从 SD 卡里启动, 本节介绍程序 FLASH 启动的方法。Zynq7000 SOC 芯片上电后,最先运行的是ARM端系统(PS

2022-05-07 09:41:35 5019

5019 普通的 FPGA 一般是可以从 flash 启动,或者被动加载,但是ZYNQ不行,ZYNQ必须PS端参与

2022-07-22 10:10:02 5209

5209 Zynq MPSoC是Zynq-7000 SoC(之后简称Zynq)的进化版本。Zynq是赛灵思发布的集成PL(FPGA)和PS设计的最早的一代产品。如图2.1所示,在相对较高层次对比了三种器件。Zynq MPSoC的PS部分比Zynq的PS部分面积更大,也更复杂。本章,将介绍这三种器件的特点.

2022-08-15 09:16:38 1629

1629 在无 JTAG 的模式下,Zynq 是通过片上CPU完成对芯片的配置,也就是PS和PL的配置是通过 PS 处理器 ARM 核来实现的。需要注意的是,与传统的 Xilinx 7 系列 FPGA 芯片不同,Zynq 是不支持从 PL 端进行直接启动配置的,一定要通过 PS 部分来完成。

2022-10-19 09:11:55 986

986 FPGA器件配置方式分三大类:主动配置、被动配置和JTAG配置。 主动配置:由FPGA器件引导配置操作过程。 被动配置:由计算机或控制器控制配置过程。上电后,控制器件或主控器把存储在外部存储器

2022-11-17 12:15:10 1141

1141 介绍一下Xilinx公司的新一代Zynq UltraScale+ RFSoC器件,可用于LTE、5G、SDR、卫星通信等无线平台。

2023-05-22 10:38:59 3966

3966

本文介绍使用Xilinx SDK软件查看当前Zynq SoC启动模式的步骤

2023-07-07 14:15:00 1179

1179

在 “ 什么是软启动?软启动时间?启动时间?”文章中,我们简述了为开关电源配置一个最小的软启动时间,至少可以获得两个好处。

2023-07-23 10:35:06 1102

1102

电子发烧友网站提供《Zynq UltraScale+ MPSoC中的隔离方法.pdf》资料免费下载

2023-09-13 17:11:48 1

1 电子发烧友网站提供《Zynq-7000 SoC的安全启动应用说明.pdf》资料免费下载

2023-09-13 11:46:04 1

1 电子发烧友网站提供《Zynq UltraScale+器件封装和管脚用户指南.pdf》资料免费下载

2023-09-13 10:30:45 1

1 Zynq器件将arm和FPGA结合,利用了两者各自的优势,arm可以实现灵活的控制,而FPGA部分可以实现算法加速,这大大扩展了zynq的应用。比如深度学习加速,图像处理等等。PL侧表示FPGA的逻辑部分,PS侧为arm端以及一些AXI接口控制部分,二者实际上通过AXI接口实现通信和互联。

2023-11-09 11:28:04 1460

1460

正在加载...

8313

8313 8313

8313

6687

6687 6687

6687

3490

3490 3490

3490

4952

4952 4952

4952

5212

5212 5212

5212 736

736 736

736

506

506 506

506

电子发烧友App

电子发烧友App

评论