谁需要4核系统? 毫无疑问,4核处理器由于性能非常高,所以主要应用在服务器上,企业级应用成为了多核产品的主战场。目前,双核已经成为服务器系统的标准配置。惠普公司在所有的服务器产品线中,包括机架、塔式

2019-06-21 06:54:58

自从AMD率先在x86领域推出双核心处理器以来,多核就成为处理器企业争夺的一个焦点。2006年11月,英特尔先于AMD发布了4核处理器。当时,双核与单核之争正在激烈进行中。不少人曾感慨,双核尚未普及

2019-06-19 07:09:55

处理器是F28335 CCSv4void foo()[static uint64_t sum_A;sum_A = 1326 * 1326;]得到的结果不对而必须对1326 进行强制转换 且 sum_A 必须放到函数外部处理器核的寄存器是16位的吗? 那sum_A也必须成为全局变量?

2020-06-10 09:12:01

处理器中断处理的过程是怎样的?处理器在读内存的过程中,CPU核、cache、MMU如何协同工作?

2021-10-18 08:57:48

Cortex-R52+处理器是一款中等性能的有序超标量处理器,主要用于汽车和工业应用。

它还适用于各种其他嵌入式应用,如通信和存储设备。

Cortex-R52+处理器有一到四个内核,每个内核实现一个

2023-08-29 07:33:50

ARM公司开发了很多系列的ARM处理器核,目前最新的系列已经是ARM11了,而ARM6核及更早的系列已经很罕见了,ARM7以后的核也不是都获得广泛应用。目前,应用比较多的是ARM7系列、ARM9系列

2019-07-23 07:08:18

ARM处理器中断处理的编程是怎么实现的?

2021-04-27 06:46:53

ARM处理器是一个32位元精简指令集(RISC)处理器架构,其广泛地使用在许多嵌入式系统设计。ARM全称为Acorn RISC Machine。ARM处理器本身是32位设计,但也配备16位指令集

2021-08-23 07:45:05

请教:ARM多核处理器中不同的核是否可配置为纯REE环境和(REE+TEE)或纯TEE环境?实现“不同CPU核的REE与TEE同时并行运行,并相互通信”?(手机上是否就这样做的?)谢谢。

2022-09-05 15:55:30

瑞芯微RK3066芯片手册!A9双核处理器1.6GHZ!由于文件比较大,需要的话请发邮件向我要@lishengsdx@qq.com!我会发给你!

2013-03-02 21:43:50

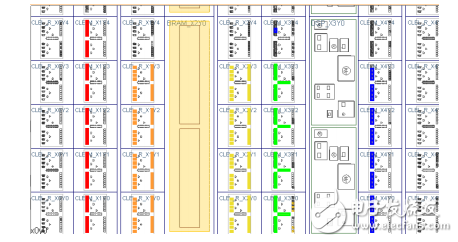

FPGA实现高速FFT处理器的设计介绍了采用Xilinx公司的Virtex - II系列FPGA设计高速FFT处理器的实现方法及技巧。充分利用Virtex - II芯片的硬件资源,减少复杂逻辑,采用

2012-08-12 11:49:01

可编程逻辑业对微处理器核的报道层出不穷,包括与ARM和MIPS的协议,这些讨论已经持续了数年。然而,讨论的主题大体上没什么改变,诸如采用硬核还是软核?采用供应商的特定标准还是行业标准?这些核如何用来全方位地支持生态系统?如何根据成本、功耗和性能来选择微处理器?如何根据应用来选择核?

2019-08-08 06:43:03

设计RISC微处理器需要遵循哪些原则?基于FPGA技术用VHDL语言实现的8位RISC微处理器

2021-04-13 06:11:51

FPGA硬核与软核处理器有什么区别和联系?

2023-05-30 20:36:48

数据传输效率低,这将严重影响产品的性能;而如果采用高速并口,则占用管脚多,硬件成本将会增加。为解决这一痛点,各大芯片公司陆续推出了兼具A核和M核的多核异构处理器,如NXP的i.MX8系列、瑞萨的RZ

2022-11-21 09:45:10

)作为一种特殊的嵌入式微处理器系统,已逐渐成为一个新兴的技术方向。SOPC融合了SoC和FPGA各自的优点,并具备软硬件在系统可编程、可裁减、可扩充、可升级的功能。其核心是在FPGA上实现的嵌入式微处理器

2020-03-16 06:37:20

基于X86-64架构的处理器如何实现兼容的应用模式?

2021-04-26 06:50:02

本期文章目录一个小型RISC-V开源处理器核介绍!#SOC#FPGA#RISC-V点击阅读数字积木从零开始写RISC-V处理器(超详细)#RISC-V点击阅读数字积木为什么说模拟工程...

2021-07-23 09:42:00

RK3399核心板采用Cortex-A72+Cortex-A53六核64-bit 2.0GHz处理器,超高性能,最高配置4GB/128GB,提供全功能评估板选购,可以二次开发/扩展,快速实现产品研发

2019-09-16 02:37:59

RK3566四核64位处理器有哪些特点及其功能呢?

2022-03-02 06:00:59

在TMS320F28377D双核处理器中,CPU1子系统充当主系统,在默认情况下(在复位时),它拥有配置和控制所有外设和IO口权限。由于双核各自拥有各自的flash和ram空间,其中LS是每个CPU

2022-02-25 06:17:16

CPU处理器参数可以从以下几个方面进行查看:

CPU品牌:如Intel、AMD等。

核心数:单核、双核、四核、六核等。

主频:表示CPU每秒执行的指令数,单位为GHz。

外频:表示系统总线的工作频率

2023-09-05 16:42:49

我是大学生。我想在微软软核处理器之间创建连接以创建硬件设计。这意味着如果我已经在硬件中创建了内存,我想给一些微小的信号来控制内存(在sdk中)。我有如何创建xps硬件设计并将其导出到sdk和程序并

2020-03-30 10:28:17

项目名称:FPGA上的处理器核原型设计试用计划:申请理由及项目计划:本人西安某高校学生,对数字IC感兴趣,学习过FPGA与处理器相关知识,用过quartus和vivado,ISE,看过水头一寿

2017-07-25 18:02:36

代码加速和代码转换到硬件协处理器的方法如何采用FPGA协处理器实现算法加速?

2021-04-13 06:39:25

主流四核移动处理器解析

2012-08-20 13:01:36

ARM 处理器是一种低功耗高性能的 32 位 RISC(精简指令系统)处理器。从结构 入手对其进行分析,并针对目前流行的 ARM920T 核详细描述其硬件结构和编程。ARM 处理器共有 31 个

2019-09-24 17:47:38

的DSP是什么东西?打开QuartusII的IP核向导,如上图所示。QuartusII中的DSP是一些IP核,它只做一些常见的算法,如:FFT、NCO、FIR等。显然,这并非前面所说的DSP处理器。查看

2020-09-04 10:31:13

可编程逻辑业对微处理器核的报道层出不穷,包括与ARM和MIPS的协议,这些讨论已经持续了数年。然而,讨论的主题大体上没什么改变,诸如采用硬核还是软核?采用供应商的特定标准还是行业标准?这些核如何用来全方位地支持生态系统?如何根据成本、功耗和性能来选择微处理器?如何根据应用来选择核?

2019-08-13 07:52:46

本文介绍在使用Arm DesignStart计划开放的处理器核搭建SoC并通过FPGA实现的过程中所用工具软件(不介绍如何操作),理清“软件编程”和“硬件编程”的概念,熟悉SoC设计的流程。软硬件

2022-04-01 17:48:02

当使用仿真EEPROM组件时,处理器核是否有任何限制。例如,当Flash被写入时,CPU是否停止? 以上来自于百度翻译 以下为原文Are there any limitations

2018-10-11 15:55:20

1、基于同步原语扩展的实时操作系统 在多核处理器的每一个处理器核上都运行一个完全相同的RTOS,然后提供扩展的组件库,这种组件库提供相应的同步原语以支持处理器核间的通信。Eg:VxWorks

2019-06-29 08:30:00

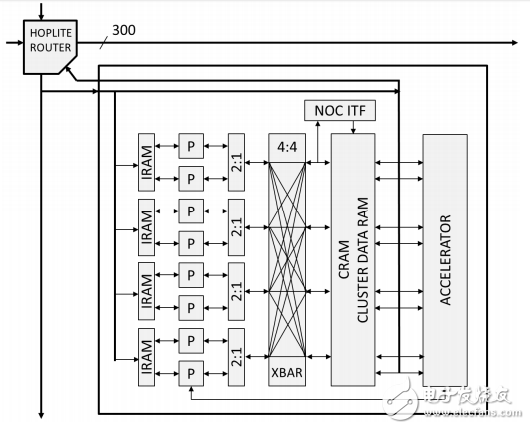

进行控制操作和多媒体显示;DSP天生为数字信号处理而生,擅长进行专用算法运算;FPGA擅长高速、多通道数据采集和信号传输。同时,异构多核SoC处理器核间通过各种通信方式,快速进行数据的传输和共享,可完美实现

2020-09-08 09:39:19

你好我想提出我的两个问题希望我们可以讨论它吗?1.双处理器设计与双核设计之间的差异是什么?2. Xilinx双微填充设计中如何缓存高速缓存一致性。在xilinx WP 262中,声明

2019-03-04 13:41:13

双核处理器ARM_DSP如何实现协同工作

2012-08-17 14:26:59

,物以稀为贵。所以,销售方式好也不失为一种手段。其次是性能出色的双核处理器,采用的是高通的MSM8260处理器,配Adreno220图形处理器。最后在产品ID设计和材料使用上,小米也独具一格。造就了今天的风靡。我们也要跟着潮流的进步而改变并接受,只有努力适应,才会有更多的创新和突变。

2014-04-04 17:29:29

架构双核ARM Cortex-A9 处理器:一个应用级的处理器,能运行完整的像Linux 这样的操作系统传统的现场可编程门阵列(Field Programmable Gate Array,FPGA

2021-07-23 09:23:34

两个方面的内容:IP核生成和IP核复用。文中采用IP核复用方法和SOC技术基于AVR 8位微处理器AT90S1200IP Core设计专用PLC微处理器FSPLCSOC模块。

2019-07-26 06:19:34

基于NIOS II 软核处理器的SOPC 技术摘要:介绍了基于NIOS II 软核处理器的SOPC 技术,分析了传统方法和基于SOPC 技术的方法实现扩频收发机的优劣,详细说明了嵌有双NIOS II

2009-10-06 15:05:24

提供核心部件的稳定保障,缩短客户研发周期。飞凌嵌入式结合特色交通解决方案,展示各产品在智慧路灯、智能停车、车联网、公共交通、5G、北斗车载等领域中的应用。车地5G传输终端飞凌FET1046A-C核心板,基于NXP公司的LS1046A四核处理器设计,主频最高1.8GHz,ARM Cortex-A72架构。

2021-12-20 06:47:59

基于RK3399处理器的64位6核服务器级处理器具有哪些功能呢?

2022-03-04 10:02:37

看出,信箱寄存器机制需要处理器轮询,所以通信效率不高,在休眠/唤醒这类不频繁的操作中还可以,如果是比较频繁的核间通信就不适用了,要采取中断机制。以上是多核处理器启动的基本原理,至于具体实现,不同的厂商有

2022-06-07 16:41:29

的内部系统,应用处理器仅仅在一两年时间内已从单核发展到双核,甚至到目前的四核配置,目的是为了处理越来越多样化和高性能的功能。一些最新的多核应用处理器系列也集成了额外的外设,如DRAM控制器及ARM

2018-09-25 14:28:58

多内核是指在一枚处理器中集成两个或多个完整的计算引擎(内核),多核处理器是单枚芯片(也称为“硅核”),能够直接插入单一的处理器插槽中,但操作系统会利用所有相关的资源,将它的每个执行内核作为分立的逻辑

2019-06-20 06:47:01

CMP的构成分成同构和异构两类,同构是指内部核的结构是相同的,而异构是指内部的核结构是不同的。为此,面对不同的应用研究核结构的实现对未来微处理器的性能至关重要。核本身的结构,关系到整个芯片的面积、功耗

2011-04-13 09:48:17

大小核(big.LITTLE)晶片设计架构正快速崛起。在安谋国际(ARM)全力推广下,已有不少行动处理器开发商推出采用big.LITTLE架构的新方案,期透过让大小核心分别处理最适合的运算任务,达到兼顾最佳效能与节能效果的目的,以获得更多行动装置制造商青睐。

2019-09-02 07:24:33

你好,我打算建立通信以在两个处理器之间读写。一方面是ASIC(MCIMX6)上的四核ARM Cortex A9处理器,另一方面是FPGA(ZC7020)。我在FPGA端没有任何PCIe硬端口。因此

2020-04-16 09:04:30

如何为双核处理器创建静态库?在 CubeIDE 下以“New Project”启动时,“Static Library”点不可用,例如,当使用 STM32H745 (M4 & M7 Core) 时。是否有应用说明,如何做?

2022-12-05 06:51:06

想咨询一下如何在蜂鸟处理器核的基础上扩展第三方指令,使用户自定义指令,并如何构建机器码等内容?

我看了胡老师的RISC-V处理器设计的书里面讲的使用custom1-4来进行扩展,并以EAI为实例进行

2023-08-16 07:36:49

按照这句话的意思,协处理器拓展指令只能实现读写操作吗,官方的案例貌似也只是读写指令。那如何用协处理器拓展指令实现更高级运算呢,用内联汇编吗

2023-08-16 07:41:54

如何调试Zed板702的双核臂处理器。

2019-10-30 09:29:20

若不按照官方文档中的NICE核指令格式自定义指令,主处理器会如何处理该指令?主处理器正常派发该指令给协处理器,报错或者卡死或者忽略?

2023-08-17 06:41:43

对设计进行综合,下载到FPGA中就可以方便地实现一个具有高速DSP功能的嵌入式处理器。那么直接在读写寄存器上进行嵌入式软核Nios Ⅱ串口编程,有哪些方法?我们应该注意哪些事项呢?

2019-08-06 06:37:27

我想将8位软核处理器与EMAC连接以进行TCP / IP通信。请建议我哪个IP核必须去EMAC控制器。如果可能的话,请给我指导其实施TCP / IP的参考设计。以上来自于谷歌翻译以下为原文I

2019-01-24 10:58:20

编程接口共用或并存,可能包含部分可编程模拟电路,单芯片、低功耗。本文主要研究的是应用嵌入式系统开发的软硬件协同设计方法来实现一个集软核处理器的嵌入式设计平台,在此基础上,如有必要还可集成嵌入式操作系统。

2020-03-13 07:03:54

处理器间通信和中断方面仍需进一步的研究。本文在处理器间通信和中断控制方面进行了深入的研究。MicroBlaze是一个被优化过的可以在Xilinx公司FPGA中运行的软核处理器,可以和其他外设IP核一起完成

2021-03-16 07:44:35

本文设计了一种在多处理器系统中的Nios II软核处理器的启动方案,这个方案在外部处理器向Nios II的程序存储器和数据存储器加载数据时,可以控制Nios II处理器的启动。

2021-04-27 06:52:42

本文介绍了一种基于FPGA及NiosII软核处理器与TFT-LCD接口的方法。它直接采用CPU对存贮器的读写,实现了对TFT-LCD屏的实时操作。它具有直接、有效和速度快等特点。该设计使CPU对TFT-LCD的控制极其简单化。

2021-05-08 07:21:11

本文根据FPGA的结构特点,围绕在FPGA上设计实现八位微处理器软核设计方法进行探讨,研究了片上系统的设计方法和设计复用技术,并给出了指令集和其调试方法,提出了一种基于FPGA的微处理器的IP的设计方法。

2021-04-29 06:38:37

最近看了《步步惊芯——软核处理器内部设计分析》,感觉不错,对OR1200的分析比较透彻,好不容易找到了清晰版《步步惊芯——软核处理器内部设计分析》前1-4章的PDF文件,建议大家下载看看。

2013-11-03 13:59:03

本文介绍了基于LEON3开源软核处理器的动态图像边缘检测SoC设计。 实验结果表明该SoC系统工作正常,可以实现每秒22~25帧,最佳分辨率为400×240和640×480的动态图像边缘检测

2021-02-22 07:50:13

看出,信箱寄存器机制需要处理器轮询,所以通信效率不高,在休眠/唤醒这类不频繁的操作中还可以,如果是比较频繁的核间通信就不适用了,要采取中断机制。以上是多核处理器启动的基本原理,至于具体实现,不同的厂商有

2022-07-19 15:00:47

经过努力,开源软核处理器OpenMIPS的实践版终于新鲜出炉了,相对OpenMIPS教学版而言,OpenMIPS实践版最大的特点是引入了Wishbone总线接口,组建了SOPC,包括SDRAM控制器

2014-01-06 17:41:21

听说苹果最新处理器A7出来时完爆其它的移动处理器,现在高通的骁龙800能与之媲美吗?联发科的“8核”能否抗衡

2013-08-07 00:48:31

请教大神怎样使用ARM DesignStart计划开放的处理器核搭建SoC系统呢?

2022-07-29 15:01:05

片上Nios Ⅱ嵌入式软核多处理器系统具有哪些优势?如何实现片上嵌入式Nios Ⅱ软核六处理器系统的设计?

2021-04-19 08:17:09

处理器上有更多的选择,Altera公司宣布,Freescale将为SOPC Builder工具推出32位V1 ColdFire软核。为迅速方便的使用Altera? Cyclone? III FPGA建立

2008-06-17 11:40:12

包含一个以上的嵌入式处理器IP(Intellectual Property,知识产权)核,具有小容量片内高速RAM资源,丰富的IP核资源可供灵活选择,有足够的片上可编程逻辑资源,处理器高速接口和FPGA编程接口共用或并存,可能包含部分可编程模拟电路,单芯片、低功耗[1]。

2019-08-23 08:18:51

飞思卡尔半导体推出具备先进功率管理功能的 QorIQ® P1022 双核处理器,以便在嵌入式系统中实现节能设计。这种低能耗、高性能的 P1022 处理器帮助嵌入式系统设计者满足绿色能源的强制性要求,同时还能将整个系统控制在低成本内。

2019-09-03 06:16:46

高速专用GFP处理器的FPGA实现采用 实现了非标准用户数据接入 网络时,进行数据 封装和解封装的处理器电路在处理器电路中引入了缓冲区管理器,使得电路能够有效处理突发到达 瞬时速率较高的客户

2012-08-11 11:51:11

龙芯1B 芯片是基于GS232处理器核的片上系统, 具有高性价比,可广泛应用于工业控制、家庭网关、信息家电 、医疗器械和安全应用等领域。1B采用SMIC0.13微米工艺实现,采用Wire Bond

2021-07-23 08:36:40

Cortex-A72核心模块 64位6核 RK3399六核“服务器级”处理器Cortex-A72核心模块 64位6核 RK3399六核“服务器级”处理器

2021-12-14 10:03:19

电子发烧友App

电子发烧友App

评论