现在使用CST92F25,gpio(p14)上会有一个4V的脉冲式的电压,脉冲宽度几百毫秒,周期50Hz,现在配置的是上拉输入或者下拉输入,这样的话会有什么风险吗?另外想问一下如果配成高阻态,芯片内部是怎么处理的呢?

2023-02-23 13:01:50

这个时序图,当control为0的时候,作为输入和输出端的q波形为啥是一样的呢?按照程序意思,作为输出端,不应该是高阻态吗?

2013-05-06 19:08:10

一开始输出为高阻态,然后才正常运行!

2015-11-03 20:13:44

单片机引脚什么时候表现为高阻态?切断芯片的电源是否就使得芯片的引脚呈现高阻态了呢?求教!

2017-03-11 12:12:17

高阻态和三态门高阻态 高阻态的实质:电路分析时高阻态可做开路理解。你可以把它看作输出(输入)电阻非常大。他的极限可以认为悬空。也就是说理论上高阻态不是悬空,它是对地或对电源电阻极大的状态。而实际

2019-01-08 11:03:07

数字电路常见术语:高阻态,三态门高阻态常用的表示方法

2021-03-01 11:09:49

高阻态高阻态是电路的一种输出状态,既不是高电平也不是低电平,如果高阻态再输入下一级电路的话,和没接一样。电路分析时可以把高阻态看成开路,即输出(输入)电阻非常大,极限可以认为是悬空。但是理论上高阻态

2022-01-25 07:03:19

悬空,顾名思义,就是不接任何器件啦高阻态:无上拉和无下拉,对外表现出电平不确定性不是所有的单片机都支持三态输出。三态输出一般由寄存器控制,需进行配置。高阻态既然无确定电平,怎么能做输出呢?把一个端口

2021-11-24 08:19:25

电路分析时高阻态可做开路理解。你可以把它看作输出(输入)电阻非常大。它的极限状态可以认为悬空(开路)。也就是说理论上高阻态不是悬空,它是对地或对电源电阻极大的状态。而实际应用上与引脚的悬空几乎是一样的。

2019-05-23 06:58:08

`发电机中性点采用“经高电阻接地”方式,即经副边带电阻的配电变压器接地,也就是在中性点和地之间连接一配电变压器,在其二次侧连接一只电阻,使中性点线路的阻抗值增大,起到限制接地电流的作用。高阻接地

2019-04-17 09:07:11

高阻无源探头即我们通常所说的无源探头,应用最为广泛,基本上每个使用过示波器的人都接触过这种探头。高阻无源探头和示波器相连时,要求示波器端的输入阻抗是 1M 欧姆。以下是一个 10:1 高阻无源探头

2018-04-02 09:17:49

高阻硅材料进口半导体单晶硅、高阻硅片,有n型、p型、本征硅片,晶向〈111〉、〈100〉、〈110〉,直径1~8寸的单抛硅片、双抛硅片、氧化硅片,超平硅片、超薄硅片、超厚硅片,异型硅片,电阻率30000Ω.Cm,详细参数来电咨询,也可根据用户要求生产。欢迎垂询,***.

2018-01-22 11:49:03

高阻配电电路图如图为高阻配电电路图。它与低阻配电的显著区别是在各分路负载中串接一定阻值的限流电阻R1,一般取值为电池内阻的5倍~l0倍。这时如果某一分路发生短路,则系统电压跌落及反冲尖峰电压都较小

2009-10-24 09:24:04

如硬件图,用Proteus仿真时,明明OE口输入1了,管脚却是灰色的,说明是高阻态程序如下:(desplay是用数码管显示AD转换的数,老是显示0,所以我怀疑是OE的问题,注意程序倒数第七行,已经把

2013-03-26 09:05:44

CC2530应该怎么定义Io口是高阻状态?

2016-03-14 11:18:18

问题描述:CS32G020 PB12/PB11输出低电平点亮LED0/LED1, 实测PB12/PB12会有周期位2.2s,脉宽为200ms的脉冲出现,造成LED灯闪烁,猜测是内部IO状态变成了高阻态导致.*附件:CS32G020问题.doc

2022-09-02 09:18:39

本帖最后由 李姝萱 于 2021-4-7 15:18 编辑

由于功能的要求,子模块内部部分信号需赋初值(或最后拉高)为高阻态,现在quartus2给出警告Warning (13046

2021-04-06 15:34:40

用的很简单的verilog 程序,步骤都是按照教程来的,但是仿真结果输入总是高阻态,试了很多不同的程序都是同样的问题module xor_2(y,a,b );output y; input a

2014-07-29 21:11:27

今天在使用ISE的Isim仿真时发现输出一直为高阻,经过排查发现这种情况是由于仿真器无法全面检查测试模块导致,使用综合器检查即可排查错误。在我的测试模块中,同时使用上升沿和下降沿赋值,在仿真器中通过,而这在综合器中是不允许的,改为单上升沿赋值解决了问题。

2017-09-06 14:45:39

当为高的时候是高阻态 如何让输出不是高阻态 请各位指点迷津

2017-10-21 17:48:40

大家好,我有一个关于Linux Vivado中多个OOC模块综合的快速问题。我在Ubuntu 14.04LTS上运行Vivado 2015.4.2。我注意到在我的Windows机器上,同一

2020-04-29 10:03:04

为什么我按照“基于M9K块的单口RAM配置仿真实验—LiangXuan-博客园的程序从头做了一遍,发现dout输出总是高阻态,哪位大神能帮忙解决下吗?感激不尽。在MegaWizard Plug-In Manager的配置上没有那么详细,有没有可能是这块出了问题?求帮忙

2014-12-18 11:03:48

`请问PCB过孔阻焊的处理方式有哪些?`

2019-12-31 15:28:04

用PIC16F877A实现高阻态输出,就像89C51的P0端口一样,输出"1"时候,电压较低???

2012-11-06 14:29:41

如题,例如用PWM1引脚输出PWM波形,如何将这个引脚设置成高阻!谢谢各位师傅们!

2013-05-20 11:48:38

STC的IO的高阻,的读取外部状态是否和准双向IO一样要先锁存为1?还是说即使高阻锁存为0也可以读取外部状态?

2019-05-21 04:35:40

的影响 / 462.2.4 use_dsp48在实现加法运算时的作用 / 482.3 out-of-context(OOC)综合模式 / 502.3.1 Project模式下使用OOC / 502.3.2

2020-10-21 18:24:48

的任何子模块。来自IP catalog的IP就默认使用OOC综合的方式,例如上图中的“Synthesis Options”选项就设置为了“Out of Context Per IP”。这些IP会在顶层

2023-04-17 16:33:55

adc引脚悬空时,串联在adc引脚上的电阻有0.1v的分压,难道adc悬空时,引脚不是高阻态?

2024-03-05 08:20:17

最近调用乘法器的ip核为了进行有符号的16位乘法运算,查看内部输入信号 都正常不清楚为啥modelsim仿真的输出脚就是高阻态,求教各位了。谢谢{:23:}

2013-04-10 16:32:11

现在使用psoc6.发现spi口。 在进入deepsleep模式前,我想降低功耗,将spi口配置为高阻态模式

2024-02-21 06:16:58

tc3xx,休眠时mcu pin可以是高阻态吗?如何设置?

2024-01-19 08:26:57

`在我们刚一开始接触到51单片机的时候对P0口必须加上上拉电阻,否则P0就是高阻态。对这个问题可能感到疑惑,为什么是高阻态?加上拉电阻?今天针对这一概念进行简单讲解。高阻态高阻态这是一个数字电路里

2019-07-29 07:00:00

一、三态单片机IO的三态是指:高电平(1)、低电平(0)、高组态(Z)。二、高阻态高阻i是一种电路状态.既不是高电平,也不是低电平,以高阻态对下级电路输出,下级电路什么影响也没有.高阻态的IO电平

2021-11-25 06:42:28

如图所示:1.不是说高阻态电平不确定么,为什么高阻态时两个灯都灭,按理论来说高阻态其中必有一个亮对么?2.去掉IN4148行么?它在这里编演什么角色?

2020-07-19 08:06:45

, sum, cout);endendmodule在vivado2017.3 Run Behavioral Simulation下的运行结果,sum是高阻态,这是为什么呀?`

2017-12-25 17:18:31

指示灯,继电器等,其驱动指示灯的电路如图所示。什么是三态门?三态门,是指逻辑门的输出除有高、低电平两种状态外,还有第三种状态——高阻状态的门电路 高阻态相当于隔断状态。 三态门都有一个EN控制使能端,来

2008-05-26 13:01:37

看到有些手册中写到引脚处于高阻状态,请问这是一种什么状态呢?

2023-10-31 07:02:45

为PWM输出,当PWM为高时,芯片输出正常,PWM为低时,芯片输出高阻态,控制见下方截图。 那么整个PWM循环中,芯片处于正常工作和高阻态输出。这样对电机是否有影响?同时对电机芯片有什么影响?而且测试

2021-06-29 22:49:22

本帖最后由 hy658 于 2015-12-23 21:58 编辑

我们可以给单片机0或1.控制高电平或者低电平输出,能不能控制输出高阻态?用3个单片机io口,控制4个LED亮灭?

2015-12-23 21:35:48

单片机I/O口做输入时接一个很大的电阻,是否相当于高阻态,输入电压信号是否会有压降?

2020-03-19 03:59:11

问一个菜鸟问题,单片机IO口悬空和高阻态究竟是什么?IO口具体设置成什么?(输出不接外部器件?输入不上拉?)我查了下百度都没说清楚,复制粘贴的就算了!!另外想问一下,LCD驱动时IO口是怎么输出3种

2014-06-28 08:47:37

单片机中的高阻态到底什么意思?在我们刚一开始接触到51单片机的时候对P0口必须加上上拉电阻,否则P0就是高阻态。对这个问题可能感到疑惑,为什么是高阻态?加上拉电阻?今天针对这一概念进行简单讲解。高阻

2019-12-31 08:00:00

单片机中的高阻态是什么

2020-12-28 07:59:37

在我们刚一开始接触到51单片机的时候对P0口必须加上上拉电阻,否则P0就是高阻态。 对这个问题可能感到疑惑,为什么是高阻态?加上拉电阻?今天针对这一概念进行简单讲解。 高阻态 高阻态这是一

2021-01-13 16:56:04

我可以获得一些关于上下文实现的文档吗?以上来自于谷歌翻译以下为原文Can I get some documentation on Out-of-Context Implementation?

2018-10-30 11:08:13

回到原状态,必须在IC外部另接一电阻。2、数字电路有三种状态:高电平、低电平、和高阻状态,有些应用场合不希望出现高阻状态,可以通过上拉电阻或下拉电阻的方式使处于稳定状态,具体视设计要求而定!3、一般说

2011-07-28 09:58:10

吸电流、拉电流、灌电流、上下拉电阻、高阻态分析

2012-08-18 07:40:57

顶级模块的实现。这可能吗?我正在OOC检查点读取并使用模式out_of_contex和top作为顶部运行synth_design。我不希望IO缓冲区插入顶部。我这样做是为了对正常合成和上下文合成之间

2018-11-09 11:43:59

三态门高阻态时,同或门输出状态怎么判断?F的 逻辑表达式

2015-12-15 10:59:57

相当大的设计,需要大约一个半小时才能构建。我发现OOC模块占用了大约三分之一的时间,并且想知道是否有办法从合成中排除未修改的IP块。我尝试使用以下TCL命令从综合中排除这些:set_property

2020-04-29 07:43:42

怎么实现楼宇对讲系统中音频电路的设计?怎样设计通话电路达到高租态呢?

2021-06-04 06:01:30

要找一个7路输入/输出并带高阻的三态输出的逻辑IC,体积要小点的,有知道的请推荐一下,谢谢!!!积分只有13分,全给了。

2016-01-04 11:36:40

请各位大侠么讲解一下高阻态与不定态的区别?单片机的接口如何设置成高组态如何设置成不定态!

2012-08-26 16:52:47

out_of_context#optimize netlist opt_design #Place Design place_design #rebuffer high fanout nets

2018-10-23 10:30:35

在做时序仿真的时候,发现一个问题,代码如下:assign gateway_out1 = gateway_in10 * gateway_in11 结果发现 输出带有高阻态,波形如图。 在做功能仿真的时候没有问题,做时序仿真就出现问题了。 请问这是什麼原因造成的。

2017-07-27 09:09:53

在我们刚一开始接触到51单片机的时候对P0口必须加上上拉电阻,否则P0就是高阻态。对这个问题可能感到疑惑,为什么是高阻态?加上拉电阻?今天针对这一概念进行简单讲解。高阻态高阻态这是一个数字电路里常见

2020-07-24 07:32:20

新人在工作中经常碰到三态门与高阻态;请教技术大佬,这两个到底是什么东西 ?

2021-04-07 06:59:01

我正在使用该芯片,将数据输出到FPGA处理。想请问下,由于不需读取旋变数据时,我将ad2s80芯片设置为禁能模式。这样会不会导致芯片禁能高阻与fpga输入高阻相连,导致高阻引脚电平不确定。我想问下,我当前的设计合理么,在ad2s80芯片和fpga之间需要增加上拉电阻么,阻值多少合适?

2018-09-28 15:12:09

由于利用外部放大电路,将AD5522的输出电压范围扩大两倍来实现±22V的输出摆幅。

当FV输出高阻时,环路是断开的,内部运放的输出电压未知,这样从高阻态再回来正常FV模式时,会有一个很大的毛刺

2023-12-05 08:00:36

HC32F003的单片机IO口怎么配置成高阻态?

2023-09-27 07:29:59

系统上电后,I/O的状态是高阻态么?还是是输入状态?

2018-08-16 06:01:22

现在需要实现低功耗,手册说需要把未使用的IO配置为高阻态,请问应该如何配置?

2024-02-18 08:27:43

是不是高阻态

2023-10-24 07:41:26

开关管驱动用,想找一个类似与74HCT245的芯片,可控制信号通断。74HCT245是三态输出,不使能的时候输出端是高阻,有没有一款芯片能在控制端的作用下,不需要有效信号时输出全部为低电平的??比较着急,感谢感谢!!!

2019-08-10 10:29:57

大家好,这里的任何人都可以为我提供有关最新OOC实施流程的教程吗?我有用户指南,但它提到我可以应Xilinx支持请求接收教程。另外,我们是否在最新版本的Vivado中为GUI提供了GUI支持。我发现

2020-05-26 06:19:55

GPIO输入具备缓冲功能,输出均具有锁存功能GPIO一般具有三态:0态、1态、高阻态启动总线:SCL保持高电平时SDA由高转为低终止总线:SCL保持高电平时SDA由低转为高数据传送时高位在前,低位

2021-12-23 07:27:59

请问下有没有大神知道高压高阻箱的相关设计资料,以及国内外现状等相关资料的啊,能不能共享下呢?

2016-09-22 09:45:47

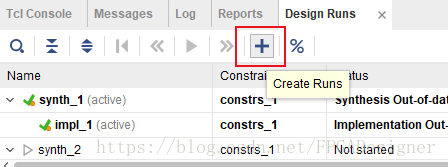

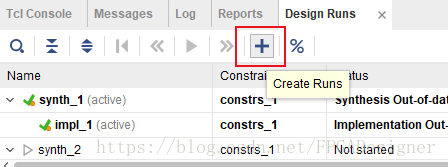

创建综合运行 一个“运行(run)”是指定义和配置设计在综合过程中的各方面,包括:使用 的Xilinx器件、应用的约束集、启动单个或多个综合的选项、控制综合引擎结果的选项。点击Flow菜单

2021-01-02 09:03:00 3081

3081

随着大规模预训练语言模型(LLM)能力的不断提升,in-context learning(ICL)逐渐成为自然语言处理领域一个新的范式。

2023-04-21 10:02:14 989

989 Context接口没有提供方法来设置其值和过期时间,也没有提供方法直接将其自身撤销。也就是说,Context不能改变和撤销其自身。那么该怎么通过Context传递改变后的状态呢?

2023-11-16 16:15:08 156

156

正在加载...

电子发烧友App

电子发烧友App

评论