)、锁相环频率合成技术(PLL)、直接数字频率合成技术(DDS)、混合频率合成技术四种实现方式,其中锁相环频率合成器是射频电路中最常使用的一种结构,相比于其他几种结构,PLL结构能够在有限的功耗限制下合成高性能的载波信号。

2015-10-17 11:24:00 1656

1656

现在在调试DDS激励ADF4351输出扫频信号的板子,碰到点问题。当配置4351寄存器的参考时钟为20MHZ时,输入的参考时钟只能在20MHZ+/-1MHZ的范围内变化,超过这个范围就会失锁,不知道是我哪个寄存器配置问题,还是这个芯片无法做到较大范围改变参考时钟而不会失锁。希望得到回复,谢谢!

2018-11-12 15:10:51

现在在调试DDS激励ADF4351输出扫频信号的板子,碰到点问题。当配置4351寄存器的参考时钟为20MHZ时,输入的参考时钟只能在20MHZ+/-1MHZ的范围内变化,超过这个范围就会失锁,不知道是我哪个寄存器配置问题,还是这个芯片无法做到较大范围改变参考时钟而不会失锁。希望得到回复,谢谢!

2018-12-03 16:09:22

我用ADF4351做一个整数分频的锁相环输出,控制器是51单片机,程序能下载进单片机,时序是参考网上写寄存器的程序,但是寄存器赋值LD引脚高低电平变化时,在LD引脚检测不到高低电平,感觉寄存器值没写

2019-01-04 10:16:12

我ADF4351不能正常控制它的输出频率,控制板调整输出频率数值增加一定范围的数值,ADF输出端输出频率才发生变化,并且输出频率错误。比如驱动板控制ADF输出70MHZ,但是ADF输出端只有

2017-07-15 17:35:36

专家们好,最近项目用ADF4351做AD/DA的采样时钟源,时钟频率为100MHz,结果寄存器写进去了,锁定指示LD管脚连接的指示灯也亮了,但用示波器看输出却没有信号,不知为何,同样的程序,把时钟

2018-10-25 09:12:45

我使用ADF4351,其输出在中心频率偏移184k附近有杂散输出,通过减小环路带宽,减小充电电流等,杂散有一定的降低, 此时带来靠近中心频率出的噪声升高,通过对比不同的板卡,都存在类似的现象,环路

2018-10-12 09:24:23

`配置界面如图所示,测量ADF4351输出谐波比较多,测量锁定引脚发现没锁定,混频出来谐波也比较多,请教下我这个问题出在哪?`

2019-09-10 15:48:00

我根据ADF4351评估板做了个板子,采用78M05和ADP7102-3.3供电,环路滤波器和评估板一致,一级输出接了低噪放放大,另一极直接输出,晶振是10M温补晶振。目前测试发现置数后数字锁定没有

2019-01-16 08:17:56

本人新手,最近再学习ADF4351的使用,在制作PCB时发现官网中所给出的ADF4351BCPZ的封装里的输出引脚(11,12)与ADF4351的用户手册里的输出引脚(12,13)对应不上,而且还有

2018-09-04 11:35:32

使用ADF4002搭建一个锁相环,依据simPLL软件推荐的滤波器,实验效果未达预期。实验记录见附件,请高手给看看问题出在哪里?

2021-11-24 22:56:12

求一ADF5355_锁相环相关资料,最好中文版,详细点

2017-03-06 23:32:13

想用adf4351做一个锁相环提取载波,但是每次锁定后输出都和参考有一个随机的相位差,请问如何才能消除这个相位差,使输出与参考输入同频同相。寄存器配置如下:

2018-08-09 06:48:18

本帖最后由 gk320830 于 2015-3-9 20:38 编辑

最近在用adf 4001做一个锁相环,环路配置好后发现锁定不了,电荷泵cp 输出一直在扫描,检查芯片内部的配置,也没发现什么问题,分频输出也是正常的,哪位高手用过这个芯片,帮我分析分析吧,期待中。。。

2010-09-14 08:52:16

本文按照数字锁相环设计的步骤,采用手把手的方式讲述设计过程和原理,旨在给数字锁相环初次设计者提供一个思路,缩短开发的时间。 有关数字锁相环的帖子不断出现,但大多没有讲述其原理。翻开有关锁相环的书总是

2012-01-12 15:29:12

数字锁相环设计源程序PLL是数字锁相环设计源程序, 其中, Fi是输入频率(接收数据), Fo(Q5)是本地输出频率.目的是从输入数据中提取时钟信号(Q5), 其频率与数据速率一致, 时钟上升沿锁定在数据的上升和下降沿上;顶层文件是PLL.GDF

2009-12-18 10:37:37

频率合成器的主要性能指标锁相环频率合成器原理锁相环频率合成器捕捉过程的分析与仿真

2021-04-22 06:27:35

及可编程分频器三部分组成。其中可编程分频器是单片微机与锁相环之间的接口,同时也是组成数字锁相频率合成器的关键部件,在移动通信陆地电台等领域有着广泛的应用。</p><

2010-03-16 10:59:24

技术占有越来越重要的地位。由一个或几个高稳定度、高准确度的参考频率源通过数字锁相频率合成技术可获得高品质的离散频率源。

2019-06-20 06:24:14

请问锁相环仿真用什么软件好,我们需要用到ADF4110VOC选择MAX2606

2016-06-27 15:57:53

我用msp430和adf4106加一个vco 和环路滤波做了一个锁相环,但频率漂到其他地方了!请大神解决

2016-01-20 15:07:57

ADI是高性能模拟器件供应商,在锁相环领域已有十多的的设计经验。到目前为止,ADI的ADF系列锁相环产品所能综合的频率可达8GHz,几乎能够涵盖目前所有无线通信系统的频段。ADF系列PLL频率合成

2018-10-31 15:08:45

ADI是高性能模拟器件供应商,在锁相环领域已有十多的的设计经验。到目前为止,ADI的ADF系列锁相环产品所能综合的频率可达8GHz,几乎能够涵盖目前所有无线通信系统的频段。ADF系列PLL频率合成

2018-11-06 09:03:16

锁相环控制频率的原理锁相环频率自动跟踪-------用锁相环可以确保工作在想要的频率点上如何理解以下两段话?鉴相器是相位比较装置, 它把输入信号和压控振荡器的输出信号的相位进行比较, 产生对应

2022-06-22 19:16:46

EVAL-ADF4351EB1Z,该板设计用于允许用户评估ADF4351频率合成器的性能,以实现锁相环(PLL)。它显示了该板,其中包含ADF4351集成合成器和VCO,用于输出信号的SMA连接器

2019-03-01 08:03:03

FPGA怎么驱动ADF4351去产生一个正弦波

2016-06-04 14:57:29

介绍了锁相环路的基本原理,分析了集成锁相环芯片ADF4106的工作特性,给出了集成锁相环芯片ADF4106的一个应用实例,为高频频率合成器的设计提供了很好的思路。 关键词:ADF4106,锁相环,频率合成器,环路滤波器

2019-07-04 07:01:10

使用STM32控制ADF4351,频率分辨率设置为1M。进行了如2700MHz、2705MHz时一切正常,但当设置输出入2701、2702不被5整除的频率时,出现很小的杂波。希望了解这方面的专家给予简答。

2018-09-04 11:23:28

全数字锁相环的设计及分析 1 引 言 锁相环是一种能使输出信号在频率和相位上与输入信号同步的电路,即系统进入锁定状态(或同步状态)后,震荡器的输出信号与系统输入信号之间相差为零,或者保持为常数

2010-03-16 10:56:10

我有一块ADF4351的开发板,但是我现在想用相位噪声测试仪测量ADF4351的VCO开环相位噪声,但是却不知道怎样设置,如果仅仅只是将振荡器移除,测量得到的相位噪声是VCO的闭环相位噪声,有没有大神知道怎么设置才能测量VCO的开环相位噪声, 希望能够指点一二 谢谢

2018-08-02 07:46:23

图一图一中U2是ADF4351,U6和U8是两个串联的射频开关HMC347,两个开关中心距是6mm,一个HMC347在2.4GHz隔离度大概50多dB,C44这边是ADF4351频率源的输出,是个

2019-01-10 14:27:42

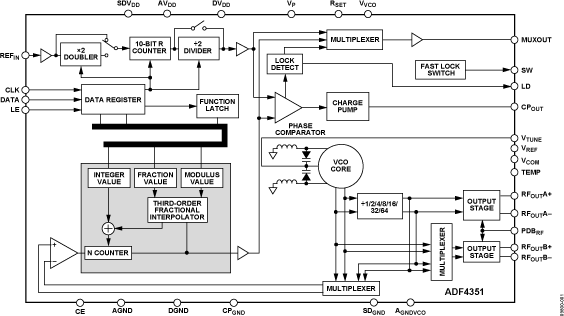

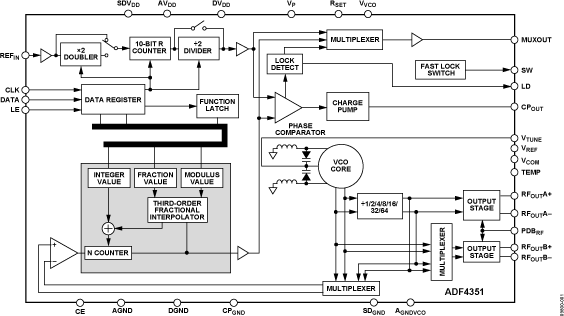

ADF4351锁相环介绍及相关硬件设计ADF4351是ADI公司推出的一款集成VCO的锁相环芯片。其输出频率范围可配置为35MHZ到4400MHZ,这取决于参考频率和寄存器配置。其内部包括整数N

2022-01-11 07:28:51

下合成高性能的载波信号。本文基于锁相环芯片ADF4106设计了一种数字锁相环频率合成器,具有超宽的带宽、较好的噪声特性、快速锁定时间,以及功耗低和体积小等特点,从而被广泛应用于无线通信系统中。一

2018-09-06 14:32:13

本文设计了一种多环锁相频率合成器。多环锁相环路有直接数字频率合成(DDS)环路和锁相频率合成环路(PLL)组成。充分利用两个不同环路的优点,既保证了高的输出频率,又得到了较高的频率分辨率。【关键词

2010-05-13 09:09:53

锁相环是什么工作原理?如何采用FPGA与频率综合器ADF4111相结合的方法实现数字锁相式频率源的设计?

2021-04-14 07:00:20

锁相环频率合成器是什么原理?基于CD4046的锁相环频率合成器的设计

2021-04-12 06:28:35

全数字锁相环由那几部分组成?数字锁相环的原理是什么?如何采用VHDL实现全数字锁相环电路的设计?

2021-05-07 06:14:44

数字锁相环频率合成系统的工作原理CPU控制数字锁相环频率合成系统FPGA实现

2021-04-09 06:20:37

EV-ADF41020EB1Z,用于ADF41020 PLL频率合成器评估板的评估板。评估用于锁相环(PLL)的ADF41020频率合成器。它包含ADF41020合成器,100 MHz TCXO,电源,USB接口和RF输出。板载有一个有源环路滤波器和一个13 GHz VCO

2019-02-28 07:23:02

评估板EVAL-ADF4152HVEB1Z旨在让用户评估ADF4152HV频率合成器的性能,以实现锁相环(PLL)。该板包含ADF4152HV合成器,环路滤波器,1GHz至2GHz倍频程的压控振荡器

2019-03-01 10:17:42

您好,我设计的ADF4351采用数字工业级晶振 或 恒温正弦波晶振 作为参考时钟,输出混有谐波,(1)当采用数字工业级晶振,低频输出时,最强谐波比基波低3~4个dB,示波器看起来有点近似方波输出(2

2018-08-09 07:20:13

请问ADF4351的基准输入REFin用正弦波还是方波,其功率电平大小范围是什么?谢谢

2018-09-07 09:50:33

使用ADF4351设计了一个频率源,频率范围1200M-2500M,步进1M,要求跳频时间控制在50us内,通过实际测试只能到100us。现在想知道ADF4351最快的频率锁定时间是多少啊?如果可以达到的话,应如何设置寄存器?参考频率100M,鉴相频率25M,环路带宽为250K。

2018-10-11 09:21:28

问题描述:使用ADF4351评估板自带的25 MHz参考频率,输出频率为1422 MHz,参数设计如下图所示: 使用频谱仪输出频率,Span设置为100 Hz,VBW和RBW自动设置,发现频率在

2018-09-12 11:08:59

ADF4351移相时禁用频段选择,设置相位值,并不能实现移相操作?

2019-01-03 21:35:40

工程师您好:ADF4351内部集成VCO振荡器,如果结合外部环路滤波器和外部参考时钟频率能构成数字锁相环吗?如果不能是不是因为ADF4351内部没有鉴相器,如果我想做数字锁相环还要和ADF4002合用吗?能实现位同步吗?期待您们的答复!

2018-09-14 14:23:29

采用ADF4351输出频率,发现设置输出频率时,其3、5、7、2、4、6等倍频的位置幅值很大,特别是基波600M频率以下时,3倍频谐波输出幅度超过了基波,请教如何能将高次谐波大幅度减小?

2018-09-25 11:29:24

请教老师,我想用一个PLL(ADF4351)给两个DAC(AD9119)提供时钟,DAC时钟频率最高为1.5GHz。我的ADF4351输出可以直接接到两个DAC的CLK输入端吗(也就是两个DAC并联

2018-12-03 09:26:26

用ADF4351点频输出,为什么频率在1.7GHz-2.3GHz,输出有分频谐波?图中显示是输出锁到1.8GHz的,但是其左边还有900MHz和600MHz的分频谐波。请问这是什么问题,如何解决?

2018-09-03 14:04:59

打算将adf4351输出的2Ghz的信号应用到si分析当中,因此需要获得其输出的时域波形或得知上升沿时间、下降沿时间和占空比这样的信息。那么如何获得这些信息?曾使用过adisimpll仿真软件进行仿真,但是还是无法获得上升沿和下降沿时间,不知是不是操作有误还是另有原因。希望大家能够帮忙解答!

2019-03-01 14:48:43

您好!请问频率合成器ADF4351数据手册中提到的“通道步进分辨率”是什么意思?它有什么作用?下图是ADF4351的评估板软件,我想要配置1425.42MHz的输出,请问Channel

2018-10-26 09:07:07

我近日在学习锁相环时使用STM32控制ADF4351产生264.3MHz的LO。在使用ADIsimPLL设计工具时,根据填入参数,生成的配置中Prescaler P选项默认设置成8,但是我觉得根据

2018-07-27 09:25:30

请问一些关于ADF4351的问题1.ADF4351能在40~4.4GHz都单端输出2dBm的功率吗?功率波动为2dBm2.辅助输出B也能在单端输出时输出2dBm的功率吗?功率博能能到2dBm吗?3.

2018-07-30 06:06:13

`具体要求是这样的,要利用ADF4351产生多路同频并具有特定相位差(如相差为0)的信号。目前我利用同一个外部时钟和STM32f103RCT6控制板实现了4路同频信号(我这里是151MHz)的产生

2018-11-18 18:06:50

最近在调试adf4351,出现数字检测是高电平,LD也输出高电平,但没输出信号,请问是什么问题?

2018-09-25 14:14:51

各位前辈们好,请问,用频谱仪测量ADF4351输出,为什么1.7GHz-2.3GHz的频率段没锁住,而35MHz-2.5GHz的其他任何频率锁的频谱都非常好?环路滤波器我是仿的50MHz到2.5GHz的。

2018-09-04 11:35:39

驱动高压锁相环频率合成器电路的VCO

2021-01-11 06:02:04

ADF4351结合外部环路滤波器和外部基准频率使用时,可实现小数N分频或整数N分频锁相环(PLL)频率合成器。 ADF4351具有一个集成电压控制振荡器(VCO),其基波输出频率范围为

2023-02-16 15:13:11

锁相环的研究和频率合成一、实验目的:1. 振荡器(VCO)的V—f 特性的研究2. 对称波锁相环基本特性的研究3. 利用锁相环实现频率合成二、锁相环原理:

2009-03-06 20:02:52 1939

1939

介绍了锁相环路的基本原理,分析了集成锁相环芯片ADF4106的工作特性,给出了集成锁相环芯片ADF4106的一个应用实例,为高频频率合成器的设计提供了很好的思路。

2009-05-05 19:57:57 2585

2585

集成锁相环频率合成器,什么是集成锁相环频率合成器

频率合成的历史

频率合成器被人们喻为众多电子系统

2010-03-23 11:45:44 770

770 全球领先的高性能信号处理解决方案和 RF IC供应商,最近推出一款用于无线通信系统的 PLL(锁相环)频率合成器ADF4351。

2011-06-21 16:50:02 2278

2278 电子发烧友网为你提供ADI(ti)ADF4351相关产品参数、数据手册,更有ADF4351的引脚图、接线图、封装手册、中文资料、英文资料,ADF4351真值表,ADF4351管脚等资料,希望可以帮助到广大的电子工程师们。

2019-02-22 15:16:34

本文档的主要内容详细介绍的是基于MSP430F5438A的ADF4351锁相环频率锁定程序的详细资料免费下载。

2019-03-18 08:00:00 55

55 本视频将介绍如何搭建ADF4351评估板

2019-07-08 06:15:00 2707

2707 ADF4351 Gerber Files

2021-02-03 15:49:30 3

3 ADF4351 Gerber Files

2021-03-06 08:25:27 5

5 ADF4350/ADF4351 Evaluation Board Software

2021-03-10 14:40:42 7

7 UG-369:ADF4151锁相环频率合成器评估板

2021-04-19 20:14:47 6

6 UG-802:用于锁相环的ADF5355频率合成器评估

2021-04-25 12:23:05 3

3 UG-873:评估ADF4355-3小数/整数N锁相环频率合成器

2021-04-28 14:35:35 5

5 UG-804:评估ADF4355-2小数/整数N锁相环频率合成器

2021-05-10 08:26:33 8

8 UG-383:用于锁相环的ADF4159频率合成器评估

2021-05-10 13:26:06 1

1 UG-485:ADF4153A小数N锁相环频率合成器评估板

2021-05-16 13:22:43 8

8 UG-1087:用于锁相环的ADF5356频率合成器评估

2021-05-17 09:38:07 4

4 ADF4217:双射频锁相环频率合成器过时数据表

2021-05-17 11:55:55 2

2 UG-389:ADF4xxx锁相环频率合成器的USB转并行转接板

2021-05-24 11:46:02 6

6 UG-686:ADF4155锁相环频率合成器评估板

2021-05-25 16:46:51 4

4 ADF4150HV锁相环频率合成器UG-406评估板

2021-06-03 11:16:33 7

7 该评估板旨在帮助用户评估支持锁相环(PLL)的频率合成器ADF4351的性能。它包含ADF4351集成式频率合成器和VCO、用于输出信号的SMA连接器、电源、参考振荡器和USB连接器。片上还集成

2021-06-04 13:54:55 3

3 ADF4351腔体完整带控制器V1.0文件资料分享

2022-10-08 11:24:05 2

2 电子发烧友网站提供《基于ADF4111的锁相环频率合成器设计.pdf》资料免费下载

2023-10-20 14:45:29 0

0

电子发烧友App

电子发烧友App

评论