我再换种更简单的描述

二进制数 1 0 1 1 0

二进制数右移1位,空位补0 0 1 0 1 1

异或运算 1 1 1 0 1

这样就可以实现二进制到格雷码的转换了,总结就是移位并且异或,verilog代码实现就一句:assign wgraynext = (wbinnext>>1) ^ wbinnext;

是不是非常简单。

三、代码解析

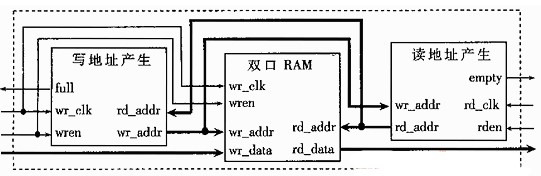

异步FIFO的信号接口:

wclk wrst_n winc wdata //写时钟、写复位、写请求、写数据这几个与写有关的全部与wclk同步

rclk rrst_n rinc rdata //读时钟、读 复位、读 请求、读 数据 这几个与读有关的全部与rclk同步

wfull //写满 与wclk同步

rempty // 读空 与rclk同步

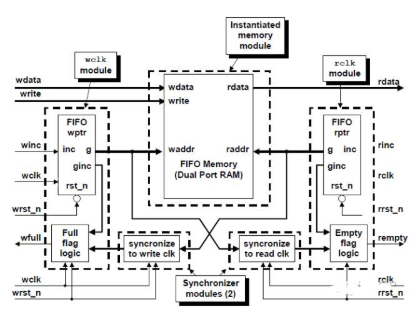

本次代码共分为6个module

1、fifo.v 是顶层模块,作用是将各个小模块例化联系起来

module fifo

#(

parameter DSIZE = 8,

parameter ASIZE = 4

)

(

output [DSIZE-1:0] rdata,

output wfull,

output rempty,

input [DSIZE-1:0] wdata,

input winc, wclk, wrst_n,

input rinc, rclk, rrst_n

);

wire [ASIZE-1:0] waddr, raddr;

wire [ASIZE:0] wptr, rptr, wq2_rptr, rq2_wptr;

// synchronize the read pointer into the write-clock domain

sync_r2w sync_r2w

(

.wq2_rptr (wq2_rptr),

.rptr (rptr ),

.wclk (wclk ),

.wrst_n (wrst_n )

);

// synchronize the write pointer into the read-clock domain

sync_w2r sync_w2r

(

.rq2_wptr(rq2_wptr),

.wptr(wptr),

.rclk(rclk),

.rrst_n(rrst_n)

);

//this is the FIFO memory buffer that is accessed by both the write and read clock domains.

//This buffer is most likely an instantiated, synchronous dual-port RAM.

//Other memory styles can be adapted to function as the FIFO buffer.

fifomem

#(DSIZE, ASIZE)

fifomem

(

.rdata(rdata),

.wdata(wdata),

.waddr(waddr),

.raddr(raddr),

.wclken(winc),

.wfull(wfull),

.wclk(wclk)

);

//this module is completely synchronous to the read-clock domain and contains the FIFO read pointer and empty-flag logic.

rptr_empty

#(ASIZE)

rptr_empty

(

.rempty(rempty),

.raddr(raddr),

.rptr(rptr),

.rq2_wptr(rq2_wptr),

.rinc(rinc),

.rclk(rclk),

.rrst_n(rrst_n)

);

//this module is completely synchronous to the write-clock domain and contains the FIFO write pointer and full-flag logic

wptr_full

#(ASIZE)

wptr_full

(

.wfull(wfull),

.waddr(waddr),

.wptr(wptr),

.wq2_rptr(wq2_rptr),

.winc(winc),

.wclk(wclk),

.wrst_n(wrst_n)

);

endmodule

2、fifomem.v 生成存储实体,FIFO 的本质是RAM,因此在设计存储实体的时候有两种方法:用数组存储数据或者调用RAM的IP核

module fifomem

#(

parameter DATASIZE = 8, // Memory data word width

parameter ADDRSIZE = 4 // 深度为8即地址为3位即可,这里多定义一位的原因是用来判断是空还是满,详细在后文讲到

) // Number of mem address bits

(

output [DATASIZE-1:0] rdata,

input [DATASIZE-1:0] wdata,

input [ADDRSIZE-1:0] waddr, raddr,

input wclken, wfull, wclk

);

`ifdef RAM //可以调用一个RAM IP核

// instantiation of a vendor's dual-port RAM

my_ram mem

(

.dout(rdata),

.din(wdata),

.waddr(waddr),

.raddr(raddr),

.wclken(wclken),

.wclken_n(wfull),

.clk(wclk)

);

`else //用数组生成存储体

// RTL Verilog memory model

localparam DEPTH = 1< reg [DATASIZE-1:0] mem [0:DEPTH-1]; //生成2^4个位宽位8的数组

assign rdata = mem[raddr];

always @(posedge wclk) //当写使能有效且还未写满的时候将数据写入存储实体中,注意这里是与wclk同步的

if (wclken && !wfull)

mem[waddr] <= wdata;

`endif

endmodule

3、sync_r2w.v 将 rclk 时钟域的格雷码形式的读指针同步到 wclk 时钟域,简单来讲就是用两级寄存器同步,即打两拍

module sync_r2w

#(

parameter ADDRSIZE = 4

)

(

output reg [ADDRSIZE:0] wq2_rptr, //读指针同步到写时钟域

input [ADDRSIZE:0] rptr, // 格雷码形式的读指针,格雷码的好处后面会细说

input wclk, wrst_n

);

reg [ADDRSIZE:0] wq1_rptr;

always @(posedge wclk or negedge wrst_n)

if (!wrst_n) begin

wq1_rptr <= 0;

wq2_rptr <= 0;

end

else begin

wq1_rptr<= rptr;

wq2_rptr<=wq1_rptr;

end

endmodule

电子发烧友App

电子发烧友App

评论