摘要:基于Xilinx芯片的FPGA集成了越来越多的可配置逻辑资源、各种各样的外部总线接口以及丰富的内部RAM 资源。在FPGA的电路设计中,上电配置电路至关重要。其中,DONE信号上拉电阻阻值的选择很容易被人忽略,错误的阻值选择往往会导致意想不到的情况。通过采用4.7 kΩ电阻上拉DONE信号产生的试验结果,来分析DONE信号上拉电阻必须为330 Ω的原因。

0.引言

随着半导体和芯片技术的飞速发展, 现在的现场可编程门阵列(Field Programmable Gate Array, FPGA)集成了越来越多的可配置逻辑资源、各种各样的外部总线接口以及丰富的内部RAM 资源, 使其在国防、医疗、消费电子等领域得到了越来越广泛的应用。但是FPGA 大多数是基于SRAM 工艺的, 具有易失性, 因此FPGA 通常使用外部存储器件(如PROM) 存储必需的配置信息, 防止设备掉电后FPGA丢失自我配置能力。但FPGA 配置在一定的条件和时间下才能成功完成, 随着FPGA 容量的不断攀升,配置时间也被大大加长, 上电时如不充分考虑FPGA的配置时序以及对其他器件的影响, 根据常规经验设计电路, 往往会影响系统其他外围器件的正常工作, 严重时会导致整个系统的失效。因此, FPGA 的配置方式和上电时序已成为系统设计的重要一环[1]。本文主要分析在FPGA上电配置过程中,因DONE上拉电阻阻值的不同而引起的不同上电结果。

1. FPGA的加载过程

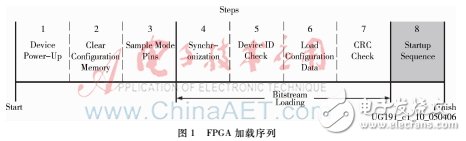

FPGA加载过程分为8个序列[1],如图1所示。

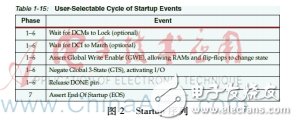

在前7个步骤完成后,配置数据的CRC校验完成,进入最后的Startup序列,Startup序列所需要处理的事件如图2所示。

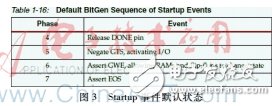

这7个事件的前后关系是可以在FPGA的目标码bit文件生成选项中进行设置的,默认的设置顺序如图3所示。

所以,默认状态下,FPGA在配置数据加载完并且通过CRC校验后,依次完成以下工作:

(1)释放DONE信号:配置数据加载期间FPGA驱动DONE信号为低,到Startup序列后FPGA将DONE信号置为高阻态,靠外部上拉电阻将DONE信号拉为高。

(2)处理GTS事件:配置数据加载期间FPGA IO管脚为高阻态(或也可由FPGA的某个配置管脚将所有IO在配置数据加载期间设置为上拉,该管脚的名字通常为PUDC_B或HSWAPEN),到Startup序列后FPGA取消IO的高阻态,使能其输出。

(3)处理GWE事件:配置数据加载期间FPGA禁止RAM的写入和flipflop状态的改变,到Startup序列后使能RAM的写入,并允许flipflop状态发生改变。

默认状态下DLL和DCI不作为Startup序列的一部分,由FPGA自行处理完成后进入Lock状态。

2.DONE信号上拉电阻与GTS事件

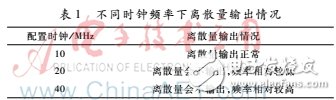

为了分析DONE信号上拉电阻阻值对上电配置的影响,本文将DONE信号上拉4.7 kΩ电阻来观察造成的结果。使用一个离散量输出作为GTS事件的标志,该离散量在VHDL源码中赋为“0”,由于FPGA电路配置为在加载期间IO上拉,从而该离散量信号在GTS事件之前时为高电平,在GTS事件后变为低电平,该信号的电平变化就标志了GTS事件的发生,离散量无变化即为GTS未发生。FPGA采用XCF32P PROM Flash的CLKOUT作为配置时钟CCLK的时钟源。默认状态下,该时钟仅可输出20 MHz或40 MHz时钟,若使用MCS压缩模式,该时钟还可以输出10 MHz时钟。

当DONE信号上拉电阻阻值为4.7 kΩ时,经过多种组合情况的测试,结果如表1所示。

通常而言,如果PCB走线较差,FPGA配置电路信号完整性不好,FPGA配置时钟频率较高时容易发生配置失败,但这通常会使配置数据载入错误,造成CRC校验错误,从而导致配置失败。而在这样配置环境中,即使采用40 MHz的配置时钟,CRC校验仍然不会发生错误,所以离散量不输出并不是信号完整性较差引发的,肯定有着与GTS事件处理直接相关的原因。

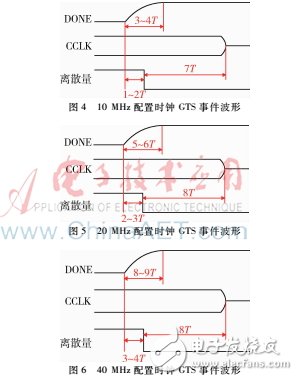

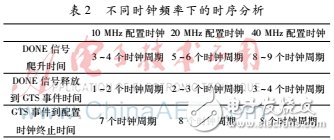

进一步对GTS事件时配置电路的行为进行波形捕获与分析,在不同的配置时钟频率下,使用示波器对该离散量、DONE信号、配置时钟进行捕获,获得波形如图4、图5、图6所示。

以上三幅图中的T表示相应情况下的时钟周期。总结分析如表2所示。

不同配置时钟频率下“DONE信号爬升时间”有所差异,DONE信号的爬升速度缓慢造成了GTS事件的失败,在较低频率的配置时钟下,DONE信号需要较少时钟周期即可为高,而在较高频率的配置时钟下,DONE信号需要较多时钟周期才能升高。所以配置时钟频率较高时,发生GTS事件失败的概率较高。

根据不同配置时钟频率下“DONE信号释放到GTS事件时间”的差异,进一步得出GTS事件的发生需要对DONE信号的电平状态进行回采,即FPGA在释放DONE信号后,并不是在下一个时钟周期立即执行GTS事件,而是要在每个时钟周期对DONE信号的状态进行采集判断,直至外部上拉电阻将DONE信号电平拉高之后才会开始执行GTS事件。

根据GTS事件到配置时钟终止时间,猜测XCF32P PROM Flash是根据FPGA的DONE信号电平状态来决定何时终止CLKOUT配置时钟的输出,待其CE#管脚采集到DONE信号为高后,再给出7~8个配置时钟周期,即终止配置时钟。

至此,对GTS事件失败的原因分析结果为:配置数据加载并校验完成之后,FPGA释放DONE信号,由外部上拉电阻将DONE信号拉为高,DONE信号开始爬升。FPGA对DONE信号的实际电平状态进行回采,待其电平为高后执行GTS事件。如果FPGA的DONE信号并未按照Xilinx手册用330 Ω电阻上拉,而使用了4.7 kΩ电阻上拉,这就造成了DONE信号爬升太过缓慢,需要配置多个时钟周期才可为高。这样的话,在FPGA对DONE信号实际电平进行回采时,即有可能因为DONE信号有回沟而采集到混乱的DONE信号状态(例如首先为高然后为低),这就可能造成GTS事件的失败,从而造成FPGA 的IO管脚无法输出,进而影响整个系统。

3.分析结果的验证

为验证以上分析,需要加快DONE信号爬升速度,来观测GTS事件失败的情况。

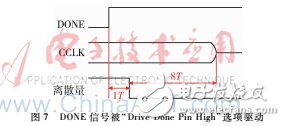

在FPGA的目标码bit文件生成选项中,选择“Drive Done Pin High”选项来使FPGA在配置数据加载并校验完成之后,并不释放DONE信号,而是主动将DONE信号驱动为高。选择该选项后,DONE信号不再需要外部上拉电阻来驱动,而是由FPGA直接从低驱动为高,在这种情况下,示波器采集所获波形如图7所示。

在这种情况下,FPGA对DONE信号实际电平进行回采时,就不会再采集到DONE信号的不定态,GTS事件不会再失败。离散量也就输出正常。

经此选项后,在40 MHz配置时钟下多次试验,GTS事件也不会再失败。

通过FPGA的目标码bit文件生成选项可以更改GTS事件和GWE事件的前后关系。如果将GWE事件与GTS事件交换位置,则会发生GWE事件失败而GTS事件成功的情况。这说明DONE信号释放后的第一个事件会受到影响,再之后的事件由于DONE信号已爬升为高,因而不会再失败。

4.结论

Xilinx不直接对DONE信号进行驱高,而是由外部上拉电阻拉高,这样可以让多个FPGA的DONE信号连在一起,回采其信号,从而可使所有FPGA都加载完成之后,同步开始工作。

Xilinx要求使用330 Ω电阻对DONE信号进行上拉的原因是,该阻值可以保证在所允许的最高频率的配置时钟下,DONE信号仍可在一个时钟周期内爬升为高,从而保证后续GTS事件的成功处理。

电子发烧友App

电子发烧友App

评论