Xilinx Block Memory Generator(BMG)是一个先进的内存构造器,它使用Xilinx fpga中的嵌入式块RAM资源生成面积和 性能优化的内存。

2023-11-14 17:49:43 736

736

51单片机C语言编程入门以及keil_uvision使用方法介绍(详讲版)

2014-09-14 18:35:44

INtime RTOS内部的关键处理机制是什么?INtime RTOS内部的关键处理机制有哪些相关的应用案例?

2021-09-29 06:28:48

上一篇系列文章“INtime可与Windows在同个PC运行的实时操作系统(上)”中我们介绍INtime实时操作系统的基本特性与功能。本篇文章将着重介绍INtime RTOS内部的关键处理机制及其

2021-07-02 06:41:14

`Xilinx Artix-7 FPGA快速入门、技巧与实例连载6——FPGA开发流程更多资料共享链接:https://share.weiyun.com/53UnQas如图1.32所示,这是一个

2019-04-01 17:50:52

Xilinx Artix7 DEVB_124X92MM 6~16V

2023-03-28 13:05:55

本帖最后由 eehome 于 2013-1-5 09:52 编辑

不可多得的Xilinx FPGA中文培训材料教程,涉及到virtel的基本架构、赛灵思设计流程、如何阅读报告、时序约束等经典

2012-03-02 09:51:53

移除并绑定到GND或VCC ???另外,我如何验证上面的块优化是否正常,我的设计仍然适用于上述块优化?请告诉我...我正在使用xilinx ise 14.1ž。以上来自于谷歌翻译以下为原文hi, i

2019-03-27 10:25:33

支持所有Xilinx器件下载 包括FPGA CPLD ISP Configuration PROM 下载接口电压:5V 3.3V 2.5V 1.8V 1.5V

2023-03-24 15:06:53

Xilinx_fpga_设计流程

2012-08-02 23:51:05

DDR 终端稳压器。它还具有一个用于加电和断电排序的LM3880。此设计采用 12V 输入电压。特性 提供 Xilinx® Zynq® 7000 系列 (XC7Z015) 所需的所有电源轨设计已经过优化,支持 12V 输入板载加电和断电排序支持 DDR3 存储器件模块设计,使用方便

2022-09-23 07:43:32

描述 PMP10601 参考设计提供为 Xilinx® Zynq® 7000 系列 (XC7Z015) FPGA供电时所需的所有电源轨。此设计使用多个 LMZ3 系列模块、多个 LDO 和一个

2022-09-28 06:24:34

的问题是:“Xilinx是否有关于MAP流程各阶段的详细开放文档?”我找不到一个。以上来自于谷歌翻译以下为原文When I do MAP on ISE 11, the process goes up

2018-10-09 15:39:10

Quartus II与ModelSim、Synplify Pro等常用EDA工具的开发流程。ALTERA CPLD FPGA设计高级篇:结合作者多年工作经验,深入地讨论了altera fpga

2020-05-14 14:50:30

本帖最后由 mr.pengyongche 于 2013-4-30 02:57 编辑

DSP2812寄存器详

2012-08-16 23:19:18

解决的方法。在这里,我们会分享大规模逻辑设计的开发流程,以及解决复杂时序问题的工程案例。此外,还将分享如何利用业界最新的大数据分析和机器学习功能来优化时序设计。3.28,让我们相聚深圳,且听资深工程师

2015-03-11 16:13:48

,而优化流程则是达到以上管理效果的一个重要手段。以下内容适用于ERP、CRM等实施中流程梳理的问题:但很多企业在开展流程优化时,却常常遇到“劳而无功”的尴尬。经常会有负责流程梳理工作的经理们抱怨说

2017-08-17 09:24:35

I/O 可优化管脚分配,从而提高布通率和信号完整性。主要优势:■ 通过采用并行流程缩短总设计时间■ 通过消除 PCB 信号层降低 PCB制造成本■ 消除由于 PCB 上的过期 FPGA符号所导致

2018-09-20 11:11:16

配置文件,接着完成下载并进行板级调试验证。图5.16 FPGA/CPLD设计简易流程 本文节选自特权同学的图书《FPGA/CPLD边练边学——快速入门Verilog/VHDL》书中代码请访问网盘:http://pan.baidu.com/s/1bndF0bt Xilinx FPGA入门连载

2019-01-28 02:29:05

FPGA设计全流程第一章Modelsim编译Xilinx库 第二章调用Xilinx CORE-Generator第三章使用Synplify.Pro综合HDL 和内核 第四章综合后的项目执行 第五章不同类型结构的仿真

2012-08-11 16:15:54

有任何其他的优化编译流程的窍门,请与我们分享。让我们一起建设更加美好的 FPGA 用户社区!了解更多 InTime 的信息,或者直接申请免费试用。关注Plunify公众号,关注FPGA设计优化。所有产品的信息和相关使用申请亦在公众号主页的菜单中,我们期待与您的交流。

2018-06-11 16:11:07

遇到一个IAR编译优化的问题:本想在profile中write callback中做特征值的有效性检查,却发现编译优化“high”和"medium"导致代码流程错误,如下

2020-03-05 07:46:50

FPGA厂商Altera和Xilinx自带的QuartusⅡ和ISE开发平台完全可以应付与之有关的开发。 整个完整的流程可以分为前端和后端两部分,前端的流程图如下: 前端的主要任务是将HDL语言描述的电路

2018-08-16 09:14:32

大家好,是不是对linux内核很感兴趣,有人是不是在跟着市面的教程,不管是收费的还是免费的,或多或少为大家讲下内核链表分析,不知道有多少人真的在本质上给您有讲.今天狄泰唐老师为你们免费讲解,总共分3

2017-07-10 18:23:35

的优化变得异常复杂,如何定位性能问题出在哪个方面,是性能优化的一大难题, 从系统入手,阐述由于系统软、硬件配置不当可能造成的性能问题,并且探讨检测系统故障和优化性能的一般方法和流程。一、CPU性能评估

2019-07-22 06:48:03

MSP430_C语言例程注释详

2017-03-12 18:59:17

用过Matlab的同学应该都知道,Matlab的慢是出了名的,但是再慢也有优化的方式,下面我们给出几个Matlab编程中常用的优化技巧。 在讲优化方法之前,首先要说的就是Matlab中用tic

2021-02-19 06:40:41

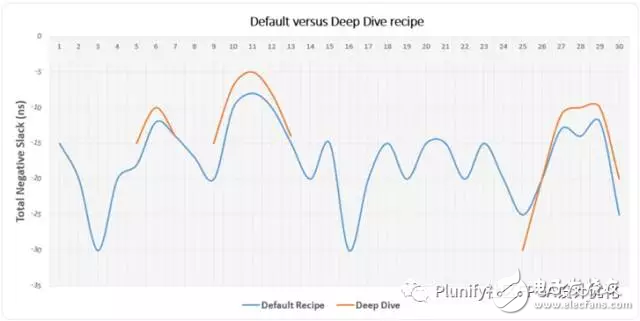

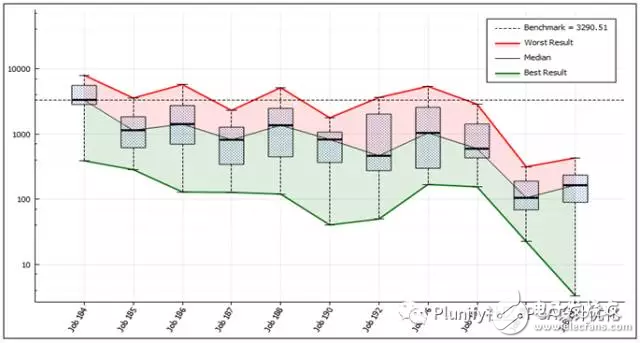

InTime 利用大数据分析和人工智能,建立时序数据库,无需修改源代码即可优化设计,为工程师推荐最佳工具参数组合。了解更多>>

2017-04-18 14:53:40

ADAPTER TC2050 FOR XILINX CABLE

2023-03-22 19:59:52

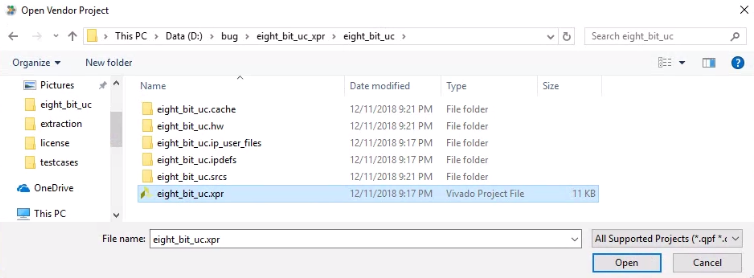

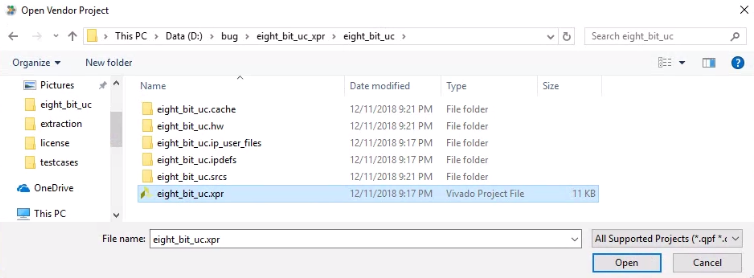

的工程,有点奇怪的是,我在笔记本上用vivado编译报TNS不满足,在台式机却是满足;既然满足了时序,我就试了试Intime对功耗的优化效果,下图是打开Intime的界面图:下图是打开Project的图

2017-06-30 15:28:28

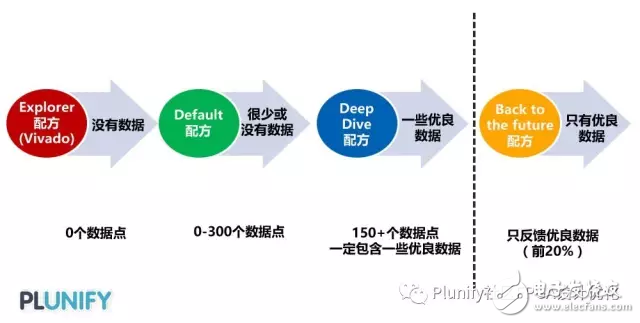

的编译综合结果,自动选择下轮运行策略。InTime运行流程如下图所示。InTime自动在本地生成专属数据库,存储相关的设计信息。初始化运行时,依据综合器的选取,自动生成策略填入综合器优化选项

2017-07-05 11:00:48

三相异步电动机的拆装详讲

2019-09-24 03:54:32

描述TIDA-00390 设计是一种经过优化的电源解决方案,适用于 Xilinx® Zynq® 7020 FPGA/SoC(属于 Zynq® 7000 产品系列)。它面向客户选择使用 FPGA 代替

2018-08-09 07:58:16

仿真技术在半导体和集成电路生产流程优化中的应用闵春燕(1)

2009-08-20 18:35:32

单片机是靠什么去读取AD的数据?讲一下大致流程

2014-11-13 11:10:01

你好,我对Xilinx工具的自下而上合成流程有一些疑问。由于我对这个领域很新,所以我只知道ISE和XST。在我的顶级设计中,我实例化了几个优化的多线程(不是库中的标准乘法器),但我不希望它们在综合

2019-03-22 06:51:51

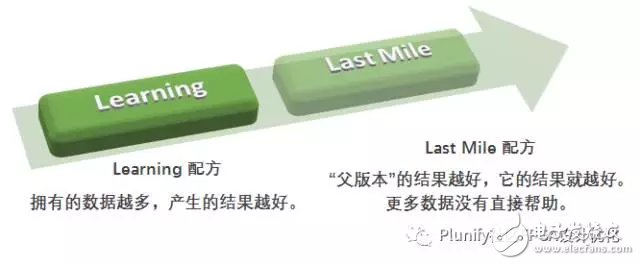

InTime,因为这个软件使用机器学习,所以比普通 FPGA 流程需要更多的数据。决定参数组合是否有效的关键是要运行很多编译。一般来说,InTime 的用户需要自己不断编译来累积设计的数据库。但是黄瀚华发现很多

2018-06-26 15:19:23

室分系统是什么?室分系统优化流程有哪几个阶段?

2021-05-20 06:26:38

前 言本文主要介绍HLS案例的使用说明,适用开发环境:Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx Vivado HLS 2017.4、Xilinx

2021-11-11 09:38:32

”,小编在电话回访过程中留意到有很多参赛选手对Xilinx 公司的FPGA及其设计流程不是很熟悉,所以想了想,最终还是决定自己动手整合一下。一方面给自己梳理梳理相关知识架构,另一方面的话,跟大家分享分享,希望

2014-11-05 13:56:42

针对目前电子发烧友网举办的“玩转FPGA:iPad2,赛灵思开发板等你拿”,小编在电话回访过程中留意到有很多参赛选手对Xilinx 公司的FPGA及其设计流程不是很熟悉,所以想了想,最终还是决定自己

2014-11-03 17:15:51

Hi,以前在学校的时候就经常遇见时序收敛的问题,尤其是改RTL好麻烦啊。工作以后和朋友们一起做了个时序优化的软件,叫InTime,希望可以帮助有相同问题的朋友。^_^我们搞了免费试用的活动,有兴趣

2017-05-11 10:55:17

使用 Quartus17.0 将这60种编译设置原封不动地也运行一遍。InTime 的 Default 配方可以从过去的结果中学习然后生成优化设计时序和资源占用率的参数。我们运行两轮是为了利用 InTime 的学习能力来得

2017-12-06 10:30:56

物理综合与优化的优点有哪些物理综合与优化流程看了就知道物理综合与优化示例

2021-04-08 06:18:15

用于Xilinx FPGA的Keysight E5910A串行链路优化工具

2019-10-16 10:49:30

电 子 DIY 过 程 详 解.pdf

2012-03-03 05:08:43

如何进行合理的PCB布板设计呢?简单讲一讲PCB Layout的设计要点

2022-02-22 06:16:49

应用及解决方案FPGA的设计流程与开发方法第二讲:Verilog基本语法与设计方法Verilog系统设计原则与技巧Verilog进行典型电路的设计第三讲:Modelsim/Questa Sim

2013-04-07 22:56:42

程序编译时采用-o3优化编译,不同函数中有相同名称的静态变量,会不会优化为同一个变量呢。另外优化会对程序流程和变量产生影响吗?

2018-09-17 14:55:02

物理综合与优化的优点是什么?物理综合与优化有哪些流程?物理综合与优化有哪些示例?为什么要通过物理综合与优化去提升设计性能?如何通过物理综合与优化去提升设计性能?

2021-04-14 06:52:32

目前xilinx 在FPGA设计上总结出了UFDM这个名词,也有ug949这篇经典的文档,将FPGA设计的流程、方法、注意事项都有详细介绍,总结了很多成功的经验,提升到设计方法学的高度。可能很多

2019-10-11 07:04:21

摘要: 如何帮助优酷迅速融合到阿里研发体系?如何优化优酷的需求分析流程?针对需求信息不明确,开发出来的功能不是产品想要的痛点如何解决?点此查看原文:[url=]http

2018-01-31 15:09:24

描述TIDA-00389 设计是一种经过优化的电源解决方案,适用于 Xilinx® Zynq® 7010 FPGA/SoC(属于 Zynq® 7000 产品系列)。它面向 ADAS 应用,在这

2018-11-19 15:00:01

EGPRS优化流程和方法:第一章 EGPRS网络优化流程 31 EGPRS网络优化流程 32 网络优化目标设定 43 网络信息收集 43.1 测试列表 4

2009-07-27 22:03:52 15

15 UML在流程工业优化调度工艺描述系统中的应用

结合建模工具Rational Rose说明如何在系统开发过程中运用UML建模。通过流程工业优化调度工艺描述系统的实际建模,对UML

2010-02-22 16:24:04 22

22 Xilinx推出行业最大容量的领域优化FPGA器件,面向通信、DSP等应用

面对市场对更大带宽的需求呈现的指数型增长态势,电子设备制造商在提升系统性能、产品更快上市方面面

2008-10-31 07:38:27 400

400 Xilinx Foundation F3.1的结构及设计流程

介绍了Xilinx Foundation F3.1可编程器件开发工具软件的组成和功能,同时介绍了该软件工具中设计入口工具和设计实现工具的主要功能

2009-03-28 15:15:47 1559

1559

以失效分析的数据作为基本数据结构,提出了测试项目有效性和测试项目耗费时间的折中作为启发信息的优化算法,提出了 芯片验证 分析及测试流程优化技术

2011-06-29 17:58:23 97

97 本文提出了一种在嵌入式Window XP(XPE)中基于INtime实时操作系统的雷达实时操控显示终端设计方案。同时充分利用Windows操作系统强大的图形界面功能,实现雷达目标、状态、原始视频、电

2011-12-21 10:09:31 1688

1688

电子发烧友网:针对目前 电子发烧友网 举办的 玩转FPGA:iPad2,赛灵思开发板等你拿 ,小编在电话回访过程中留意到有很多参赛选手对 Xilinx 公司的 FPGA 及其设计流程不是很熟悉,所以

2012-06-27 13:39:47 334

334 针对先就诊后结算 的门诊流程下需要病人预存较多诊疗费所带来的各种问题,采用了基于银行卡代缴费模式的门诊流程优化的方法,通过一所三级医院与一家国内商业银行合作开展的实

2013-03-01 15:06:54 0

0 开创性FPGA软件供应商Plunify® Pte. Ltd.今日发布其支持Altera 的FPGA和SoC的InTimeTM设计优化软件。

2014-11-21 10:54:49 1552

1552 Xilinx ISE9.1使用全流程中文书

2016-01-18 15:30:43 0

0 众所周知,Xilinx公司是FPGA芯片厂商的领导者,如今已经成立了30个年头,为我们电子开发者提供了很多优秀的迭代产品,同时不断优化的FPGA开发工具软件。但是随着互联网时代的到来,FPGA

2017-02-09 01:22:42 234

234

Plunify 将分别于2017年5月3日(成都)和2017年5月5日(长沙)的2017Xilinx All Programmable 技术研讨会。同时对于InTime时序优化工具有兴趣的朋友可以在Comtech科通展位上可以了解和参观到具体InTime的演示。

2017-04-25 15:19:55 1002

1002 1 Xilinx 的的的 EAPR 局部重构流程 EAPR(early access partial reconfiguration)与基于模块(modulebased)流程相比,有以下的主要

2017-10-18 15:12:08 22

22 1. FPGA 开发流程: 电路设计与设计输入 ;仿真验证:利用Xilinx集成的仿真工具足矣 ;逻辑综合:利用XST(Xilinx Synthesis Tool)工具 ;布局布线:利用Xilinx

2018-01-12 03:59:48 10000

10000 不断 从赛灵思FPGA设计流程看懂FPGA设计 1.XILINX ISE传统FPGA设计流程 利用XilinxISE软件开发FPGA的基本流程包括代码输入、功能仿真、综合、综合

2018-02-20 20:32:00 15820

15820

vivado 2017.2是一款Xilinx开发的功能强大的产品加工分析软件,在专业化的产品加工方面,提高产品上市的时间决定于加工的流程设计以及优化的设计方案,定制一套专业的加工流程是每一个厂家以及

2018-04-19 17:20:33 320

320 xilinx的ise的使用流程,简单介绍

2018-06-06 13:46:00 3432

3432 了解如何利用Xilinx成本优化的FPGA和SoC产品组合的最新增强功能。

2018-11-28 06:20:00 2086

2086 观看此视频,以优化和成熟的硬件参考设计的形式了解Xilinx电源传输策略的优势

2019-01-07 16:35:47 1389

1389 ISE (Integrated Software Environment)是Xilinx公司提供的用于开发其PLD产品的工具链,包括设计开发与仿真验证所需的全部功能,覆盖PLD开发的完整流程:借助该工具可以使开发人员从容地面对复杂的设计,轻松地解决各种设计难题。

2019-02-26 14:43:46 21

21 视频简介:赛灵思器件演示视频之针对 Xilinx 器件的优化电源传输方案。

2019-03-04 06:13:00 3168

3168 万幸的是,当今FPGA工具(比如Xilinx的 Vivado)都有很多开关和设置选项来帮助时序收敛。InTime的方法,就是通过调整FPGA工具的编译过程来解决用户的时序问题和其他性能问题。

2019-07-26 15:56:23 3187

3187

加州CUPERTINO - 一家有16个月历史的创业公司,名为InTime Software Inc. ,相信电子设计自动化行业已经完全错过了重要的一点,同时为开发复杂的IC创建了更强大的EDA工具

2019-08-13 11:23:39 2381

2381 对于大多数企业来说,通过优化内部流程可以节省大量资金。其中工资是大多数企业最大的财务支出,而物联网可确保这些支出物有所值。

2019-11-21 16:09:24 716

716 教程介绍 本教程旨在指导用户通过 Plunify Cloud 的云服务器,来使用 InTime 软件优化 FPGA 设计。如果您首次使用 InTime,请免费 申请该软件的本地试用 。 本教程涵盖

2020-12-21 17:57:01 1228

1228

设置芯片型号,设置源文件位置,设置生成文件位置,添加设计源文件,流程命令,生成网表文件,设计分析,生成bitstream文件。其中,流程命令是指综合、优化、布局、物理优化和布线。

2020-11-20 10:56:50 1865

1865 本文档的主要内容详细介绍的是如何使用Xilinx的FPGA对高速PCB信号实现优化设计。

2021-01-13 17:00:59 25

25 本文档的主要内容详细介绍的是LTE簇优化流程和案例介绍详细说明包括了:1无线网络优化流程簇优化的目的,2簇优化流程介绍,3簇优化的主要内容介绍,4簇优化的验收标准,5簇优化案例介绍

2021-03-02 17:11:35 9

9 电子发烧友网为你提供5G 基于路测分析优化流程资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-21 08:49:30 7

7 LTE簇优化流程和案例介绍。

2021-04-27 10:33:08 5

5 INtime RTOS简介 INtime RTOS是一个动态的,确定性的硬实时操作系统,用于多核x86兼容处理器上的非对称多处理(AMP)。与使用虚拟机管理程序,Windows设备驱动程序或单体

2021-08-10 10:58:14 3086

3086

Xilinx Zynq系列是带有ARM Cortex-A系列CPU核的FPGA,前几年流落到二手市场上的“矿板”就以Zynq 7010为核心,可以说是最廉价的Zynq实验平台了。

2023-03-14 16:13:51 1481

1481 今天推出Xilinx已发布的《Vivado使用误区与进阶》系列:用TCL定制Vivado设计实现流程。

2023-05-05 09:44:46 674

674

6月15日晚2000,虹科技术工程师许工为大家分享了“虹科实时操作系统INtime7——解决智能制造苛刻实时需求的关键RTOS”主题直播课程,课程的主要内容包括实时操作系统的必要性、虹科INtime

2023-06-21 17:23:04 514

514

螺母生产流程以及优化措施

2023-09-07 17:56:21 547

547

电子发烧友网站提供《Xilinx器件上的深度卷积优化白皮书.pdf》资料免费下载

2023-09-13 15:03:02 0

0 电子发烧友网站提供《在Xilinx器件上具有INT4优化的卷积神经网络.pdf》资料免费下载

2023-09-13 09:30:54 0

0 电子发烧友网站提供《在亚马逊EC2云端使用Xilinx工具和InTime优化设计.pdf》资料免费下载

2023-09-18 09:37:20 0

0 在制造业日益竞争激烈的今天,企业对于生产流程的优化和成本控制的需求日益迫切。SOLIDWORKS 2024以其强大的工程设计和分析功能,为生产流程的优化和成本的降低提供了有力支持。

2024-01-23 14:47:40 136

136

正在加载...

电子发烧友App

电子发烧友App

评论