介绍3种跨时钟域处理的方法,这3种方法可以说是FPGA界最常用也最实用的方法,这三种方法包含了单bit和多bit数据的跨时钟域处理,学会这3招之后,对于FPGA相关的跨时钟域数据处理便可以手到擒来。 本文介绍的3种方法跨时钟域处理方法如下:

2020-11-21 11:13:01 3278

3278

7系列FPGA拥有丰富的时钟资源。各种缓冲器类型、时钟输入管脚和时钟连接,可以满足许多不同的应用需求。选择合适的时钟资源可以改善布线、性能和一般FPGA资源利用率。BUFGCTRL(最常用作BUFG

2022-07-22 09:40:25 2475

2475 FPGA配置方式灵活多样,根据芯片是否能够自己主动加载配置数据分为主模式、从模式以及JTAG模式。典型的主模式都是加载片外非易失( 断电不丢数据) 性存储器中的配置比特流,配置所需的时钟信号( 称为

2022-09-22 09:13:59 3375

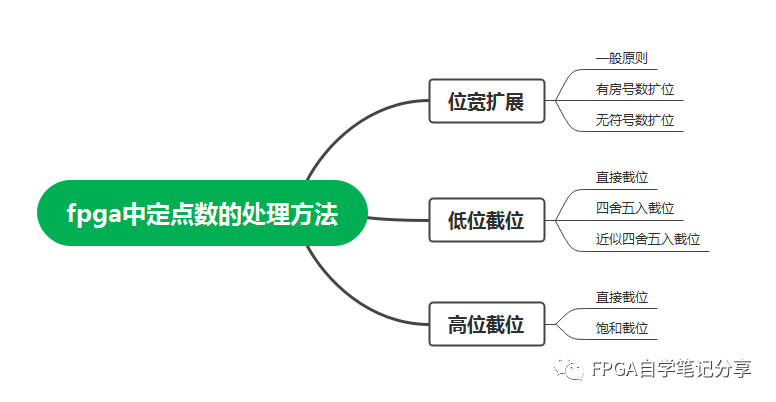

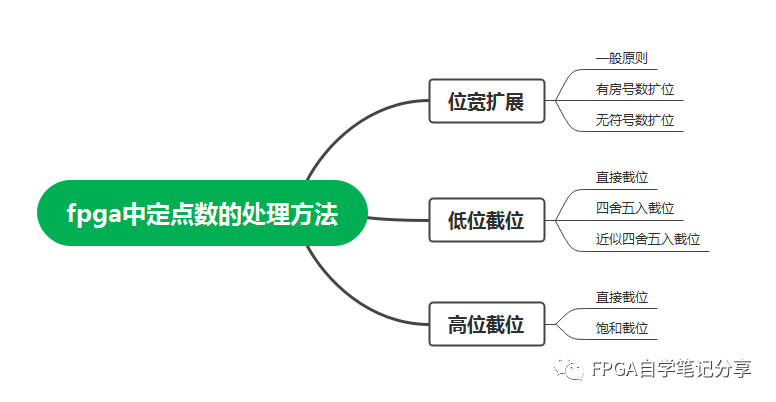

3375 FPGA中最常用的还是定点化数据处理方法,本文对定点化数据处理方法进行简要探讨,并给出必要的代码例子。

2023-05-24 15:10:05 1474

1474

` 本帖最后由 gk320830 于 2015-3-4 22:12 编辑

6种最常用恒流源电路的分析与比较`

2012-08-19 13:51:29

FPGA 设计的四种常用思想与技巧FPGA设计的四种常用思想与技巧 讨论的四种常用FPGA/CPLD设计思想与技巧:乒乓操作、串并转换、流水线操作、数据接口同步化,都是FPGA/CPLD 逻辑设计

2012-08-11 10:30:55

(10)FPGA跨时钟域处理1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA跨时钟域处理5)结语1.2 FPGA简介FPGA(Field Programmable

2022-02-23 07:47:50

产生,我们就要对亚稳态进行消除,常用对亚稳态消除有三种方式:(1) 对异步信号进行同步处理;(2) 采用FIFO对跨时钟域数据通信进行缓冲设计;(3) 对复位电路采用异步复位、同步释放方式处理

2012-04-25 15:29:59

处理的方法,这三种方法可以说是FPGA界最常用也最实用的方法,这三种方法包含了单bit和多bit数据的跨时钟域处理,学会这三招之后,对于FPGA相关的跨时钟域数据处理便可以手到擒来。这里介绍的三种方法跨

2021-03-04 09:22:51

图像细节。FPGA 图像处理方法1、图像增强两大方法:空间域方法和时间域方法(以后再详述)2、图像滤波(1)平滑空间滤波器(2)中值滤波算法3、图像边缘检测边缘指图像局部强度变化最显著的部分。边缘主要

2020-12-26 15:57:01

换、流水线操作及数据同步等;第三阶段 时序理论基本模型;时序理论基本参数;如何解决时序中的问题:关键路径的处理;跨时钟域的处理:异步电路同步化;亚稳态的出现及解决方法;利用QuarutsII提供的时序

2012-09-13 20:07:24

下面对FPGA设计中常用的复位设计方法进行了分类、分析和比较。针对FPGA在复位过程中存在不可靠复位的现象,提出了提高复位设计可靠性的4种方法,包括清除复位信号上的毛刺、异步复位同步释放、采用专用

2021-06-30 07:00:00

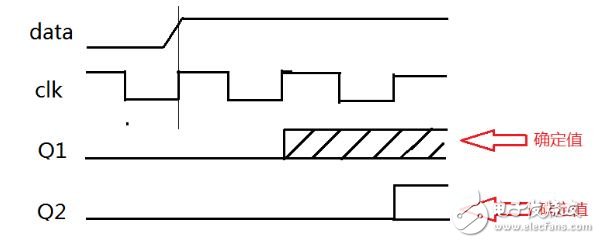

FPGA设计中有多个时钟域时如何处理?跨时钟域的基本设计方法是:(1)对于单个信号,使用双D触发器在不同时钟域间同步。来源于时钟域1的信号对于时钟域2来说是一个异步信号。异步信号进入时钟域2后,首先

2012-02-24 15:47:57

设计工作种取得事半功倍的效果。 FPGA/CPLD的设计思想与技巧是一个非常大的话题,由于篇幅所限,本文仅介绍一些常用的设计思想与技巧,包括乒乓球操作、串并转换、流水线操作和数据接口的同步方法。希望本文能

2011-10-20 09:12:36

;

四种常用FPGA/CPLD设计思想与技巧:乒乓操作、串并转换、流水线操作、数据接口同步化,都是FPGA/CPLD逻辑设计的内在规律的体现,合理地采用这些设计思想能在FPGA/CPLD设计工作种取得

2010-11-01 13:17:36

问题,异步时钟域同步化是FPGA设计者最基本的技能。[size=11.818181991577148px]我发现很多初学者没有进行同步化处理,设计的案例也能工作。[size

2014-08-13 15:36:55

玩过Linux的人都会知道,Linux中的命令的确是非常多,但是玩过Linux的人也从来不会因为Linux的命令如此之多而烦恼,因为我们只需要掌握我们最常用的命令就可以了。当然你也可以在使用时去找

2019-07-11 08:21:45

最常用的无线协议

2021-03-03 07:17:33

出现了题目中的跨时钟域的同步问题?怎么办?十年不变的老难题。为了获取稳定可靠的异步时钟域送来的信号,一种经典的处理方式就是双寄存器同步处理(double synchronizer)。那为啥要双寄存器呢

2020-08-20 11:32:06

->Core Cock Setup:pll_c0为(Latch Clock) 这两个是跨时钟域时钟,于是根据文中总结:对于跨时钟域的处理用set_false_path,约束语句如下

2018-07-03 11:59:59

1、IC设计中的多时钟域处理方法简析我们在ASIC或FPGA系统设计中,常常会遇到需要在多个时钟域下交互传输的问题,时序问题也随着系统越复杂而变得更为严重。跨时钟域处理技术是IC设计中非常重要的一个

2022-06-24 16:54:26

的特色之一,但MDO4000 绝不是以上罗列的五种测试工具的简单组合,这五种功能工作在同一时钟、同一触发机制下,使得MDO4000 具有创新的时域、频域、调制域时间相关的跨域分析功能。为此,我们将

2019-07-19 07:02:07

,讲一点最常用的知识。其它的型号大同小异。时钟含义特点HSE外部高速时钟信号一般选择外接晶振,最常用的时钟信号。电机驱动板外接12MhzHSI内部高速时钟信号由单片...

2021-08-11 07:39:56

如何克服ajax跨域

2020-04-30 13:25:07

i.MX RT 1015跨界处理器(工业级)数据手册

2022-12-13 07:05:15

i.MX RT1020跨界处理器(消费级)数据手册

2022-12-12 08:31:19

i.MX RT1050跨界处理器(消费级)数据手册

2022-12-12 07:03:51

i.MX RT 1060跨界处理器(工业级)数据手册

2022-12-12 07:14:39

i.MX RT1060跨界处理器(消费级)数据手册

2022-12-12 08:08:38

i.MX RT1064跨界处理器(工业级)数据手册

2022-12-12 08:22:07

i.MX RT600跨界处理器宣传手册

2022-12-12 07:21:12

应用处理器与MCU“跨界”处理器—从性能差距到新解决方案领域降低成本—去除片内闪存集高性能、低延迟、高能效和安全性于一体相关行业和应用 i.MX RT跨界处理器

2021-02-19 06:06:39

i.MX RT系列跨界处理器宣传手册

2022-12-12 06:37:23

i.MX RT系列跨界处理器性能优化

2022-12-12 07:51:39

双口RAM如何实现跨时钟域通信啊?怎么在quartus ii仿真???

2017-05-02 21:51:39

跨越时钟域FPGA设计中可以使用多个时钟。每个时钟形成一个FPGA内部时钟域“,如果需要在另一个时钟域的时钟域产生一个信号,需要特别小心。隧道四部分第1部分:过路处。第2部分:道口标志第3部分:穿越

2012-03-19 15:16:20

呢?如何处理好FPGA设计中跨时钟域问题?这里主要介绍三种跨时钟域处理的方法,这三种方法可以说是 FPGA 界最常用也最实用的方法,这三种方法包含了单 bit 和多 bit 数据的跨时钟域处理,学会这三招之后,对于 FPGA 相关的跨时钟域数据处理便可以手到擒来。

2020-09-22 11:23:12

处理的方法,这三种方法可以说是FPGA界最常用也最实用的方法,这三种方法包含了单bit和多bit数据的跨时钟域处理,学会这三招之后,对于FPGA相关的跨时钟域数据处理便可以手到擒来。这里介绍的三种方法跨

2021-02-21 07:00:00

时钟域处理的方法,这三种方法可以说是FPGA界最常用也最实用的方法,这三种方法包含了单bit和多bit数据的跨时钟域处理,学会这三招之后,对于FPGA相关的跨时钟域数据处理便可以手到擒来。 这里介绍

2021-01-08 16:55:23

异步bus交互(一)— 两级DFF同步器跨时钟域处理 & 亚稳态处理1.问题产生现在的芯片(比如SOC,片上系统)集成度和复杂度越来越高,通常一颗芯片上会有许多不同的信号工作在不同的时钟频率

2022-02-17 06:34:09

谢谢大家了,另外Altera FPGA从专用时钟输入port进来的时钟信号就自动会走全局时钟网络吗?

2017-07-01 10:12:36

亚稳态产生,我们就要对亚稳态进行消除,常用对亚稳态消除有三种方式:[tr][tr](1) 对异步信号进行同步处理;[tr][tr](2) 采用FIFO对跨时钟域数据通信进行缓冲设计;[tr][tr](3

2023-04-27 17:31:36

本帖最后由 zhihuizhou 于 2012-2-7 10:33 编辑

转自特权同学。 特权同学原创 这边列举一个异步时钟域中出现的很典型的问题。也就是要用一个反例来说明没有足够重视异步

2012-02-07 10:32:38

关于cdc跨时钟域处理的知识点,不看肯定后悔

2021-06-21 07:44:12

关于iFrame特性总计和iFrame跨域解决办法

2020-05-15 14:26:43

单片机最常用的四种烧写方式是什么?

2021-09-27 07:53:43

UART、 I2C 和 SPI 是单片机系统中最常用的三种通信协议。1、初步介绍SPI 是一种高速的、全双工、同步通信总线,标准的 SPI 也仅仅使用 4 个引脚,常用于单片机和 EEPROM

2021-11-18 09:22:58

单片机系统中最常用的三种通信协议是什么?

2022-02-17 06:03:46

)、MOSI(主机输出从机输入Master Output/Slave Input)和MISO(主机输入从机输出Master Input/Slave Output)。单片机系统中最常用的通信协议有三种,分...

2022-02-17 07:43:51

你好,我在Viv 2016.4上使用AC701板。我需要同步从一个时钟域到另一个时钟域的多位信号(33位)。对我来说,这个多位信号的3阶段流水线应该足够了。如果将所有触发器放在同一个相同的切片

2020-08-17 07:48:54

域产生错误的采样电平,一般使用RAM、FIFO缓存的方法完成异步时钟域的数据转换。最常用的缓存单元是DPRAM,在输入端口使用上级时钟写数据,在输出端口使用本级时钟读数据,这样就非常方便的完成了异步

2016-05-20 15:10:10

i.MX RT跨界处理器基于Adesto EcoXIP进行内存扩展

2022-12-12 07:29:32

采用FPGA来设计一款广泛应用于计算机、Modem、数据终端以及许多其他数字设备之间的数据传输的专用异步并行通信接口芯片,实现了某一时钟域(如66 MHz)的8位并行数据到另一低时钟域(如40 MHz)16

2011-09-07 09:16:40

出现问题,来自快时钟域的控制信号必须宽于较慢时钟的周期。否则如下图所示,快时钟域的控制信号无法被采样到慢时钟域。3、在时钟域之间同步数据的两种常用方法将数据从一个时钟域传递到另一个时钟域类似于传递多个

2022-04-11 17:06:57

四种常用FPGA/CPLD设计思想与技巧:乒乓操作、串并转换、流水线操作、数据接口同步化,都是FPGA/CPLD逻辑设计的内在规律的体现,合理地采用这些设计思想能在FPGA/CPLD设计工作种取得

2020-05-01 07:00:00

时钟域处理的方法,这三种方法可以说是 FPGA 界最常用也最实用的方法,这三种方法包含了单 bit 和多 bit 数据的跨时钟域处理,学会这三招之后,对于 FPGA 相关的跨时钟域数据处理便可

2020-09-22 10:24:55

介绍3种跨时钟域处理的方法,这3种方法可以说是FPGA界最常用也最实用的方法,这三种方法包含了单bit和多bit数据的跨时钟域处理,学会这3招之后,对于FPGA相关的跨时钟域数据处理便可以手到擒来。本...

2021-07-29 06:19:11

跨时钟域处理是什么意思?如何处理好跨时钟域间的数据呢?有哪几种跨时钟域处理的方法呢?

2021-11-01 07:44:59

图像细节。FPGA 图像处理方法1、图像增强两大方法:空间域方法和时间域方法(以后再详述)2、图像滤波(1)平滑空间滤波器(2)中值滤波算法3、图像边缘检测边缘指图像局部强度变化最显著的部分。边缘主要

2020-12-29 09:16:19

部分的输入尽量少;4,CPLD设计可以假定延时很小,FPGA设计延时是一定要考虑的;5,跨时钟域(哪怕是同一个PLL产生的不同时钟)时,一定要用高速时钟把低速信号打一下,可以大大提高系统延时特性;6

2012-11-02 17:47:47

嵌入式跨界处理器白皮书

2022-12-12 08:10:58

市场上最常用的欧姆龙PLC型号有哪些?

2018-01-07 15:42:32

说到异步时钟域的信号处理,想必是一个FPGA设计中很关键的技术,也是令很多工程师对FPGA望 而却步的原因。但是异步信号的处理真的有那么神秘吗?那么就让特权同学和你一起慢慢解开这些所谓的难点

2021-11-04 08:03:03

时钟域处理的方法,这三种方法可以说是 FPGA 界最常用也最实用的方法,这三种方法包含了单 bit 和多 bit 数据的跨时钟域处理,学会这三招之后,对于 FPGA 相关的跨时钟域数据处理便可

2020-10-20 09:27:37

气缸内径测量最常用的方法,精度是什么样的?

2015-12-02 09:52:14

本文根据FPGA的结构特点,围绕在FPGA上设计实现八位微处理器软核设计方法进行探讨,研究了片上系统的设计方法和设计复用技术,并给出了指令集和其调试方法,提出了一种基于FPGA的微处理器的IP的设计方法。

2021-04-29 06:38:37

现在最流行的一个词也许就是跨界了。不同行业跨界才能迸发出新火花,不同领域不同职业的人跨界才算有趣不俗套,那么汽车也要跨界才好玩,只能在地上跑的话可就太无趣了。 当一辆坦克和一艘船跨界,会产生什么样

2017-06-19 18:30:33

基于电容常用功能,详细介绍各功能应用电路中最常见到的电容使用方法

2021-03-17 08:08:35

逻辑出身的农民工兄弟在面试时总难以避免“跨时钟域”的拷问,在诸多跨时钟域的方法里,握手是一种常见的方式,而Stream作为一种天然的握手信号,不妨看看它里面是如做跨时钟域的握手

2022-07-07 17:25:02

知识转移策略的跨域故障诊断背景转移学习概述转移学习方法研究动机和问题设置跨域方法在故障诊断中的应用开源故障数据集背景数据驱动诊断方法的常用验证方式为通过将一个数据集分为训练集和测试集来保证这两个

2021-07-12 07:37:58

大家好,又到了每日学习的时候了。今天我们来聊一聊异步电路中的时钟同步处理方法。既然说到了时钟的同步处理,那么什么是时钟的同步处理?那首先我们就来了解一下。时钟是数字电路中所有信号的参考,没有时钟或者

2018-02-09 11:21:12

` 好久没发帖子了,不是本宫懈怠了人生,是因为本宫正在闭关自攻。。。。。那位公子笑得我都看见你小舌头了。。。。我说我在闭关,独自在攻克难关 时下,流行跨界,唱歌的说相声,演电视的唱歌,演小品的也唱

2016-10-21 19:03:38

` 本帖最后由 birdinskyd***sy 于 2016-10-29 10:52 编辑

各位主公,你们知道跨界有多难么?若干年前,一场雷雨,一下子劈死了我两个笔记本,一个t61的一个dell

2016-10-29 10:52:46

型的问题,并且这些问题的解决方案也有所不同。本文讨论了不同类型的跨时钟域,以及每种类型中可能遇到的问题及其解决方案。在接下来的所有部分中,都直接使用了上图所示的信号名称。例如,C1和C2分别表示源时钟

2022-06-23 15:34:45

1、高级FPGA设计技巧 有一个有趣的现象,众多数字设计特别是与FPGA设计相关的教科书都特别强调整个设计最好采用唯一的时钟域。换句话说,只有一个独立的网络可以驱动一个设计中所有触发器的时钟端口

2022-10-14 15:43:00

数字滤波是数据处理是常用、灵活、有效的方法。前面的按键程序已经用到了滤波,属于开关量滤波,这里要讨论的是模拟量滤波程序,包括最常用的两种方法,中值滤波和平均值滤波。中值滤波的原理是,每次取最近几个

2022-02-24 07:49:11

射击探测器中最常用的口径是什么?

2021-04-12 06:56:45

ht tp : / /w w w .s krp et.c o m诺基亚WP8也玩跨界 新款大屏手机曝光上周在interwebs网站泄露了诺基亚一款代号为JuggernautSemaphore原型机

2012-12-20 09:32:39

1、跨时钟域信号的约束写法 问题一:没有对设计进行全面的约束导致综合结果异常,比如没有设置异步时钟分组,综合器对异步时钟路径进行静态时序分析导致误报时序违例。 约束文件包括三类,建议用户应该将

2022-11-15 14:47:59

原则。11.同步时序设计注意事项异步时钟域的数据转换。组合逻辑电路的设计方法。同步时序电路的时钟设计。同步时序电路的延迟。同步时序电路的延迟最常用的设计方法是用分频或者倍频的时钟或者同步计数器完成所需

2019-03-08 06:30:00

”解密,无需经过等待解密的周期。跨界处理器中的这些高级加密加速器能够大幅提高加密/解密吞吐量,从而无需使用片内非易失存储器来满足安全性的需求。即使在硬件加密不适用的情况下,跨界处理器的高性能内核也可用

2018-10-30 11:17:45

40Nginx的反向代理功能解决跨域问题

2019-10-10 10:58:03

减少很多与多时钟域有关的问题,但是由于FPGA外各种系统限制,只使用一个时钟常常又不现实。FPGA时常需要在两个不同时钟频率系统之间交换数据,在系统之间通过多I/O接口接收和发送数据,处理异步信号

2023-06-02 14:26:23

最常用电池品质术语

产 品﹕過程的結果。 程 序:規定活動或過程的方法。质量﹕一組物

2009-10-22 12:19:22 653

653 工作来加以完善,其中使用喷涂机器人来进行物品表面喷漆处理就是一种常见的方法,那么卫浴喷涂机器人最常用的喷漆处理方法是什么呢?下面国辰机器人就为大家来详细介绍。 一、生产加工 它是更为大伙儿熟识的一种解决方法,低成

2020-08-04 15:09:37 702

702 跨时钟域处理的方法,这三种方法可以说是 FPGA 界最常用也最实用的方法,这三种方法包含了单 bit 和多 bit 数据的跨时钟域处理,学会这三招之后,对于 FPGA 相关的跨时钟域数据处理便可以手到擒来。 这里介绍的三种方法跨时钟域处理方法如下: 打两

2022-12-05 16:41:28 1324

1324 介绍3种跨时钟域处理的方法,这3种方法可以说是FPGA界最常用也最实用的方法,这三种方法包含了单bit和多bit数据的跨时钟域处理,学会这3招之后,对于FPGA相关的跨时钟域数据处理便可以手到擒来。 本文介绍的3种方法跨时钟域处理方法如下:

2021-09-18 11:33:49 21439

21439

(10)FPGA跨时钟域处理1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA跨时钟域处理5)结语1.2 FPGA简介FPGA(Field Programmable

2021-12-29 19:40:35 7

7 跨时钟域处理是FPGA设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个FPGA初学者的必修课。如果是还在校生,跨时钟域处理也是面试中经常常被问到的一个问题。

2022-10-18 09:12:20 3138

3138 跨时钟域是FPGA设计中最容易出错的设计模块,而且一旦跨时钟域出现问题,定位排查会非常困难,因为跨时钟域问题一般是偶现的,而且除非是构造特殊用例一般的仿真是发现不了这类问题的。

2023-05-25 15:06:00 1150

1150

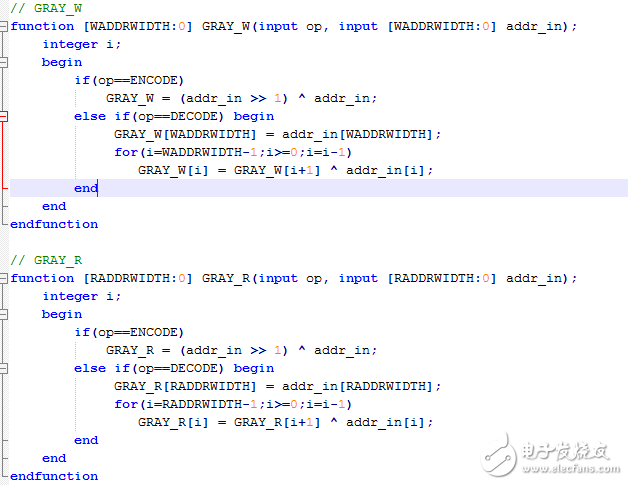

上一篇文章已经讲过了单bit跨时钟域的处理方法,这次解说一下多bit的跨时钟域方法。

2023-05-25 15:07:19 584

584

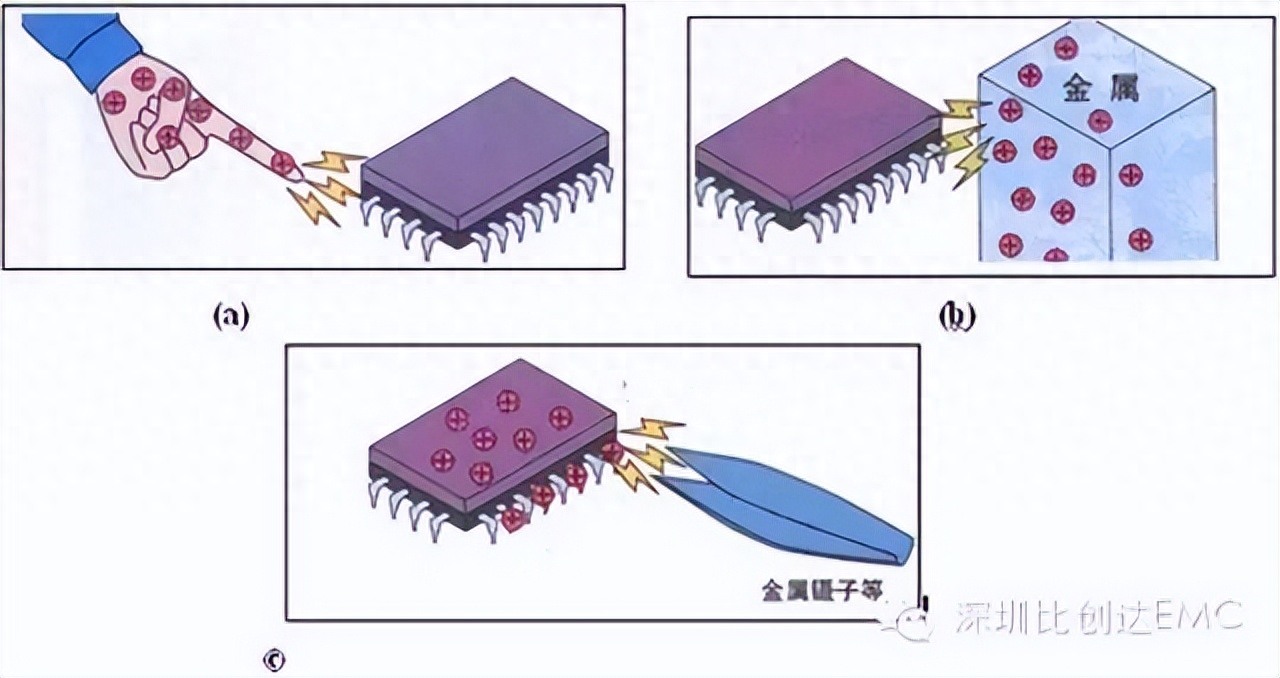

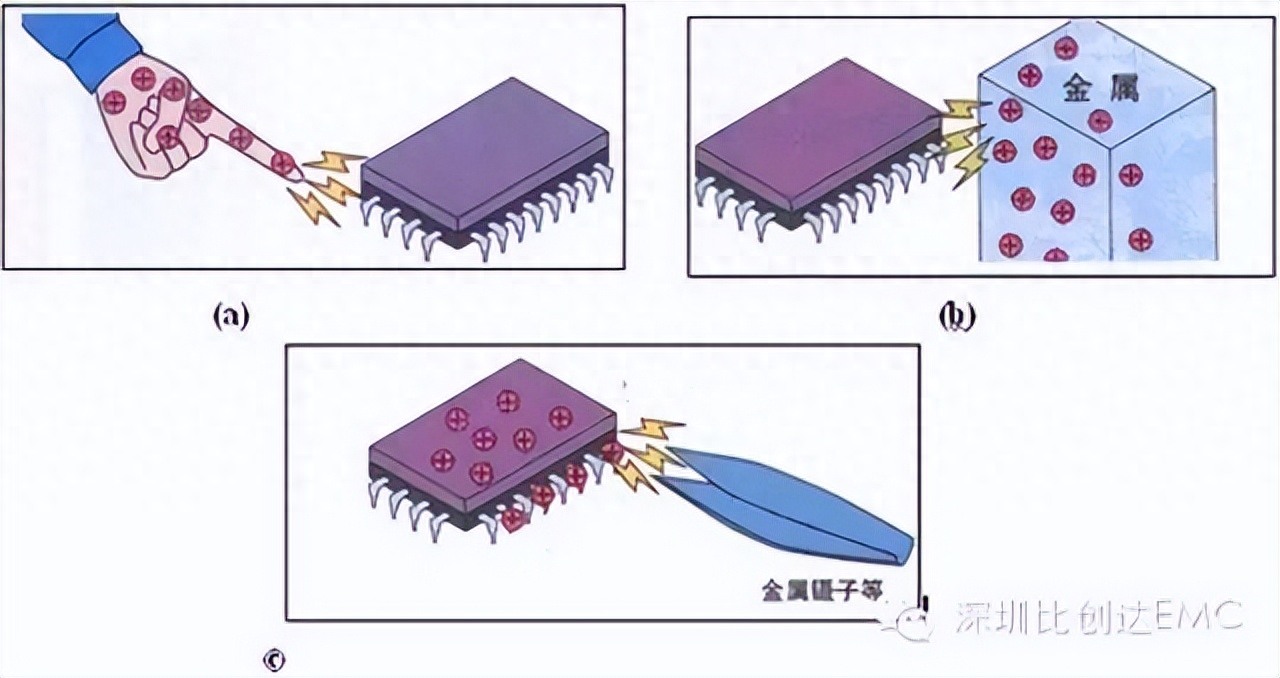

ESD最常用的3种模型?|深圳比创达EMC

2023-09-20 11:29:53 627

627

正在加载...

电子发烧友App

电子发烧友App

评论