/10b编码已经集成在数据流里面,数据本身经过加扰,绝对不可能有多于5个0或者5个1的长串(利于时钟恢复),也绝对不存在周期性(避免频谱集中)。这样,通过数据流的沿变可以直接用PLL恢复出时钟,再用恢复的时钟采集数据流。这有什么好处?时钟

2023-05-31 14:19:18 1229

1229

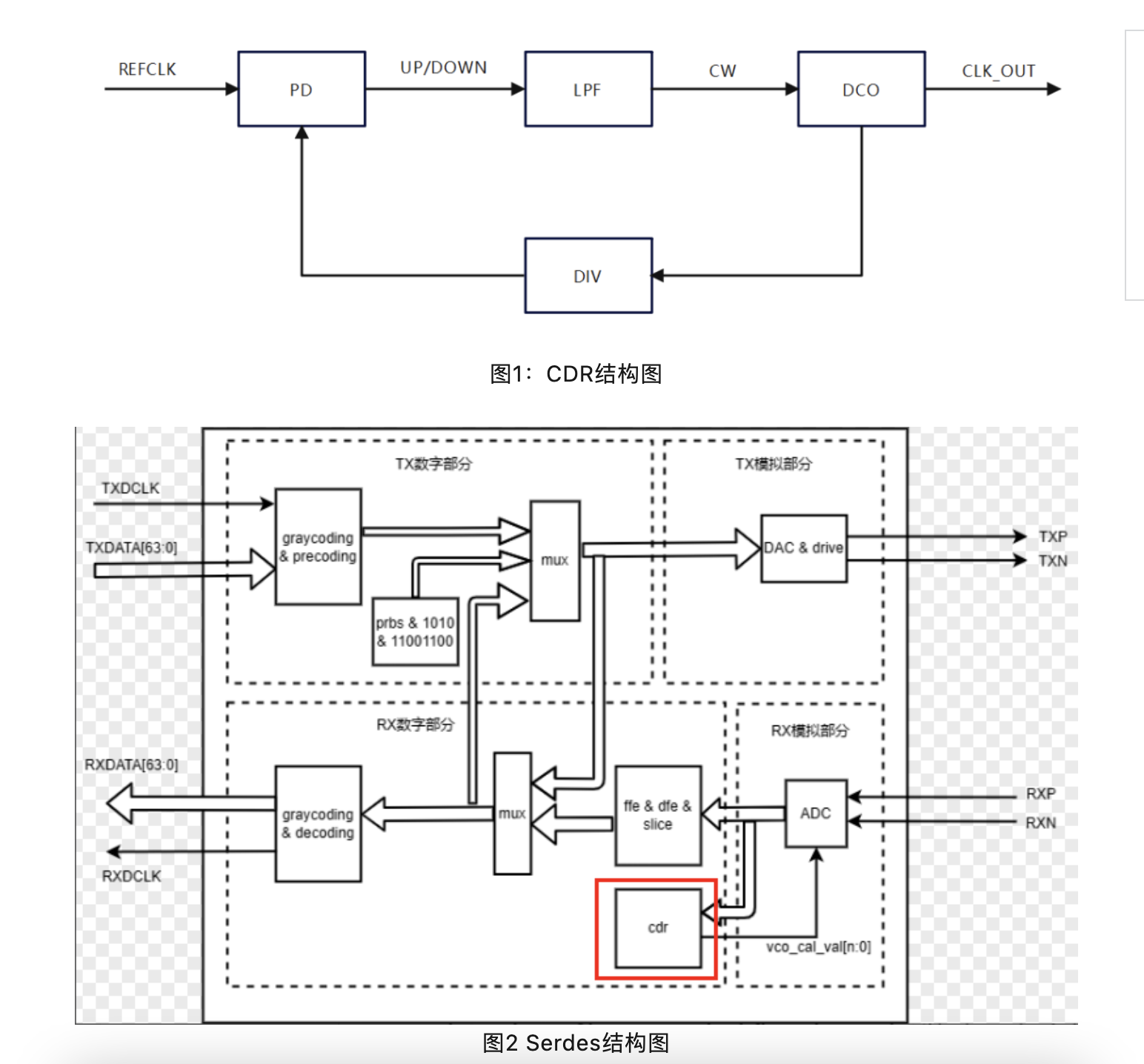

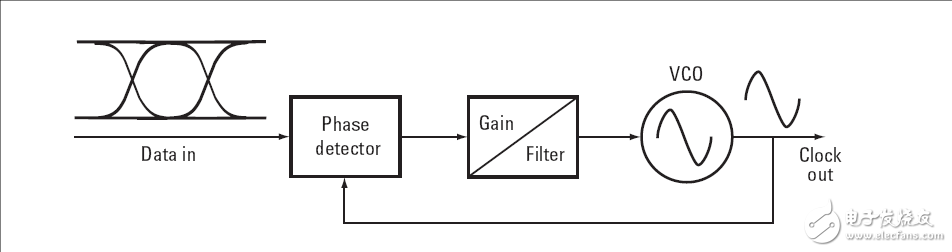

可以通过不同架构实现时钟恢复,测量设备中最常用的是基于锁相环(PLL)的方法。根据在数据中看到的跳变,使用恢复电路导出与输入数据同步的时钟,这取决于看到数据中的跳变。

2011-01-24 08:55:50 1938

1938

USB数据包的开头有同步域(SYNC),其值为00000001,在经过NRZI编码后,就是一串方波,接收方通过方波计算出时钟频率来采样后续数据。

2023-04-28 10:03:08 2052

2052

83495A Agilent 10 Gb/s 时钟恢复模块

连续数据速率:9.953 Gb/s至11.32 Gb/s

波长范围:750-860 nm或1000-1600 nm

提供光、电两种输入

2023-09-15 14:12:40

【作者】:张浩;张彧;潘长勇;【来源】:《电视技术》2010年02期【摘要】:实现了直接中频采样、数字下变频的8PSK全数字解调,分析了数字下变频、时钟恢复、载波恢复等模块的实现原理及方法。在

2010-04-23 11:16:42

8路立体声音频光端机,采用先进的数字编解码转换、FPGA、复用技术和时钟恢复技术,对立体声音频信号进行数字化处理,在一根光纤上,传输8路立体声信号源,轻松达到和超过国家广电总局批准发布

2011-03-09 20:50:02

专家你好:我对ADN2915时钟恢复功能的使用有一些疑问。 我想要利用ADN2915对信号进行时钟恢复,我没有对芯片进行写或读的操作,而是让它工作在默认状态,按数据手册上说法此时ADN2915的锁定

2018-10-29 09:21:01

16 GFC 及 InfiniBand)提供了完整的光测试解决方案,同时提供了通用光器件测试功能。 其它模块功能包括光电转换器、平均功率监测仪、一台或多台参考接收机滤波器、全带宽光路径、选配集成时钟恢复

2018-10-12 14:59:13

。 80C07B 可以选配支持 125、155、622、1063、1250、2125、2488、2500 和 2666 Mb/s 速率的时钟恢复功能。80C08D 多速率宽波长高灵敏度 10 Gb/s 模块

2022-02-23 09:53:09

比较器将网线传输过来的差分信号转为单端信号,该信号时钟频率为100M,电平标准能满足FPGA的输入电平标准,波形质量尚可。单端信号直接连接到FPGA,现在如果想用FPGA直接采集,应该怎么处理呢,是当作异步信号直接打拍吗,过采样的话时钟频率不够。时钟恢复目前来不及实现。

2020-03-07 16:01:37

和最常用的NRZ码(Non—Return Zero,非归零码)相比,HDB3码具有很多优点,例如:消除了NRZ码的直流成分,具有时钟恢复和更好的抗干扰性能,这使它更适合于长距离信道传输。

2019-09-26 09:12:23

`广播专业AES系列数字音频光端机,采用先进的广播和通信专业芯片。使用先进的FPGA、多路时分复用和时钟恢复技术。输入自动均衡,时钟恢复,低抖动,透明传输完整AES格式信息。在1芯光纤上,传输10路

2011-03-13 22:54:43

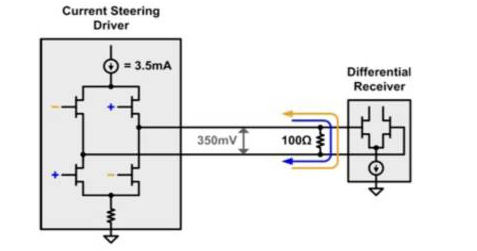

面,而差分信号一定要走两根等长、等宽、紧密靠近、且在同一层面的线。这样的情况常常发生在芯片的管脚间距很小,以至于只能穿过一根走线的情况下。二、时钟数据恢复时钟恢复( CDR: clock data

2019-07-10 07:30:00

的精细定时分辨率选配应用支持Agilent/安捷伦83496A 光/电时钟恢复模块,50 Mb/s – 7.1 Gb/sAgilent/安捷伦83496A 光/电时钟恢复模块,50 Mb/s – 7.1

2020-12-09 10:59:20

(TDR/TDT),用于包括S参数的高精度阻抗分用户可进行配置:主机插槽可支持 两个模块(4个光通道或电通道)先进的一键式简单测量触发带宽大于13 GHz(选件001)时钟恢复功能具有可调节的环路带宽

2021-04-08 17:01:28

回收 电时钟恢复 Keysight N1076B 欧阳R:*** QQ:1226365851回收工厂或个人、库存闲置、二手仪器及附件。长期 专业销售、维修、回收 高频 二手仪器。温馨提示:如果您

2019-06-30 12:17:18

extinction testing of EDFA noise figure..Built-in coherence control.Built-in isolatorAgilent 83497A 光电时钟恢复

2020-07-06 09:25:58

; 50 fs 典型值);可调节时钟恢复峰值和环路带宽灵活的仪器配置可以缩短开发时间。仪器配有集成的时钟恢复(50 Mb/s 至 32 Gb/s 数据速率)、集成的传感器,以及相位匹配电缆。这种电缆适用于

2020-07-09 09:03:07

摘要:随着石油勘探的发展,在地震勘探仪器中越来越需要高精度的同步技术来支持高效采集。基于这种目的,采用FPGA技术设计了一种时钟恢复以及系统同步方案,并完成了系统的固件和嵌入式软件设计。通过室內测试

2019-06-18 08:15:35

嗨,我目前正在构建用于差分曼彻斯特码(CPD / CMI)的时钟恢复模块。我正在使用具有Clock_Hold功能的时钟向导,因为在任何时候都不会有数据来恢复时钟。首先,我与第一个接收到的数据同步,当

2020-06-12 11:28:47

你好!所以我知道CyPress做USB音频的时钟恢复。我想知道它是否为另一个来源,如果我可以使用一个GPIOS来给时钟恢复,IM现在使用CS2000时钟恢复,但现在我想使PSOC4只。谢谢!

2019-10-10 10:51:59

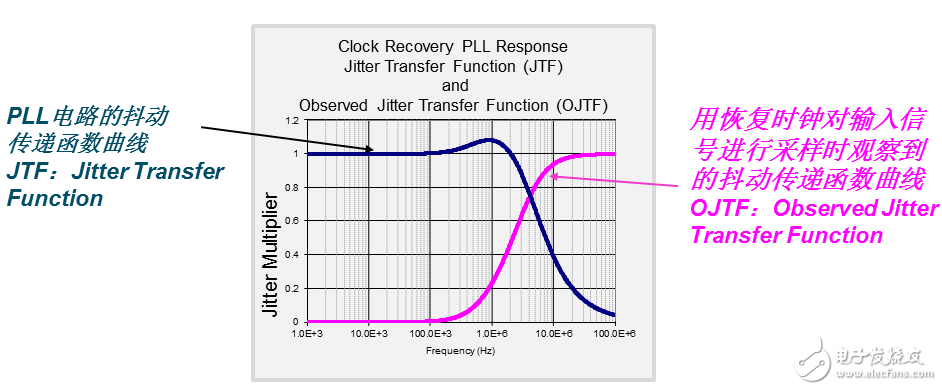

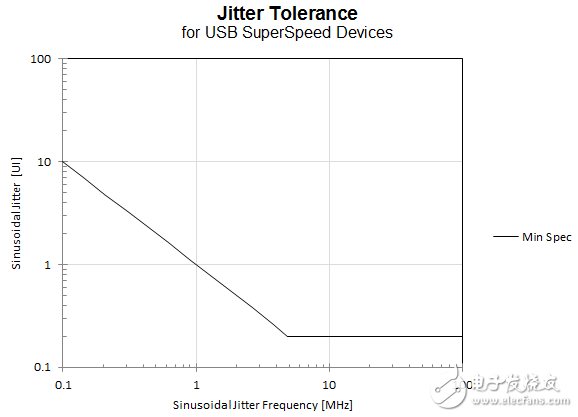

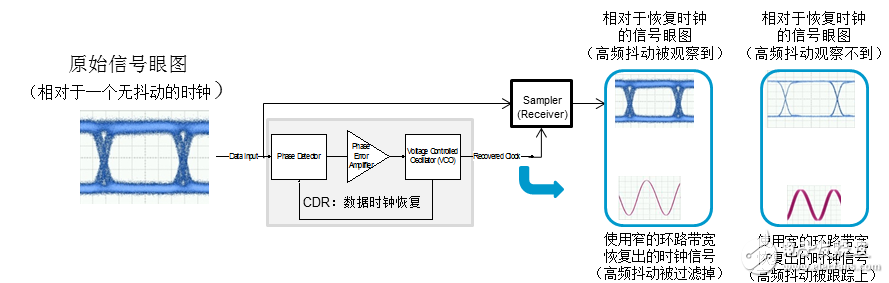

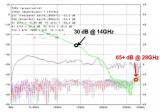

CDR电路原理环路带宽对眼图、抖动测量的影响测试中时钟恢复方式的选择

2021-02-24 06:51:53

码间干扰。如果信号速度足够快,超出示波器的带宽,那么滚降速度较快的平坦响应会出现振铃。不论哪种情况,用户必须了解硬件对测量的影像。 时钟恢复的区别 时钟恢复是示波器测量的关键因素。它支持构建实时眼

2018-04-26 10:44:44

(Accredited)Agilent/安捷伦83496A 光/电时钟恢复模块,50 Mb/s – 7.1 Gb/sAgilent/安捷伦83496A 光/电时钟恢复模块,50 Mb/s – 7.1

2020-12-09 11:14:09

灵敏度时更换电缆。 ■宽带工作频率 内置支持从125 Mbit/s到12.5 Gbit/s的比特率的选件,这种集所有功能于一身的方案支持不同速率的应用,包括STM-1到10 GbE。 ■时钟恢复

2022-02-11 13:49:58

同Agilent/安捷伦83496A 光/电时钟恢复模块,50 Mb/s – 7.1 Gb/sAgilent/安捷伦83496A 光/电时钟恢复模块,50 Mb/s – 7.1 Gb/sAgilent

2020-12-09 11:09:43

方法。首先示波器采集到一长串连续的数据波形;然后使用软件CDR恢复时钟用恢复的时钟切割每个比特的波形从第1个、第2个、第3个、一直到第n-1个、第n个比特;最后一步是把所有比特重叠得到眼图。其中实时

2019-10-10 14:36:04

E1音频编解码器,是汉源高科采用数字处理芯片及数字编解码转换和时钟恢复技术方法设计的,音频接口XLR(卡侬座)。适用于广播节目源传输的设备。音频编码器是将输入的立体声音频信号或AES/EBU数字音频

2022-06-21 11:04:19

采用一种新的时钟增强方案并配合双区折射率耦合激光器实现非归零码信号的全光时钟恢复,通过数学仿真研究了此时钟恢复系统在64 Gb/s非归零码系统中的性能表现。仿真结果表

2009-03-04 10:38:27 19

19 TEL:主要特性与技术指标光时钟恢复(选件101)输入和输出:9/125 μm(单模)至62.5/125 μm(多模)波长范围:1250-1650 nm(单模)、750-1330 nm

2022-08-09 17:14:51

HDB3 码无直流分量,具有时钟恢复和较好的抗干扰能力。本文提出使用HDB3码用于高速长距离的数据传输, 并给出使用单片机AT89C51 控制E1 收发芯片DS2153Q 实现NRZ-HDB3 的码制转换,包括

2009-04-15 11:31:16 19

19 TRU-050是VECTRON公司生产的具有时钟恢复和数据重定时、频率转换、时钟平滑三种功能的器件.本文介绍该器件的特点和功能,并给了实际应用电路.

2009-04-21 16:40:48 18

18 SY87700L是MICREL公司推出的一种完整的、可将数据速率从32-175Mbps的NRZ数据流中进行恢复的反相不归零时钟恢复和数据重定时电路芯片,可广泛应用于SONET/SDH/ATM、高速英特网和其它所

2009-04-25 15:51:45 28

28 电 NRZ 和 PAM-4 数字信号上的 50 MBaud 至 32 GBaud 数据速率范围(连续)提供符合标准的时钟恢复(“最佳锁相环”)包括可调整环路带宽(高达 20 MHz)和峰值抖动频谱

2022-10-09 17:04:06

83496B 光/电时钟恢复模块 获得突破性的光时钟恢复性能 配有输入和输出的选件 101:9/125 米(单模)至 62.5/125 米(多模);波长范围:1250-1650 nm(单模

2022-10-09 17:07:59

光时钟恢复(仅限选件101)输入和输出:9/125 µm(单模)至62.5/125 µm(多模)波长范围:1250-1650 nm(单模)、750-1330 nm (多模)最小光调制幅度:-11

2022-10-09 17:10:05

标准 83495A是适用于 86100 Infiniium数字通信分析仪的独特时钟恢复模块。它提供9.953Gb/s至11.32 Gb/s所有速率的光和电

2022-10-09 17:12:28

; 83494A 单模时钟恢复插入式模块是一款用于高速数字传输测试的综合解决方案。深圳市美佳特科技有限公司(简称“美佳特”)成立于2010年,致力于光通讯测试、通用电子测量

2022-10-09 17:14:27

插入测试信号,选择数据速率,然后进行测量。 9/125光纤的光时钟恢复波长范围:1200-1600 nm数据速率:0.155/0.622/1.250/2.

2022-10-09 17:16:37

本文主要设计了基于相位控制技术的时钟恢复系统的PLL 锁相环路。分别对各单元电路结构——鉴频鉴相器、电荷泵、环路滤波器、压控振荡器、分频器进行设计。采用2.5V,0.25μm

2009-06-01 15:51:53 54

54 N1077A 光/电时钟恢复模块为从 50 MBd 到 16 或 32 GBd 的 PAM4 和 NRZ 单模和多模光信号及电信号提供符合标准的时钟恢复功能。 在光电设计中提供 50

2022-11-15 16:20:47

是德 Keysight N1078A 光/电时钟恢复模块为从 125 MBd 到 64 GBd 的 PAM4 和 NRZ 单模光信号及电信号提供符合标准的时钟恢复功能。 拥有

2022-11-15 16:23:17

本文详细介绍了E1 信号基本帧和复帧的结构,以及基本帧和复帧的同步算法,并对E1 接口的时钟恢复,码型转换实现做了具体介绍。同时对各种告警信号的产生做了详细阐述。采用VH

2010-01-20 11:45:18 24

24 DS26503是一个楼宇综合定时供给系统(BITS)时钟恢复元件,还可用作基本T1/E1收发器。接收部分可从T1, E1和6312kHz同步时序接口中恢复时钟。在T1和E1模式下,还可恢复出同步状态

2023-07-18 08:58:07

锁相环(PLL)是集成电路中非常重要的模块,常常用来实现时钟倍频,时钟综合,抖动衰减,数据时钟恢复等功能。PLL是一个非线性的离散系统,很难准确刻画。在一定的条件下—

2010-06-08 08:04:31 28

28 锁相环(PLL)是集成电路中非常重要的模块,常常用来实现时钟倍频,时钟综合,抖动衰减,数据时钟恢复等功能。PLL 是一个非线性的离散系统,很难准确刻画。在一定的条

2010-06-08 08:21:29 10

10 概述AE400系列E1接口音频编解码器,是采用先进数字处理芯片,使用先进的FPGA、数字编解码转换和时钟恢复技术方法设计的。适用于广播节目源传输的设备。音频编码器是将输入

2010-07-05 15:48:46 55

55 在数字通信系统中,由于有高斯噪声和多径的影响,接收信号产生损失,从而导致时钟信号的提取更加困难,而时钟信号的不准确性会降低整个系统的性能。本文我们给出一种改进

2010-08-03 17:04:27 33

33 特点:在光电设计中提供 50 Mbaud 至 32 Gbaud 数据速率范围(连续)为 NRZ 和 PAM-4 数据信号提供符合标准的时钟恢复(CR)功能通过集成分路器和分立光耦合器(选件 SMS

2024-03-15 16:34:38

fs 典型值);可调节时钟恢复峰值和环路带宽·灵活的仪器配置可以缩短开发时间。仪器配有集成的时钟恢复(50 Mb/s 至 32 Gb/s&nb

2024-03-20 14:06:47

HDB3码无直流分量,具有时钟恢复和较好的抗干扰能力。本文提出使用HDB3码用于高速长距离的数据传输,并给出使用单片机AT89C51控制E1收发芯片DS2153Q实现NRZ-HDB3的码制转换,包括码转换器的电路设计和控制软件设计。

2006-03-11 13:25:32 2263

2263

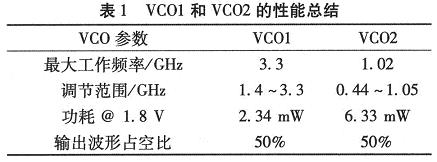

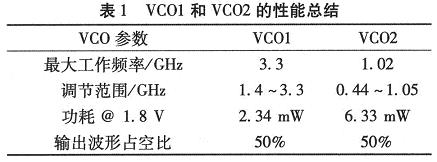

两种高频CMOS压控振荡器的设计与研究

锁相环在通讯技术中具有重要的地位,在调制、解调、时钟恢复、频率合成中都扮演着不可替代的角色。可控振荡器是锁相环的

2009-12-25 10:03:55 2517

2517

基于FPGA的SoftSerdes设计与实现

0 引言

在高速源同步应用中,时钟数据恢复是基本的方法。最普遍的时钟恢复方法是利用数字时钟模块(DCM)

2009-12-28 09:23:40 920

920

本文涉及的锁相环路是基于相位控制的时钟恢复系统。目的是用锁相环电路-PLL和DLL实现USB2.0收发器宏单远UTM的时钟恢复木块。其中PLL环路构成的时钟发生器奖外部晶振的12MHZ的正弦信号

2011-03-03 14:58:34 50

50 摘要:本文主要介绍在以太网远程网桥中多路E1 信号输入情况下的数据缓存、时钟恢复、信号 编码转换以及NIOS 处理器平台的设计,并用 Altera 的 Cyclone 器件实现的整个过程。包括 简单

2011-04-06 16:40:23 43

43 光学发射机发送波形一致性测试要求中包括需要新的参考接收机及采用标准时钟恢复单元,其中参考接收机要有严格控制的频响及19.34GHz的3 dB带宽,时钟恢复单元要有10 MHz PLL环路带宽及

2011-08-08 16:46:40 1398

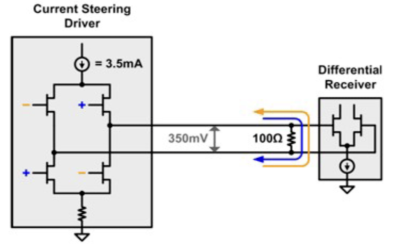

1398 Today in many applications such as network switches, routers, multi-computers,and processor-memory interfaces, the ability to integrate hundreds of multi-gigabit I/Os is desired to make better use of the rapidly advancing IC technology.

2012-03-08 14:52:54 0

0 安捷伦科技公司日前宣布推出一系列新型仪表级时钟恢复解决方案,非常适合对高速数字通信元器件和系统进行光和电测试。该解决方案以显著低于同类产品的价格提供业界最高带

2012-03-27 17:04:19 606

606 PCIE 3.0相对于它的前一代PCIE 2.0的最主要的一个区别是速率由5GT/s提升到了8GT/s。为了保证数据传输密度和直流平衡以及时钟恢复,PCIE 2.0中使用了8B/10B编码,即将每8位有效数据编码为10位

2012-12-03 11:45:13 55

55 基于紫外线发光二极管(UV LED)设计了一个紫外光通信系统,为此研究了光路设计、时钟恢复、信道编码等内容,并重点设计了双工传输协议,用较小的资源实现了4.8Kb/s信息的传输。该系统可以用于近距离语音和数据的双向保密传输。 紫外光通信具有非常好的非视距传输和保密性能。

2016-11-05 08:09:03 1910

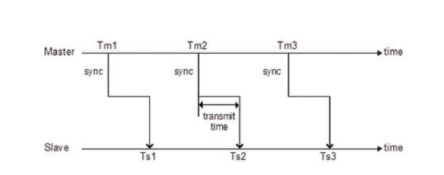

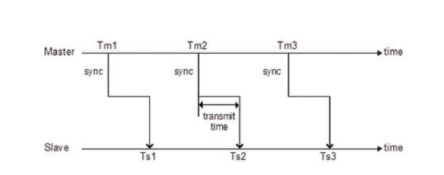

1910 在前一篇文章中,我研究了软件中处理时钟的基本知识。在本文中,我们将继续讨论全球时钟恢复、分布式时钟同步和事件同步。

2017-06-27 14:50:03 5

5 Agilent83493A为你省钱83493A光时钟恢复模块83493A/李S 158-8930-0966=======================================深圳

2017-10-09 14:52:50 1183

1183 随着石油勘探的发展,在地震勘探仪器中越来越需要高精度的同步技术来支持高效采集。基于这种目的,采用FPGA技术设计了一种时钟恢复以及系统同步方案,并完成了系统的固件和嵌入式软件设计。通过室內测试、野外

2017-11-18 06:28:42 1330

1330

可能有多于5个0或者5个1的长串(利于时钟恢复),也绝对不存在周期性(避免频谱集中)。这样,通过数据流的沿变可以直接用PLL恢复出时钟,再用恢复的时钟采集数据流。

2018-01-25 16:35:01 2893

2893

,其中PMA子层包含高速串并转换(Serdes)、预/后加重、接收均衡、时钟发生器及时钟恢复等电路。PCS子层包含8B/10B编解码、缓冲区、通道绑定和时钟修正等电路。对于GTX的发送端来说,结构如图1所示。

2018-06-20 13:48:00 2709

2709

高速比较器常在数字系统中用来恢复失真的时钟波形。LTC6752-2 分离的输入 / 输出电源特性使其可在那些需要把信号从一个电压域转移至另一个电压域的应用中使用。图中示出了一款兼具恢复和电平

2018-06-29 19:06:58 837

837 主要特性和功能通过出色的仪器性能获得更大裕量:高带宽(50 GHz 或 35 GHz)接收机、超低剩余抖动(< 50 fs 典型值);可调节时钟恢复峰值和环路带宽灵活的仪器配置可以缩短开发时间。仪器

2018-09-21 22:19:28 159

159 主要特性与技术指标标准的光纤通道、千兆位以太网和ATM/SONET/SDH,速率从155 Mb/s到2.5 Gb/s具有较慢或非标准速率的数据触发回复时钟和再生数据电输出兼容是德无源和有源探头我公司

2018-09-25 11:19:45 181

181 主要特性与技术指标标准的光纤通道、千兆位以太网和ATM/SONET/SDH,速率从155 Mb/s到2.5 Gb/s具有较慢或非标准速率的数据触发回复时钟和再生数据电输出我公司主营测试仪器的回收

2018-09-25 11:25:31 174

174 主要特性与技术指标Optical clock recovery for 9/125 fibersWavelength range: 1200-1600 nmData rates: 0.155/0.622/1.250/2.488/2.500 Gb/sPLL bandwidth: 50 to 70 kHz (internal triggering), 4 to 5 MHz (external output)Input power: -20 to +3 dBmCompatibility86100A/B Infiniium DCA Mainframes86100C Infiniium DCA-J Mainframe86100D Infiniium DCA-X Mainframe描述The 86100 family of wide-bandwidth oscilloscopes offers single connection measurements - no external trigger is required. With the addition of the Keysight 83491/92/93/94A series of clock recovery receiver modules, reliable parametric testing becomes easy even when you do not have access to a clock signal.The Keysight 8349X series of plug-in receiver modules cover the three most popular transmission media in use today - electrical lines, multimode fiber and single-mode fiber. A built-in coupler/splitter reduces external hardware required for triggering. No more need for awkward cables just to get a trigger - simply plug in your test signal, select your data rate, and make your measurements.我公司主营测试仪器的回收、销售、维修、租赁等业务,欢迎来电咨询洽谈,联系方式如下:法澜克仪器设备(深圳)有限公司联系电话:0755-23357287企业网址:http://www.falank.com联系人:魏先生手机:18689488394(微信同号)地址:广东省深圳市宝安区石岩街道金三角商务大厦306

2018-09-25 11:28:56 202

202 主要特性与技术指标标准光纤通道、千兆位以太网和ATM/SONET/SDH的速率从155 Mb/s到9953 Mb/s具有较慢或非标准速率的数据触发回复时钟和再生数据电输出我公司主营测试仪器的回收

2018-09-25 11:32:23 207

207 802.3ae标准描述83495A是适用于 86100 Infiniium数字通信分析仪的独特时钟恢复模块。它提供9.953Gb/s至11.32 Gb/s所有速率的光和电连续时钟恢复,包括新出现

2018-09-25 11:37:23 237

237 主要特性与技术指标光时钟恢复(仅限选件101)输入和输出:9/125 µm(单模)至62.5/125 µm(多模)波长范围:1250-1650 nm(单模)、750-1330 nm (多模)最小

2018-09-25 11:43:14 214

214 主要特性和功能获得突破性的光时钟恢复性能配有输入和输出的选件 101:9/125 米(单模)至 62.5/125 米(多模);波长范围:1250-1650 nm(单模)、750-1330 nm

2018-09-25 11:46:29 146

146 长久以来,工程师们在进行光接口测试(尤其是光模块测试)时都不担心同步触发时钟,要么从码型发生器(Pattern Generator)引过来、要么使用时钟恢复单元(Clock Recovery)从被测信号上恢复时钟。情。

2019-04-06 15:08:00 4306

4306

2016年将是14 th 年的The Jitter Panel(以及通过我们的营销部门过滤的官方标题是闭幕式的案例)由Chris Loberg主持并执行(或许是真的,你们将开始我们称之为DesignCon的年度家庭聚会。该小组让测试和测量大师面对面地面对来自最具挑战性的客户的问题。不同的是,这一次,T&amp; M的人没有预先计划好的商品销售 - 没有很多新的自动化测试,更疯狂的缩略词,更高的带宽,相互矛盾的产品名称 - 不,这次他们在学校舞蹈中,更像是困惑的7 th 年级学生。他们想跳舞,但他们不知道如何吸引ASIC和FPGA设计师到场。

2019-08-08 16:08:06 2338

2338

安捷伦示波器DCA-J 86100C搭配光采样模块86105C、电时钟恢复模块83496B,可以实现对光纤中的以太网信号质量分析。

2020-10-21 10:41:57 1383

1383 电子发烧友网为你提供时钟恢复方式的选择资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-05 08:40:15 18

18 AD808:带量化器和时钟恢复和数据重定时数据表的光纤接收器

2021-04-28 17:09:08 2

2 ,每个器件缺一不可,那么光模块内部包含哪些器件呢? 光模块的主要器件包括: ①CDR(Clock and Data Recovery) 即时钟恢复功能,传输到模块的信号提取时钟信号,并找出时钟信号和数据中间的相关关系。一般时钟恢复功能在长距离的传输

2021-05-19 10:59:12 7214

7214 AD800/AD802:时钟恢复和数据重定时锁相环数据表

2021-05-18 14:11:56 9

9 AD807:带量化器和时钟恢复和数据重定时数据表的光纤接收器

2021-05-19 08:29:38 12

12 传统电信网络是个同步网络,电信局间和各局内部都要保持同步状态。因此必须有一个同步分配系统来保证经过线路传输的信号仍然可以保持原始的同步关系。在一个 PDH网络中,从T1或E1线路上恢复出时钟信号

2021-05-31 10:09:21 2132

2132

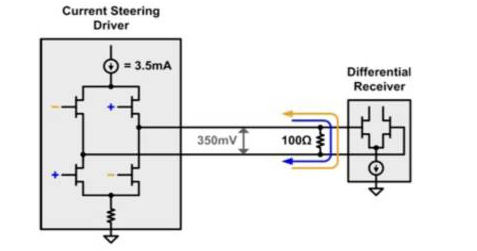

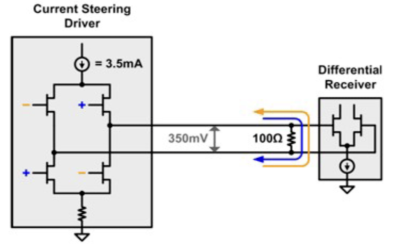

对于高速的串行总线来说,一般情况下都是通过数据编码把时钟信息嵌入到传输的数据流里,然后在接收端通过时钟恢复把时钟信息提取出来,并用这个恢复出来的时钟对数据进行采样,因此时钟恢复电路对于高速串行信号的传输和接收至关重要。

2022-02-09 10:43:43 6

6 对于高速的串行总线来说,一般情况下都是通过数据编码把时钟信息嵌入到传输的数据流里,然后在接收端通过时钟恢复把时钟信息提取出来,并用这个恢复出来的时钟对数据进行采样,因此时钟恢复电路对于高速串行信号

2022-02-11 15:05:26 8

8 在以太网通信的情况下,使用 IEEE 802.1as 作为时间同步协议,XMOS XCore 设备作为代理,同步误差可以小于 150 ns。

2022-08-12 10:34:59 1197

1197

您是否碰到过明明眼图质量优异,但是误码率很高的情况?

2022-09-16 10:46:00 2856

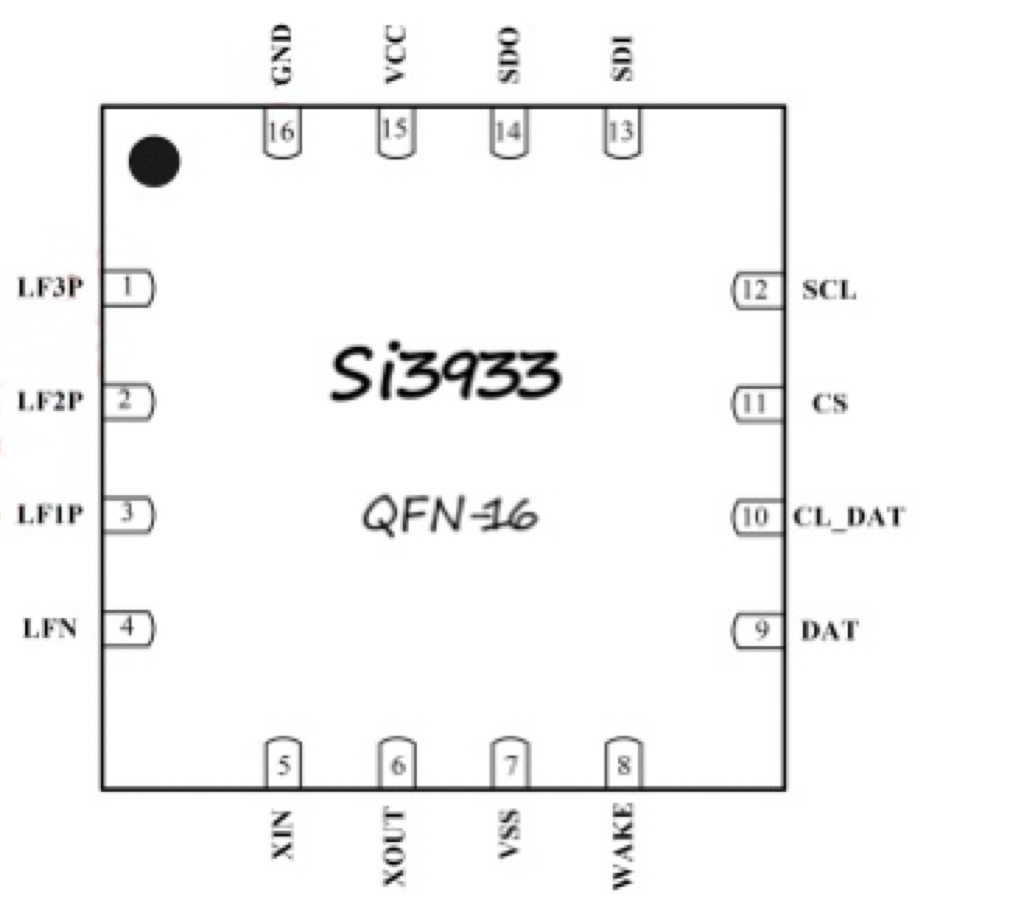

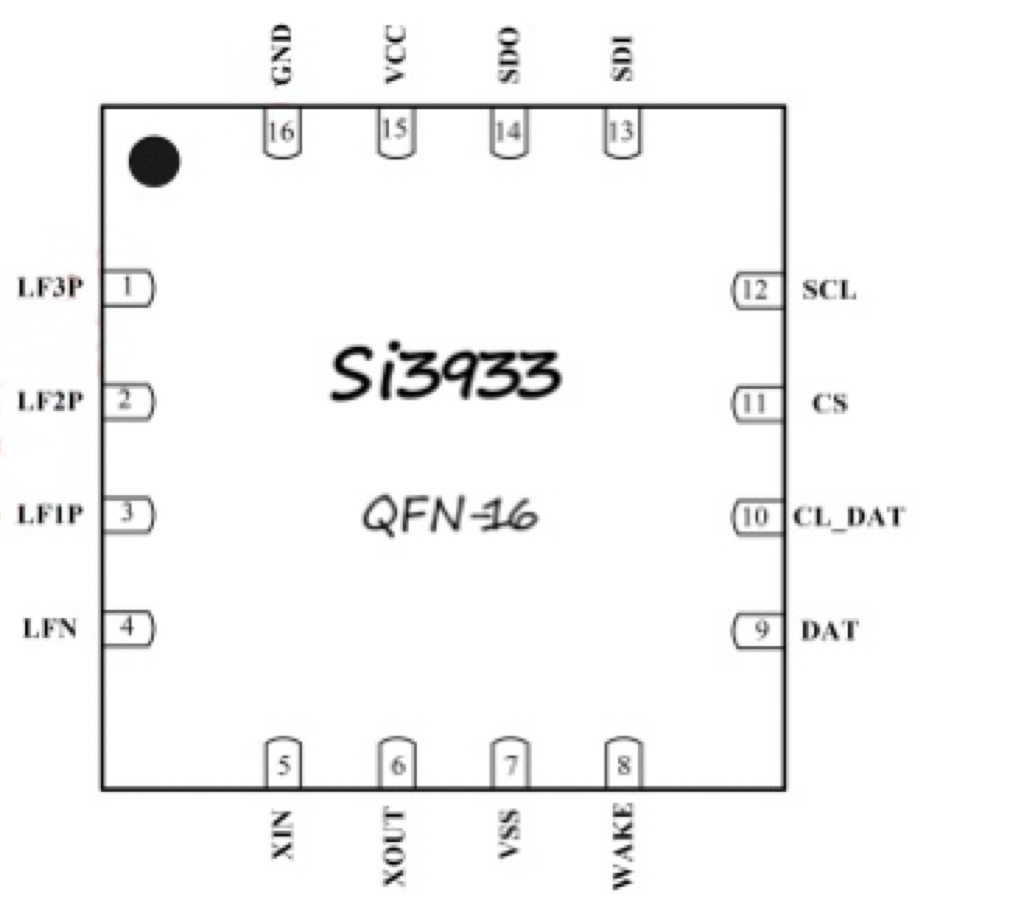

2856 SI3933 具有内部时钟产生器,可选择使用晶体振荡器或者 RC 振荡器。用户也可以选择使用外部时钟。 SI3933 支持可编程的数据速率和带时钟恢复的曼彻斯特解码。自动调谐功能确保了芯片与所需载波 频率的完美匹配,极大地简化了天线调谐。

2022-11-04 08:43:46 1315

1315

TLV360x是一个325 MHz、高速的系列具有轨对轨输入和传播的比较延迟2.5ns。快速响应和宽工作电压范围使比较器适用于窄信号脉冲检测和数据激光雷达的时钟恢复应用以及线路接收器。

2022-11-25 15:26:16 0

0 为了克服传输通道对于高速电信号的损耗,需要采用昂贵的低损耗的PCB板材(如M6/M7等板材),并且在交换芯片和光模块里都有复杂的针对电信号的预加重、均衡、时钟恢复等电路,这些都增加了系统的成本、功耗和设计难度。

2022-12-19 15:32:21 359

359 数据从远程设备(假设为DSP的SRIO端)传输过来,FPGA端(假设我们这端为FPGA的SRIO端口)通过RX接收到串行数据,先到达物理层进行时钟恢复,串并转换,之后进行8b/10b解码操作、CRC校验,这一系列的操作都在物理层完成,之后进入传输层

2023-03-03 10:19:53 725

725 以PCIE和SATA为例,时钟信息通过8b/10b编码已经集成在数据流里面,数据本身经过加扰,不可能有多于5个0或者5个1的长串(利于时钟恢复),也不存在周期性(避免频谱集中)。这样,通过数据流的沿变可以直接用PLL恢复出时钟,再用恢复的时钟采集数据流。

2023-06-06 10:20:52 910

910

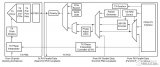

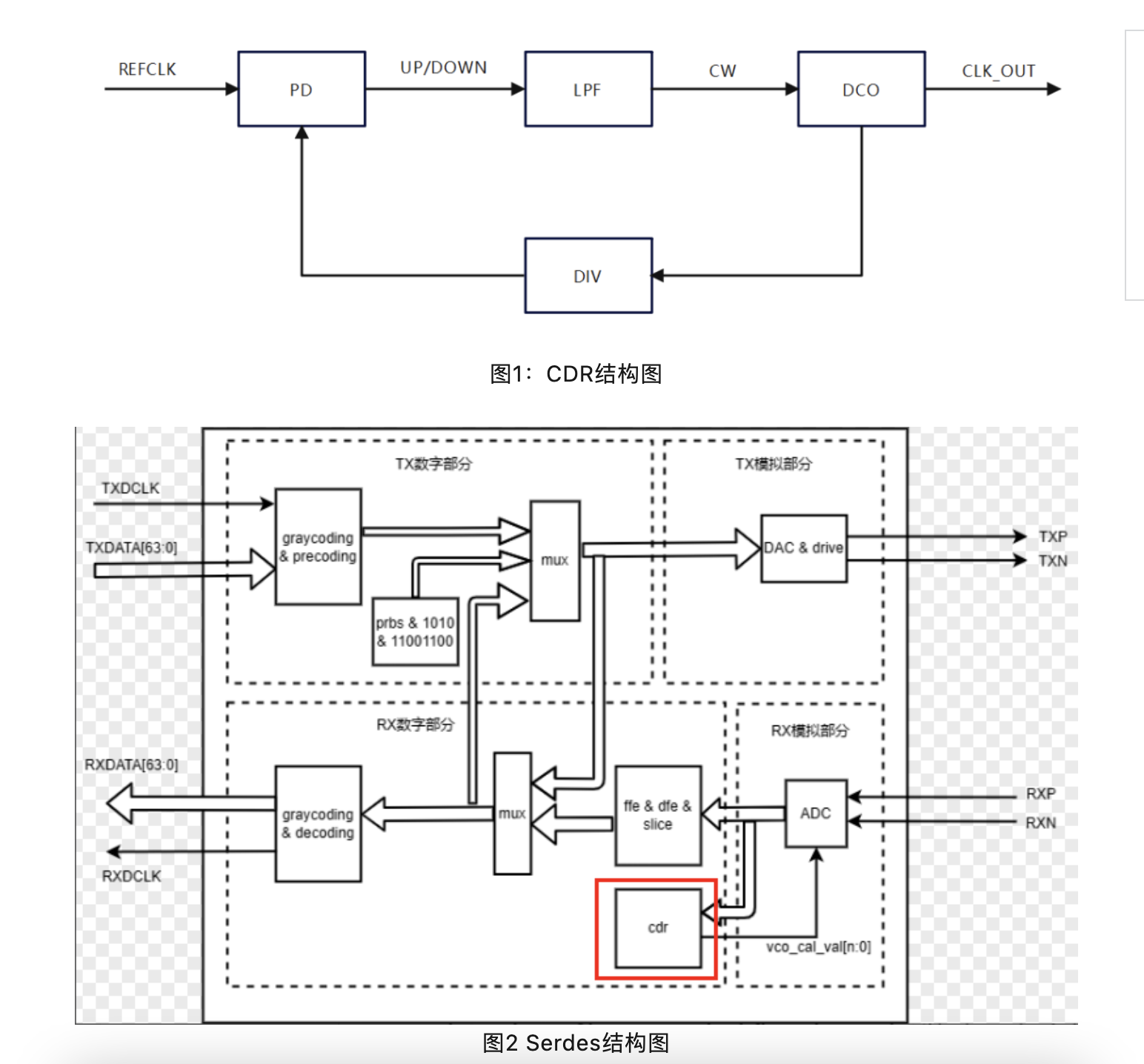

Serdes RX通过CDR的PD(数字鉴相器)来提取相位信息,然后调整DCO(数字压控振荡器)的输出相位来实现数字时钟恢复,如图1所示。

2023-09-01 15:18:35 621

621

正在加载...

电子发烧友App

电子发烧友App

评论