引言:本文介绍最常见的外部噪声源以及它们如何影响高速信号链的总动态系统性能,另外给出了一些模拟和数字小技巧,可用来改善您下一款设计的信噪比(SNR)。

简介

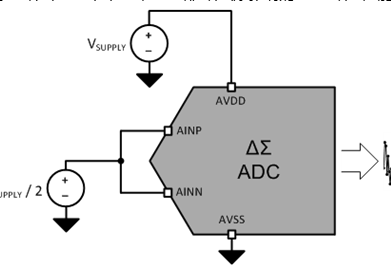

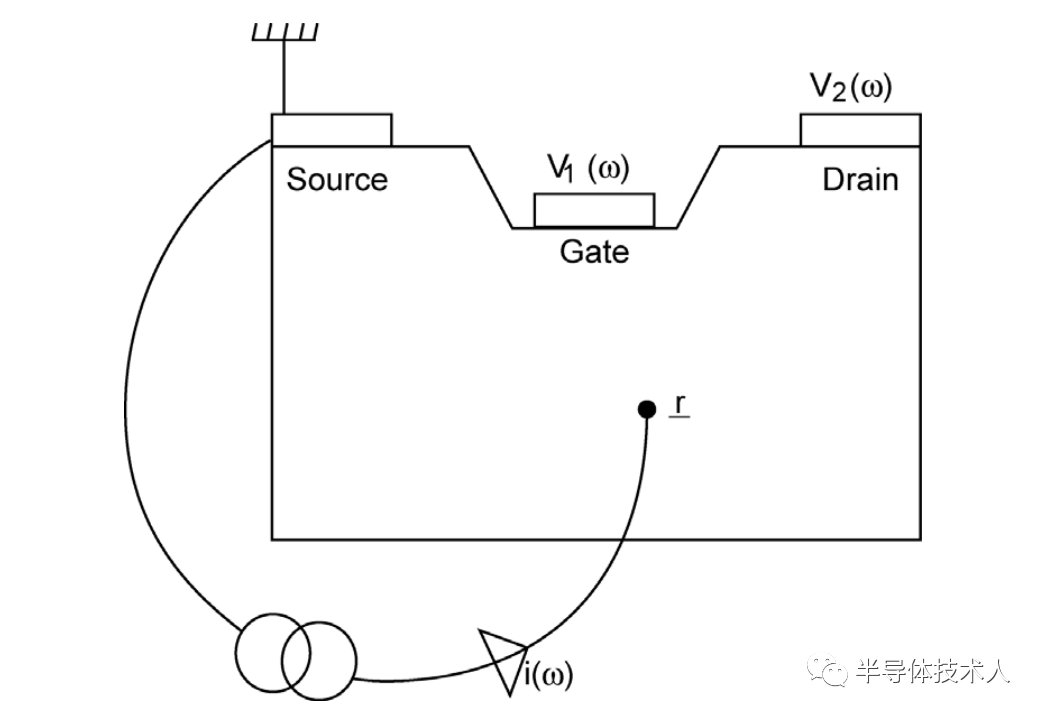

高速模拟信号链的设计可能非常具有挑战性,因为有如此多的噪声源需加以考虑。无论频率为高速(>10 MHz)或低速,转换器都应视为高速混频器,从而所有输入引脚——无论它们pin信号的类型如何(比如模拟、时钟或电源)——都能让这些pin脚的噪声引入到输出频谱。

转换器受限于工艺水平会有特定的底噪,其取决于内部节点和偏置。大部分情况下,高速ADC采用0.18 µCMOS设计,这意味着模拟电源(AVDD)为+1.8 V。这种趋势会持续扩大周边其它驱动模拟输入和时钟的支持器件极限,导致转换器产生偏压。

由于这一转换器裕量不断受限,每一款新的设计都会面临保持−150 dBFS/Hz或更低的极低噪声频谱密度的挑战。设计人员需认识到周边噪声贡献因素对整个信号链解决方案的重要性,而这就是这种认识至为重要的原因。

诚然,有很多噪声原理。本指南涉及其中的两条原理:噪声带宽和噪声源叠加。

噪声带宽

噪声带宽不同于典型的放大器或滤波器截止点的−3 dB带宽。噪声波形具有不同的形状(矩形),表示带宽的总积分。这表示考虑噪声带宽贡献因素时,您需要略为调整噪声计算。

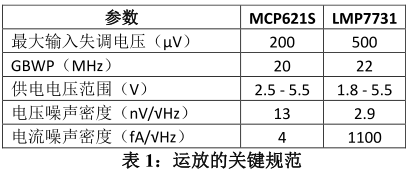

对于一阶系统而言——比如一阶低通滤波器——噪声带宽会宽57%。对于二阶系统,噪声带宽会宽22%;而三阶系统为15.5%,以此类推。在计算中纳入噪声带宽时,可快速参考表1。

噪声源

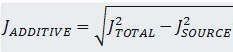

噪声源五花八门;添加噪声源时,它们互不相关,并且会分解为更小的单位,而非直接相叠加。因此,有利于突破目前受单个器件所限制的极限。因此,它所带来的优势是可以突破目前受单个器件所限制的极限。它所带来的优势——如果能够在应用中加以利用的话——就是您可以叠加驱动器/放大器或转换器(或两者)来改善系统的SNR动态范围。

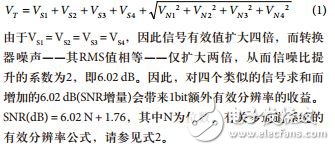

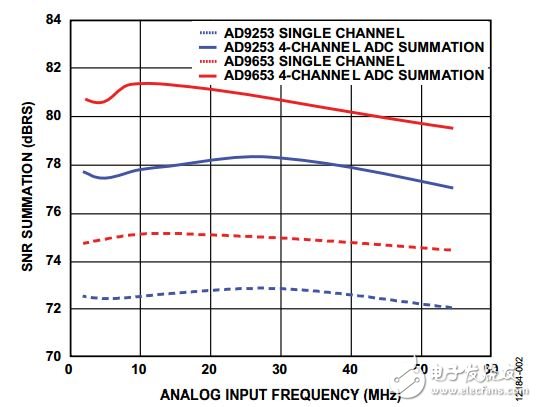

例如,对四个ADC的输出求和可改善SNR 6 dB,或1位。每一个ADC的输入由信号项(VS)和噪声项(VN)组成。对四个噪声电压源求和可产生总电压VT,数值为四个信号电压与四个信号电压与四个噪声电压的RSS的线性求和参见公式1:总噪声公式)。

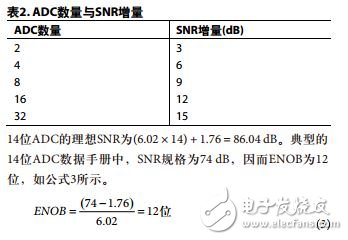

表2显示了对多个器件的输出进行求和后得到的SNR提升。从简化设计角度来说,根据面积、功耗和封装等方面考虑,对四个器件求和显然是非常合适的选择。某些关键情况下,可能会用到更多数量的器件,具体取决于其它系统规格(包括成本)以及可用的电路板面积,当然还有功耗。

图1. 四个并联ADC求和的基本框图

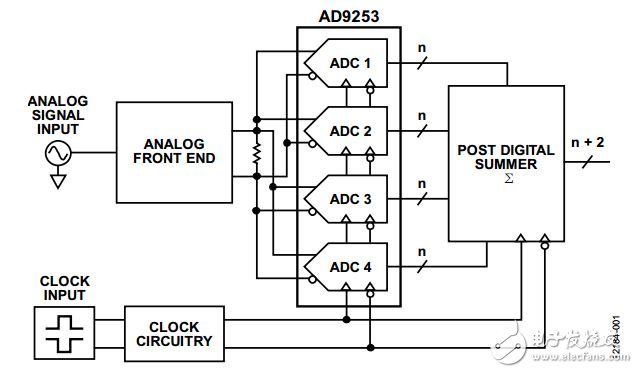

最近,较新的设计会继续降低ADC的内核功耗,从而使得四通道和八通道ADC可即刻投放市场,比如四通道、14位、125 MSPS ADC AD9253。对于多个ADC系统而言,这意味着部署更简单、节省的空间更多。因此,通过对四个14位转换器输出进行求和,设计人员便可弥补额外的一位,并将系统级ENOB扩展至13位(或80 dB)。

同样的技巧还可用于双通道和4道放大器,降低进入转换器的加性噪声。

图2. 求和SNR性能与频率的关系

噪声贡献因素

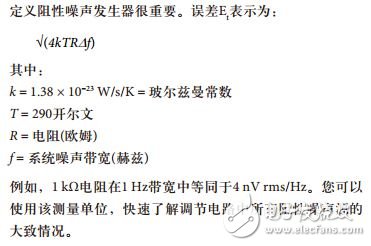

几乎所有电路元件都存在一定的固有噪声,尤其是有源器件。电阻是小噪声的源泉,会产生一定量的热噪声。它们的贡献因素较小,但如果设计人员使用高数值电阻围绕放大器来驱动转换器,则它的噪声贡献因素相比所需性能会变得非常巨大。在该电阻周围采用小增益会得到更大的噪声。

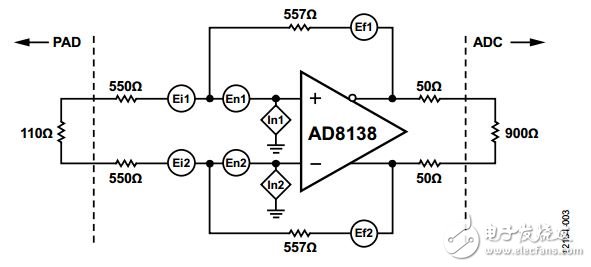

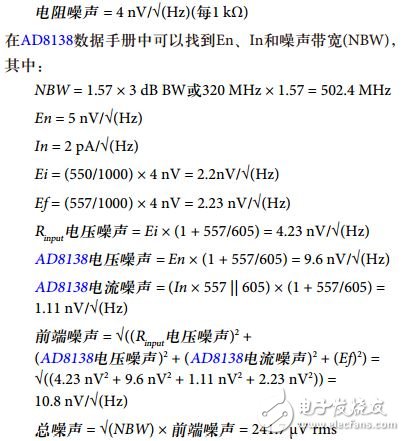

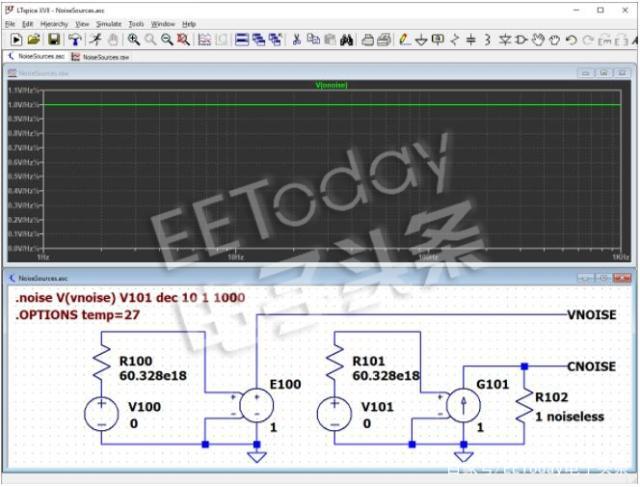

例如,图3显示的是采用AD8138放大器的放大器噪声模型。该模型显示了如何对所有电阻噪声求和并将增益纳入考虑,以便获得折合到输出的总噪声。

图3. 放大器噪声模型

注意,放大器具有某些电压噪声源(En1和En2),以及某些电流噪声源(In1和In2)。这些噪声源可在放大器数据手册的规格中找到。另外,数据手册还会定义每一个电阻噪声源。

通过简单的计算便可以定义下述公式,并得到图3中放大器电路折合到输出(RTO)的总噪声。

注意,放大器与运算放大器的区别仅仅在于前者内部含有阻性元件。因此,噪声计算包含在总噪声贡献因素中,并由数据手册定义。

在数据手册中,它一般表示为“折合到输入”(RTI)的噪声。通过选择放大器电路增益,可以快速使用RTI数值,并将其调整为:

RTI = 1.3 nV/√(Hz)

增益 = 16 dB

从而有:RTO = 1.3 × 10(16/20) = 8.2 nV/√(Hz)

出于噪声分析的目的,使用内置电阻的放大器要方便的多。

抖动

时钟噪声或抖动影响转换器性能。如果您对如何确定该噪声的系数有初步了解——比如说在宽带中确定——那么很容易对该指标所导致的性能下降有所感受。

只需使用宽带抖动噪声数秒(最好是fs级别或更短的时间)以及模拟输入频率或目标IF频率, 当时钟幅度为最大值并假定输入为正弦波,那么就会产生最大误差。可以导出一个简单的公式,以获得RMS电压误差。例如,30 MHz模拟输入IF和100 fs时钟抖动便可产生18.8 µV或2 × π 30 M × 100 fs的宽带电压噪声。

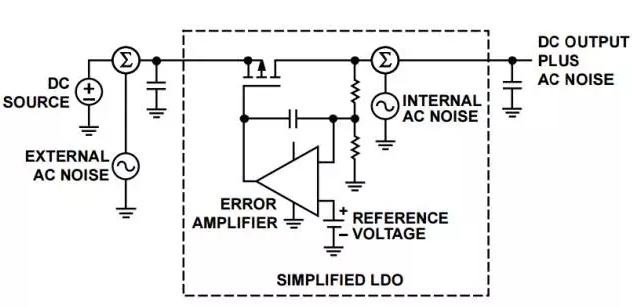

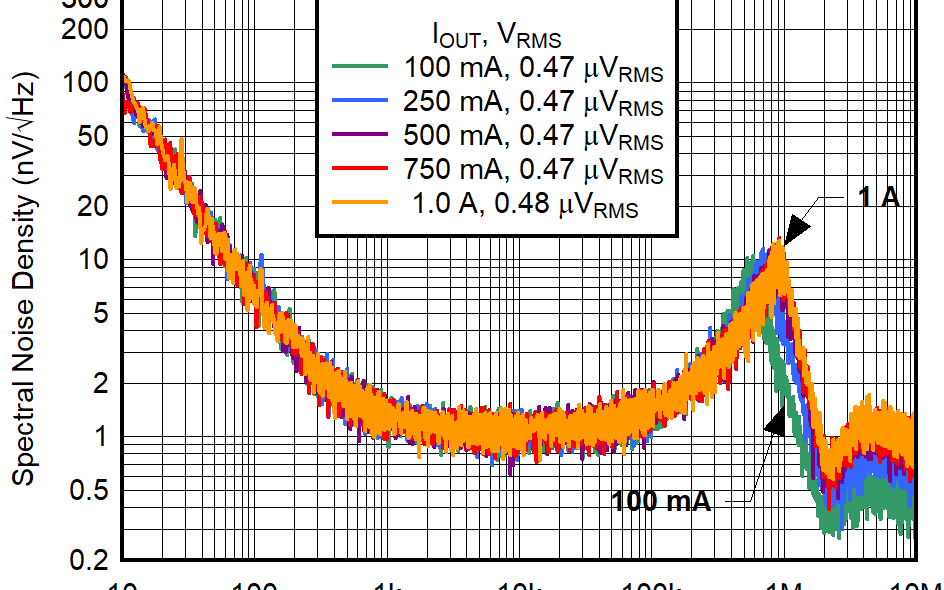

电源噪声

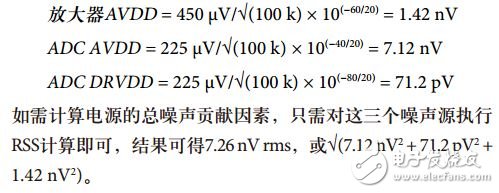

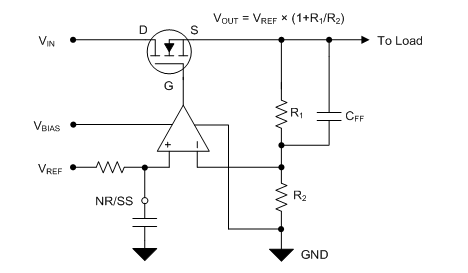

探索电源噪声需要知道LDO本身的噪声及其测量频段。这些数据同样可在调节器数据手册中找到。例如,一个调节器在100 kHz带宽内可能具有225 µV噪声。如果这是已知的,并且噪声视为白噪声,则可以用来估计它对ADC噪声性能(SNR)的贡献。然而,您需要知道ADC电源抑制(PSR)。

大部分情况下,在模拟电源域内(AVDD),第一奈奎斯特区的电源抑制为−40 dB至−60 dB。因此,为了简便起见,本例中假定为−40 dB。由此可知,有效噪声贡献为7.12 nV或225 µV/√(100 kHz) × 10(−40/20)。记住,这只是一个电源域的情况。所有电源域都需要进行同样的评估,而每一个域在ADC、放大器等器件内可能具有不同的PSR值。

在信号链设计中考虑噪声因素

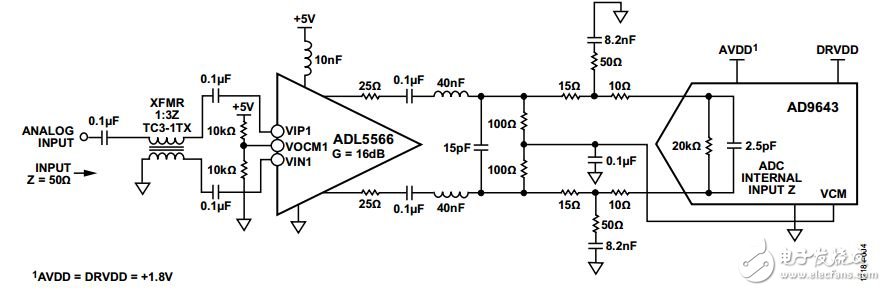

下面的示例会帮助巩固这个原则,并将进一步展示整个信号链的总动态性能。该示例采用ADL5566放大器驱动AD9643 ADC和独立电源(ADP1708和ADP1706),并分别偏置放大器和转换器,如图4所示。

图4. 示例信号链框图

由于上一节完成了很多前期工作,下一步需要计算的就是ADC热噪声。

对于AD9643,模拟输入满量程为差分1.75 V p-p,其数据手册中的SNR为71.7 dBFS。通过反向计算SNR公式,可知热噪声为:

SNR = 20 × log(满量程V rms)/热噪声 (V rms))

或者

71.7 = 20 × log((1.75/2/√(2))/热噪声 (V rms))

或者

热噪声 = 161 µV rms

下一步,确定电源的噪声贡献因素。示例计算表明ADC模拟电源的AVDD贡献因素为7.12 nV rms。

为转换器的DRVDD和放大器的AVDD电源执行同样的计算。进行这些计算时,DRVDD的PSRR为−80 dB,放大器AVDD的PSRR为−60 dB。在同一个频段内,这分别等于71.2 pV rms和1.42 nV rms噪声贡献因素

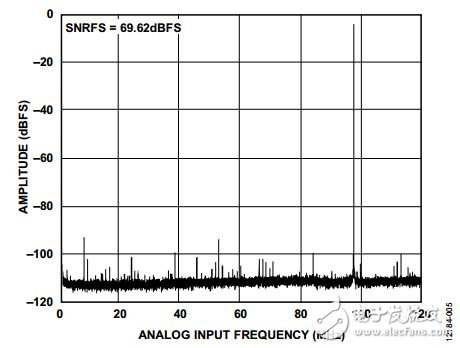

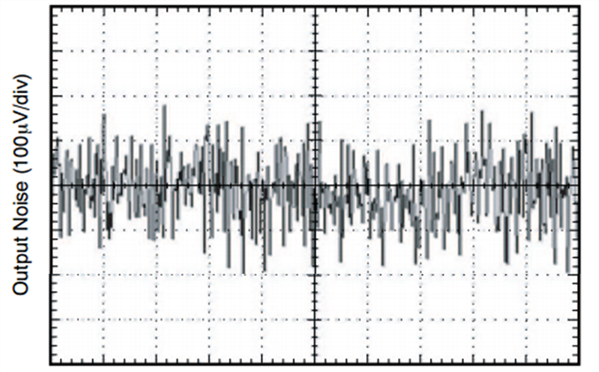

对于这个放大器示例而言,ADL5566在最大16的dB增益的条件下,RTO噪声为8.2 nV/√(Hz)。接下来,需定义带宽。通常可在放大器输出以及转换器输入之间使用一个抗混叠滤波器, 否则所有的放大器宽带噪声都会折回带内。对此噪声进行限制,假定滤波器带宽为150 MHz(−3 dB点)。使用此数值是因为AD9643是一个250 MSPS ADC,并且其奈奎斯特频段为fs/2或125 MHz。通常,为了捕捉整个目标奈奎斯特频段,会将AAF设计得略大。如图7所示,放置一个2阶或双极点LC滤波器用于抗混叠抑制。这样使得噪声带宽为:150 MHZ × 1.22 = 183 MHz。因此,计算可知,放大器的噪声贡献因素为111 µV rms,或8.2 nV/√(183 MHZ)。现在,只需采用如下标准SNR公式,对所有示例中推导出的噪声源执行RSS计算:

这样就得到了关于SNR的总信号动态范围。如果仔细查看这些贡献因素,便可轻松理解信号链的哪一部分具有最大的贡献。理解这些噪声源可以明白如何进行权衡取舍,才能让所选相关设备发挥最佳整体性能。

图5. ADL5566和AD9643测得的FFT/噪底性能

信号链设计性能

理解噪声权衡取舍以及信号链中产生噪声的根本原因可以使前期的设计变得更为简单。这篇小型指南解释了所有器件——无论有源器件或无源器件——如何在信号链中交互,以便准确预测整个信号链的SNR动态范围性能结果。进行下一款信号链设计时,应牢记这些原则。

电子发烧友App

电子发烧友App

评论