摘要:同步辐射光源硅像素探测器是面向北京先进光源对X 射线探测的重大技术需求所研发的新型仪器。该探测器处于辐射环境中,且多个前端电子学读出板被放置在密封的冷却容器中。为在不打开冷却容器的情况下,脱离专用的USB-JTAG (Universal serial bus - joint test action group)下载电缆对现场可编程门阵列(Field programmable gate array, FPGA)进行远端升级,本文提出了一种基于XVC (Xilinx visual cable)协议,通过以太网,利用ARM 微控制器控制FPGA 的JTAG 接口对其进行远程更新与调试的方法。该方案附加电路少,易于拓展,同时也提高了更新可靠性。

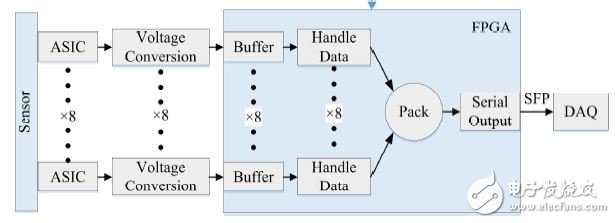

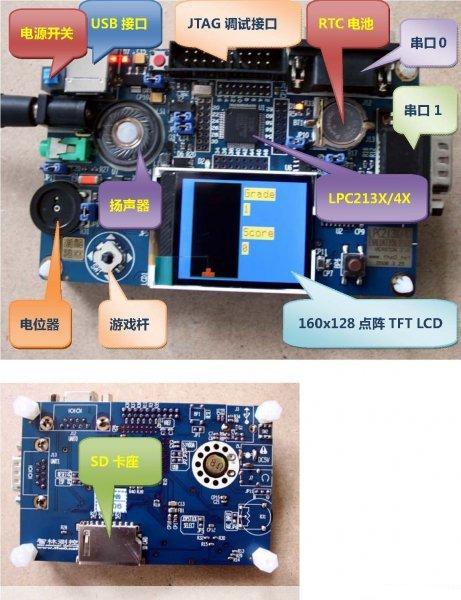

前端探测器包含6 个前端模块,每个模块对应一个传感器以及8 个读出ASIC 芯片,芯片输出信号通过电平转换送到前端数据处理现场可编程门阵列(Field programmable gate array, FPGA)。FPGA 对信号进行缓冲验证,汇总处理后通过光纤传输到后端DAQ (Data acquisition)系统。图1 为前端数据处理框图。

图1 前端数据处理框图

由于整个前端探测器模块放置在密封的冷却容器中,而且整个探测器处在辐射环境中,方便可靠的FPGA 远程更新与调试方案成为电子学系统设计的重要方面。显然传统的基于USB-JTAG (Universalserial bus - joint test action group)更新FPGA 的方式已不再适用。

目前国内外出现的FPGA 远程更新的方案基本分为两大类[2]:一类是针对早期的内部没有专用远程升级电路的FPGA 器件,采用单片机CPLD(Complex Programmable Logic Device)、DSP (Digital Signal Processor)、ARM (Acorn RISC Machine)等作为辅助配置器件[3],配合外部Flash 和以太网芯片来实现,这些方案灵活性高但设计复杂且提高了成本;另一类是针对最新推出的FPGA 器件,其自带了远程升级内核或逻辑块,只要结合外部数据配置通道,即可实现远程更新,该方案附加电路少,节省硬件资源,但却占用了FPGA 的内部逻辑资源,而且只适用特定型号的FPGA。另外,上述两类方案均无法实现对FPGA 的远程调试,还需要在PC 端开发用于远程更新的TCP/IP 软件,增加了设计复杂度。考虑到基于JTAG 的下载方式在FPGA 配置、Flash PROM 配置、软/硬件调试以及硬件测试方面的重要用途,本文设计了一种基于XVC (Xilinx visual cable)协议,通过以太网,使用单芯片ARM微控制器控制FPGA 的JTAG 接口进行远程更新调试的方案。该方案操作简单,无需额外开发TCP/IP软件,基于网络的通信能够保证足够远距离的灵活的可靠数据传输。还能对FPGA 进行远程ChipScope调试。同时,通过简单的JTAG 链路连接,可以同时完成多片FPGA 的升级与调试[4]。

1 硬件系统实现

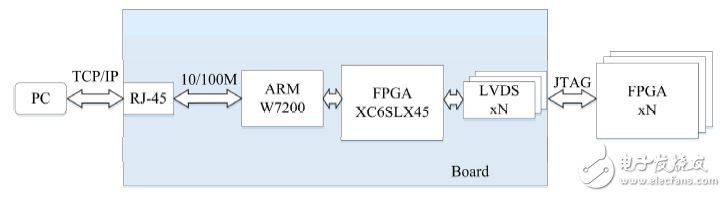

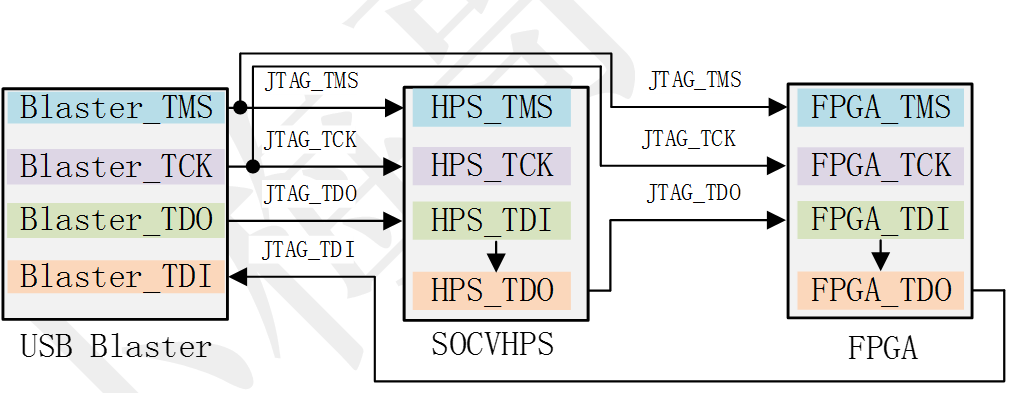

在本设计中,ARM 微控制器通过模拟JTAG 接口的时序对FPGA 进行配置。针对多片FPGA 进行远程更新的系统框图如图2。

图2 系统模块框图

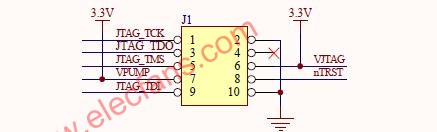

系统硬件电路主要由ARM 微控制器、JTAG 链路模块、LVDS (Low-voltage differential signaling)模块组成。ARM 选择Wiznet 公司的W7200 开发板作为配置控制器,一端通过网络与PC 建立连接,另一端通过外设的GPIO (General purpose input output)传输JTAG 配置时序。LVDS 模块负责将JTAG 单端信号转换为低压差分对信号,一对一发送给待更新的FPGA。多片待更新FPGA 的JTAG 链通过另外一块FPGA 开发板上的主控FPGA 芯片XC6SLX45的内部逻辑来实现,板上用9 个接插件引出FPGA的9 组I/O,分别连接W7200 和8 个LVDS 模块。其中, LVDS 模块和主控FPGA 开发板以子母板的形式连接。

远程更新时,PC 端使用iMPACT 将包含配置的指令通过网络发送给W7200,W7200 根据XVC 协议接收指令并模拟产生JTAG 时序,主控FPGA 接收该时序并通过JTAG 链路送入待配置FPGA,完成最终配置。

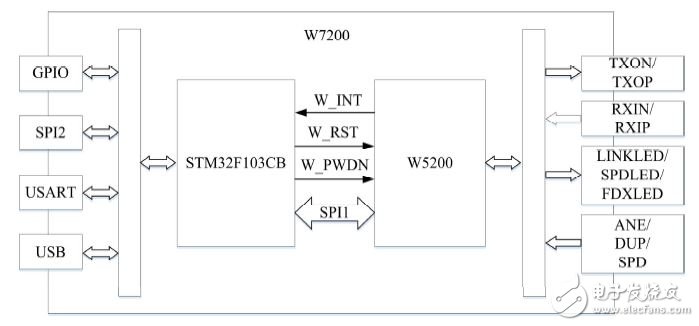

W7200 是Wiznet 公司推出的一款单芯片集成了硬件TCP/IP 协议栈的ARM Cortex-M3 微处理器[5]。内有20 KB 的SRAM 和128 KB 的Flash 以及32 KB 的以太网RX/TX 缓存,具有最高72 MHz的工作频率,有足够的能力进行数据处理。硬件TCP/IP 协议支持 TCP、UDP、IPv4、ICMP、ARP、IGMP、PPPoE 和以太网,这些协议在各种应用领域已经得到多年的验证。其结构如图3 所示。

图3 W7200 结构框图

W7200 的内核采用32 位的STM32F103CB,通过SPI 与W5200 连接,外部拓展40 个引脚,负责提供该系统的GPIO、I2C、SPI、USB 以及USART接口,集成度高却具有很低的功耗。W5200 为该公司推出的全硬件TCP/IP 芯片,负责为该系统提供各类硬件TCP/IP 协议、MAC 以及PHY,支持8 个独立的socket 同时工作。使用该芯片的优势是通过简单的socket 编程,用户便可以轻松实现所需的以太网通信,而不必要处理复杂TCP/IP 协议栈控制。

2 软件设计

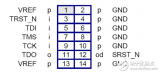

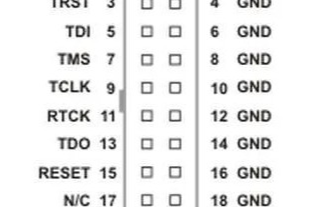

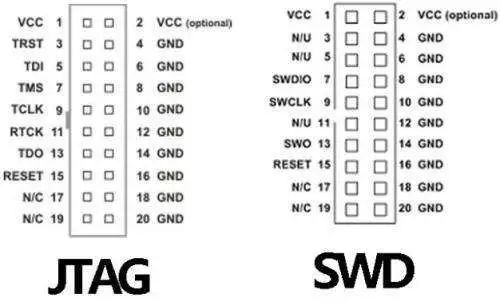

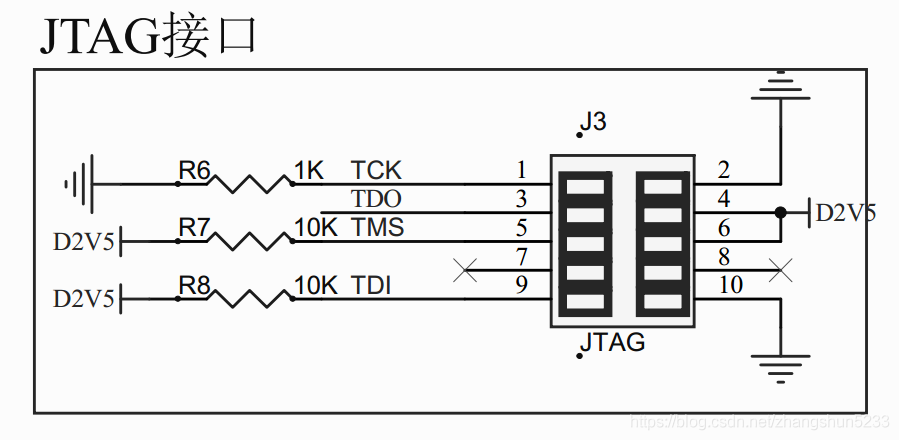

2.1 JTAG 工作方式

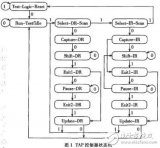

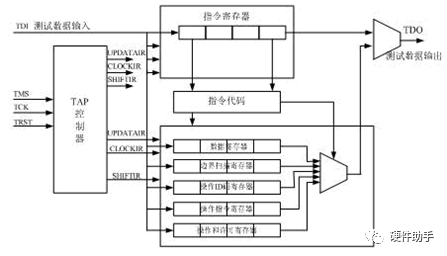

JTAG是符合IEEE 1149.1 标准的国际标准测试协议[6],主要用于各类芯片的内部测试和配置。现在大多数高级器件(包括FPGA、MCU、DSP 以及CPU 等)都支持JTAG 协议。标准的JTAG 接口是4 线接口:模式选择(TMS)、时钟(TCK)、数据输入(TDI)以及数据输出(TDO)信号线。

JTAG 工作原理是在器件内部定义一个TAP(Test Access Port)测试访问端口,外部控制器通过TAP 可以访问芯片提供的所有数据寄存器和指令寄存器。使用JTAG 方式配置FPGA 时,通过TCK 和TMS 的值,选定一个需要访问的数据/指令寄存器,将其连接到TDI 和TDO 之间。然后由TCK 驱动,通过TDI,把需要的数据/指令输入到选定的数据/指令寄存器中,同时把对应的寄存器中的值通过TDO 读出来。JTAG 接口在线编程和调试的特征改变了传统生产流程,配置效率高,是项目研发阶段必不可少的配置模式。

2.2 XVC 协议

XVC 协议是Xilinx 公司推出的一款基于TCP/IP 的虚拟线缆协议[7],它可发挥类似于 JTAG线缆的作用,允许用户无需使用USB 线缆而是通过网络访问Xilinx FPGA 的JTAG 接口并对其进行高效率的远程更新与调试。该协议还具有扩展性,可进行安全连接,允许用户通过编程将其实现于不同的平台。

XVC 协议内容简单,使用方便,其基本内容可总结为如下三条指令:

1) getinfo:

该指令用于获取XVC 服务的版本。当接收到“getinfo:”指令时,该服务将会返回如下的字符串:“ xvcServer_v1.0;

”, 其中,代表了该协议一次能移位发送的字节向量的最大长度。

2) shift:[num bits][tms vector][tdi vector]

该指令表示分别以字节向量TMS vector 和TDI vector 的形式发送num_bits 个二进制数据。其中,num_bits 是一个小端格式的整数,TMS vector和 TDI vector 代表所要发送的TMS 和TDI 的二进制数据。发送过程中,0 字节的0 比特位首先被发送出去,字节向量的长度会根据num_bits 的值向上补齐成最接近的字节数。该指令最终应该返回与TMS vector 向量同样长度的字节向量TDO vector,代表从JTAG 接口返回的所有的TDO。同样也是0字节的0 比特位首先被接收回来。

3) settck:[period in ns]

该指令表示将该协议通信的时钟周期设置为period 纳秒。period 同样是一个小端格式的整数值。使用该指令最终应该返回实际的周期值。

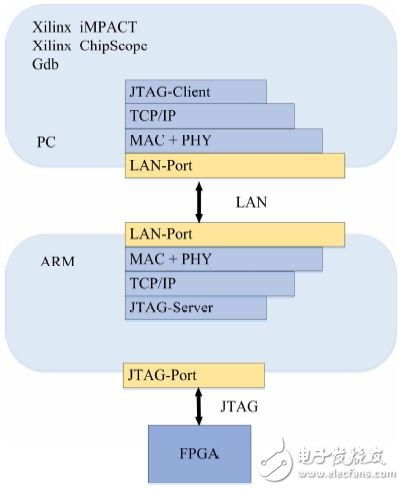

iMPACT 和ChipScope 通过网络访问FPGA 的JTAG 接口的基本原理就是基于XVC 协议发送shift指令,实现JTAG-Client 的功能[8]。因此只要ARM微控制器根据shift 指令格式分析数据,便能成功模拟JTAG 时序,实现类似于JTAG-Server 的功能。JTAG-Server 与JTAG-Client 的结构如图4。

图4 JTAG 服务器与客户端

2.3 FPGA 软件设计

在本设计中,主控FPGA 负责实现8 片待更新FPGA 的JTAG 链路。一组I/O 口用于接收W7200的配置时序,另外8 组I/O 口分别连接8 个LVDS模块的输入。一个4 位的拨码开关用来控制接入JTAG 链的FPGA 的个数。

2.4 ARM 软件设计

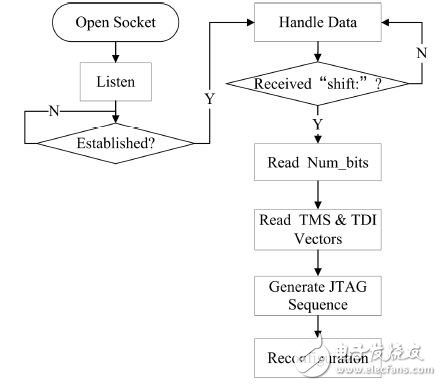

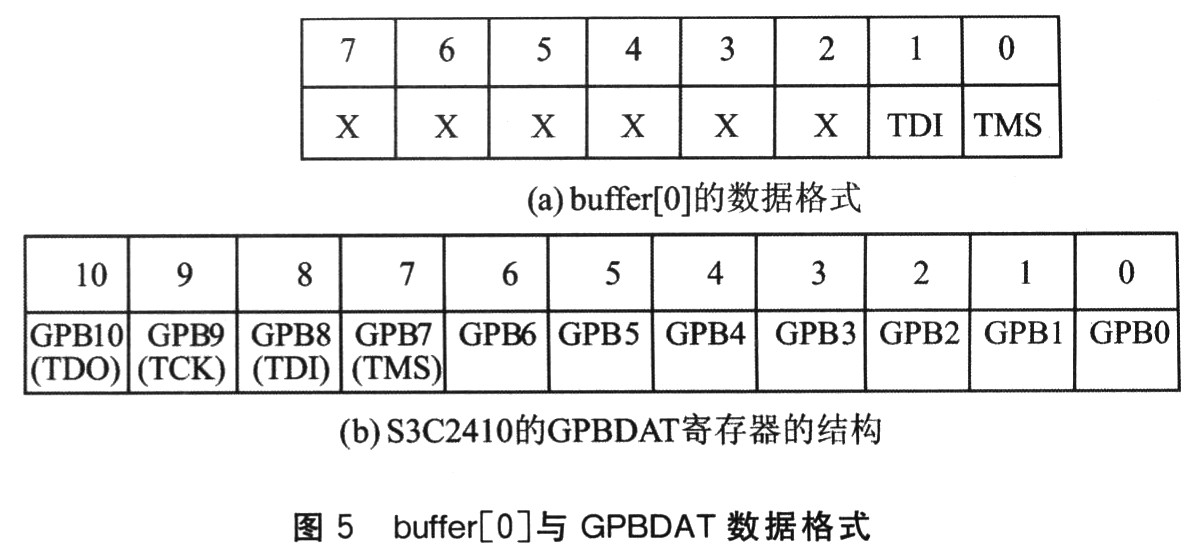

本方案使用基于JTAG 的配置方式,W7200 作为配置控制器,其通用I/O 引脚PB12、PB13、PB14、PB15 分别作为JTAG 接口的TMS、TCK、TDO 和TDI。W7200 的工作流程如图5 所示。其应用程序用C 语言开发生成,Keil MDK 进行编译调试。主要包括W7200 初始化和指令处理两部分。

首先,W720 初始化的内容包括:设置系统工作时钟、中断、GPIO/SPI、接收与发送缓存大小以及网络设置。由于iMPACT 软件每次发送shift 指令的最大长度为2 256 byte,故设置接收缓存区RX_BUF 大小为2 256,而发送缓存区TX_BUF 大小为1178。网络设置包括选择打开socket0 进行网络通信,并设置其通信协议为TCP,端口号为5000,并为其分配IP 地址和MAC 地址。初始化完成后,W7200 会作为TCP server 打开socket0 监听网络上的连接请求。

图5 更新流程

W7200 处理指令的过程为:从 socket0 的接收数据缓冲区接收6 个字节,若与字符串shift:对比相同,则继续读取4 字节的内容作为num_bits,通过计算将其转换为字节数nr_bytes。接着按该字节数分别读取TMS vector 和 TDI vector 到接收缓存区RX_BUF,然后通过for 循环分别将TMS vector 和TDI vector 的每一位赋值给TMS 和TDI 引脚,同时产生周期性的TCK 信号。该for 循环同时将TDO引脚上检测到的输入信号写入发送缓冲区TX_BUF,循环结束后以TDO vector 发送给PC。PC 验证收到的TDO 数据无误,继续通过shift 指令发送下一个数据包。由此便实现了一个完整的JTAG数据链路,从而实现了通过网络将配置数据经由JTAG 接口配置给FPGA 的过程。

3 远程更新

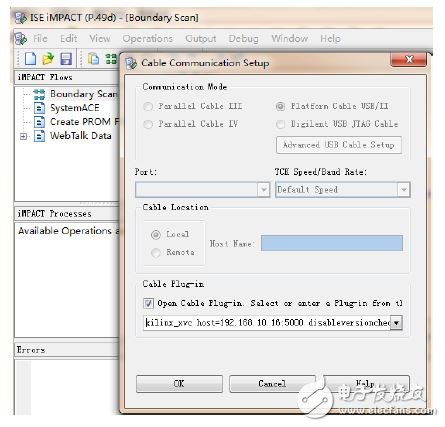

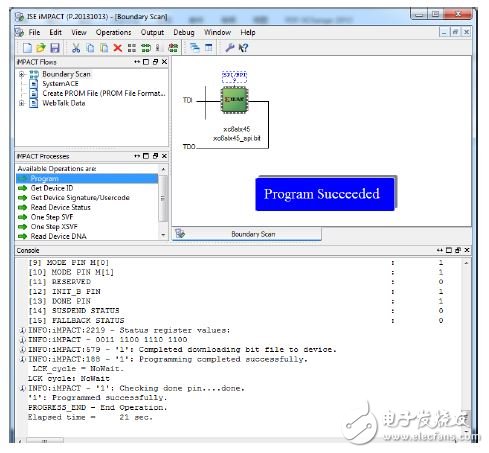

利用iMPACT 进行远程更新时的软件设置如图6 所示。首先打开iMPACT 软件,在边界扫描模式下选择菜单栏的output、Cable Setup,选择打开Xilinx_XVC 插件,更改连接对象的IP 地址与端口号,发送连接请求给W7200。

待成功建立socket 连接后,初始化JTAG 链,选择待配置FPGA 和配置文件并双击Program,PC端便按照shift 指令的格式发送配置指令和数据给W7200。配置结果如图7 所示。经过验证,为一片FPGA 成功配置大小为630 KB 的.bit 文件所需时间为21 s,配置1.41MB 的.bit 文件所需时间为48 s,配置速率均为240 KB·s−1。在相同环境下,配置不同大小的文件速率基本一致。该方案使电子学系统的远程更新和调试变得简单灵活。

图6 iMPACT 下载线设置

图7 成功更新FPGA

4 结语

本方案中,基于Xilinx 的XVC 协议,利用PC机与ARM 通过以太网通信,成功实现了基于JTAG接口的FPGA 的远程更新与调试。该方案实际只需要一个ARM 单芯片,无需其它额外的附加电路。在其他系统中应用时,可直接将W7200 芯片固化在电路板上,方便可靠。随着互联网的发展推进,通过网络进行硬件程序的更新将变得更加普遍。

电子发烧友App

电子发烧友App

评论