美国赛灵思(Xilinx)2012年4月5日使用28nm工艺制造的FPGA “Virtex-7 X690T”演示了有线通信系统(背板)。该FPGA配备有80个以最大13.1Gbit/秒的速度工作的高速串行收发器“GTH”,已于2012年

2012-04-09 11:13:59 2848

2848 xilinx的7系列FPGA根据不同的器件类型,集成了GTP、GTX、GTH以及GTZ四种串行高速收发器,四种收发器主要区别是支持的线速率不同,图一可以说明在7系列里面器件类型和支持的收发器类型以及

2020-11-20 12:08:15 17712

17712

FPGA GTP收发器设计指导疑问描述测试表明,Spartan-6 FPGA的GTP收发器有可能受到临近bank中用户管脚的干扰。因此,赛灵思针对bank0和bank2中管脚的使用提出了一些新的建议

2016-08-25 09:46:38

针对bank0和bank2中管脚的使用提出了一些新的建议。本文中的使用建议目的在于尽量减小用户管脚对GTP收发器的影响。在所有情况下,利用Spartan - 6 FPGA的SSO准则仍然需要遵循

2017-03-21 14:34:27

FPGA高速收发器设计原则高速FPGA设计收发器选择需要考虑的因素

2021-04-09 06:53:02

高速收发器(SERDES)的运用范围十分广泛,包括通讯、计算机、工业和储存,以及必须在芯片与芯片/模块之间、或在背板/电缆上传输大量数据的系统。但普通高速收发器的并行总线设计已无法满足现在的要求。将收发器整合在FPGA中,成为解决这一问题的选择办法。FPGA高速收发器设计时,我们需要注意哪些事项呢?

2019-08-07 06:26:42

技术开发的广阔前景。Xilinx公司在推出的Virtex-5 FPGA以及配套的Virtex-5 RocketIOTM GTP收发中开始支持多种协议,如SATA2.0传输协议。SATA(Serial

2018-12-11 11:04:22

RocketIO收发器怎么实现高速通信?

2021-05-26 06:28:57

RocketIO高速串行接口本人在北京工作6年以上,从事FPGA外围接口设计,熟练使用Virtex-5/Virtex-6 FPGA,非常熟悉RocketIO GTP/GTX协议,Aurora协议

2014-03-01 18:46:35

、体积小、无中继、传输距离长等优点得到了广泛的应用,光纤收发器正是利用了光纤这一高速传播介质很好的解决了以太网在传输方面的问题。那么,我们对这个名词也来做个解释吧。光纤收发器,是一种将短距离的双绞线

2014-04-30 17:28:08

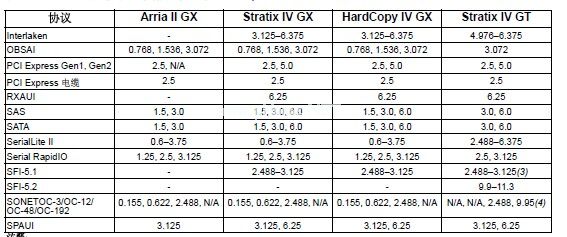

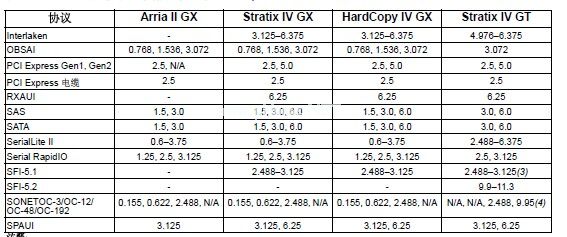

在低成本的 FPGA 中,Cyclone® IV GX 器件内嵌多达八个全双工收发器,运行在 600Mbps 到 3.125 Gbps 的串行数据速率上。 表 1-1 列出了 Cyclone IV GX 收发器通道所支持的串行协议信息。

2017-11-14 10:54:41

嗨,我正在使用ARTIX 7 FGG676,Transciever的示例参考设计 - GTP - 如UG769中所述。我为SATA2.0配置了两个这样的收发器,将它们连接在一起并成功地在它们之间来回

2020-07-31 10:20:29

嗨,可以告诉我MGT,GTP,GTX收发器之间的区别吗?Rocketio属于MGT还是GTP组?

2020-03-10 08:51:53

Express Master DMA Read --> DDR2/DDR3内存 --> 光纤/RocketIO GTP接口.3. 寄存器访问:软件访问FPGA内部与DMA传输相关的寄存器.4.

2012-05-21 09:32:15

海 任何人都可以解释Virtex 5(ML 506)中的GTP及其规格以及MGT和GTP收发器之间的区别。

2019-08-14 10:01:43

`描述PMP9408 参考设计提供为 Xilinx 的 Virtex® Ultrascale™ FPGA 中的千兆位收发器 (MGT) 供电时所需的所有电源轨。它利用一个 PMBus 接口来实现电流

2015-05-11 10:30:22

设计GTXGTH收发器电源设计1.概述Xilinx 7系列FPGA GTX/GTH收发器是模拟电路,当设计和实现PCB设计需要特殊考虑和注意。这其中涉及器件管脚功能、传输线阻抗和布线、供电设计滤波、器件选择、PCB布线和层叠设计相关内容。2.管脚描述和设计指导2.1 GTX/GTH收发器管脚描述

2021-11-11 07:42:37

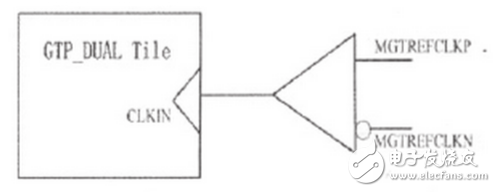

我正在使用spartan6 gtp收发器向导。但没有外部时钟。相反,我使用时钟向导使用200 M振荡器生成所需的速率。我尝试使用chipcope测试示例设计,但错误计数信号正在增加gradullay。谁能帮帮我吗?

2019-08-06 10:47:32

我之前在CSDN上查到的资料都显示FPGA需要连接一个独立CAN控制器,如SJA1000再去连CAN收发器。请问我能直接把FPGA的引脚直接连在CAN收发器的TX、RX上吗?如果不能原因又是什么?

2018-10-10 09:25:39

一、概述

IBERT(集成误码率测试仪)是xilinx为7系列FPGA GTX收发器设计的,用于评估和监控GTX收发器。IBERT包括在FPGA逻辑中实现的模式生成器和检查器,以及对端口的访问

2023-06-21 11:23:12

你好,关于GTP / GTX收发器的JTAG实现,我有几个问题。1. JTAG是否针对GTP / GTX收发器实现(因此可以驱动和读取引脚以进行电路板验证)2. JTAG组件放在GTP磁贴中的哪个

2020-06-18 14:41:02

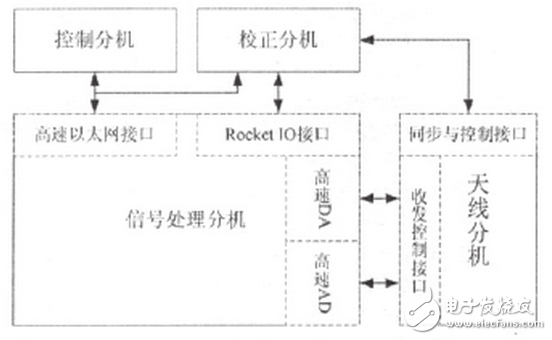

)经过CPRI接口传输。3 FPGA实现CPRI协议传输方案3.1 基本方案用FPGA实现CPRI协议传输具有以下2种方案。(1) 方案一RocketIO收发器的FPGA来实现CPRI协议的光纤通信

2019-06-04 05:00:18

)经过CPRI接口传输。3FPGA实现CPRI协议传输方案3.1基本方案用FPGA实现CPRI协议传输具有以下2种方案。(1) 方案一RocketIO收发器的FPGA来实现CPRI协议的光纤通信[3

2019-05-31 05:00:06

精准的数据收发信息,更好的为工程项目服务。传统的并行传输方式由于走线多、信号间串扰大等缺陷,无法突破自身的速度瓶颈。而串行传输拥有更高的传输速率但只需要少量的信号线,降低了板开发成本和复杂度,满足高频率远距离的数据通信需求,被广泛应用到各种高速数据通信系统设计中。

2019-10-21 06:29:57

高速差分IO信号的基础知识: 1、初步认识GTX 当你接触到FPGA的高速串行通信时,比如GTX收发器,一条TX发送线,一条RX接收线,这时候你肯定会联想到UART串口,UART串口通信多么简单

2018-08-16 09:59:19

高速LVDS数据传输方案和协议基于FPGA的高速LVDS数据传输本人在北京工作6年,从事FPGA外围接口设计,非常熟悉高速LVDS数据传输,8B/10B编码等,设计调试了多个FPGA与FPGA以及

2014-03-01 18:47:47

每对电源和地引脚都要良好旁路。5 结论本文给出了基于FPGA高速数据采集系统中的输入输出接口的实现,介绍了高速传输系统中RocketIO设计以及LVDS接口、LVPECL接口电路结构及连接方式,并在

2018-12-18 10:22:18

串行通信要求的传输线少,可靠性高,传输距离远,被广泛应用于计算机和外设的数据交换。通常都由通用异步收发器(UART)来实现串口通信的功能。在实际应用中,往往只需要UART的几个主要功能,专用的接口

2011-09-09 09:10:09

的关键技术是嵌入式RocketIO GTP低功耗串行收发器。最大的Virtex-5LXTFPGA中最高可包含24个串行收发器,每个串行收发器的运行速率范围均为100Mbps至3.2Gbps。结合可编程

2019-04-12 07:00:11

FPGA的关键技术是嵌入式RocketIO GTP低功耗串行收发器。最大的Virtex-5LXTFPGA中最高可包含24个串行收发器,每个串行收发器的运行速率范围均为100Mbps至3.2Gbps。结合

2019-04-16 07:00:07

,支持PCI Express Gen2(5Gbps/lane); •支持64bit DDR3-1600,容量1GByte; •该FPGA内嵌16个高速串行收发器RocketIO GTX; •4个

2014-11-24 15:31:02

,pin_to_pin兼容FPGAXC7K410T-2FFG900,支持8-Lane PCIe、64bit DDR3、四路SFP+连接器、四路SATA接口、内嵌16个高速串行收发器RocketIO GTX,软件

2015-01-28 15:48:55

如果系统精度、效率和可靠性至关重要,那么设计传感器节点无线数据传输以用于远程监控就会是一个相当大的挑战。而溶液的pH值是许多行业需要考虑的一种测量,今天我们分享的参考设计的目的是评估pH玻璃探针的特性,从而解决硬件和软件设计的不同挑战,并提出一种利用射频收发器模块从探针无线传输数据的解决方案。

2019-07-19 07:34:37

我使用了Virtex 5系列芯片XC5VSX95T。我使用了GTP模块,实现了快速IO通信,3.125Gbps。然后,出现了问题.FPGA可以通过Rapid IO与FPGA进行通信,通信速率高达

2020-06-19 08:53:14

嗨,我正在尝试使用spartan 3E FPGA(成本因素)实现千兆以太网接口。由于斯巴达系列中没有RocketIO收发器,因此我们必须使用LVDS TBI接口。有没有人有实施这个经验?你能给我一些

2019-08-07 09:38:25

ASIC系统。 使用USB协议栈知识产权(IP)及外部收发器 在第一种方法中,我们可以在FPGA或ASIC中实现SIE(见图3)。图3 FPGA + USB协议栈IP + USB收发器 SIE IP

2012-11-22 16:11:20

嗨,有没有办法在V5的GTP收发器中进行串行环回模式?手册提供了4种环回模式,但它们都涉及解串器之后的路径,我需要通过接收器循环串行数据并在CDR之后将其路由到发送器,而不通过重新锁定的并行路径。这可能吗?谢谢,戴夫

2020-05-27 17:17:02

嗨,大家好,我正在尝试在我的vhdl设计中实现GTP收发器。该设计应该用作两个定制硬件板之间的连接测试。它使用线性反馈移位寄存器来生成比特流,该比特流被打包到数据帧中。在通过链路发送帧之前,发送对齐

2019-07-24 14:10:28

Virtex-5LXT FPGA的关键技术是嵌入式RocketIO GTP低功耗串行收发器。最大的Virtex-5LXTFPGA中最高可包含24个串行收发器,每个串行收发器的运行速率范围均为

2019-05-05 09:29:30

本文在对Virtex-5 RocketIOTM GTP进行了解的基础上,针对串行高速接口开发中位宽不匹配的问题,提出了一种位宽转换方法,以解决Virtex-5 RocketI0TM GTP无法直接应用于某些串行高速接口开发的问题,并就SATA2.0接口开发中该问题的解决方案进行详细阐述。

2021-05-28 06:21:43

本文给出了基于FPGA高速数据采集系统中的输入输出接口的实现,介绍了高速传输系统中RocketIO设计以及LVDS接口、LVPECL接口电路结构及连接方式,并在我们设计的高速数传系统中得到应用。

2021-04-29 06:04:42

本文介绍了基于Xilinx Virtex-6 FPGA的高速串行数据传输系统的设计与实现,系统包含AXI DMA和GTX串行收发器,系统增加了流量控制机制来保证高速数据传输的可靠性。最后进行了仿真测试,测试结果显示系统可以高速可靠地传输数据。

2021-05-25 06:45:36

怎么实现基于MRF24J40的IEEE802154无线收发器电路方案设计?

2021-05-25 07:00:15

实现4字节的Aurora通信吗?第二个问题......我怎样才能找到哪个GTP或GTX收发器连接到SFP,哪个不连接。我在计划中迷失了方向。谢谢。问候,的Ondrej

2019-09-06 10:39:10

是否可以在不使用GTP / GTX收发器的情况下从Virtex-5中的数据信号中恢复时钟?该数据使用差分信令并具有NRZ编码(例如,8b / 10b)。不幸的是,输入引脚没有连接到高速收发器,所以

2020-06-08 14:50:56

亲爱的所有人,1。是否有人有关于使用Virtex 5 Rocket GTP收发器为SATA创建物理层的信息?2.并且我不了解火箭GTP中的元素RX终止和均衡,它决定了输入的高速差分信号的值。如果有

2018-09-30 11:06:24

求助FPGA高速串行收发器,输出12.5Gbps的信号要用什么电平输出28.5Gbps的信号要用什么电平?

2014-11-10 09:12:51

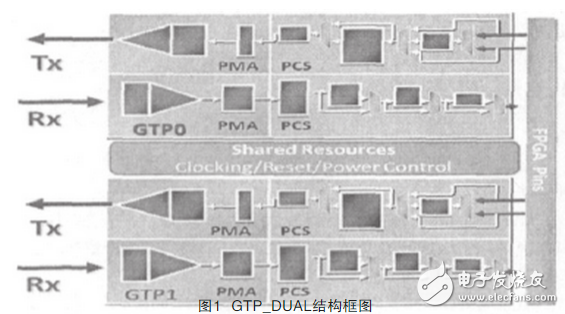

UG196的第83页注1,Virtex-5 FPGA RocketIO GTP收发器用户指南,2.1版,“采购GTP_DUAL磁贴上方的GTP_DUAL磁贴数量不得超过3个”。如果我有LX110

2020-06-04 11:49:37

描述PMP9463 参考设计提供为 Xilinx Ultrascale™ Kintex® FPGA 中的千兆位收发器 (MGT) 供电时所需的所有电源轨。它利用一个 PMBus 接口来实现电流和电压

2018-08-10 09:36:45

什么是解复用电路?解复用电路在高速收发器中的应用是什么?

2021-05-19 06:24:03

亲爱的先生我试图在Artix-7中使用GTP传输串行数据。遗憾的是,由于串行数据流包含一些抖动,Artix-7 GTP接收器中有时会出现数据错误。另一方面,收发器参考时钟是干净的。我想我应该提高

2020-08-24 09:44:56

从FPGA1中的GTP传输到FPGA2中的GTP。每个FPGA都有自己的本地收发器参考振荡器。我有两个目标,我想要实现:频率匹配FPGA1和FPGA2上的TXOUTCLK,和即使在重新编程FPGA之后

2020-08-28 06:22:25

收发器。无论如何,我的问题如下:我可以使用这些SMA连接器(连接到rocketIO引脚),而无需使用FPGA的内部传输器吗?要恢复,我想使用那些SMA连接器,但不使用ROAKEIO收发器,因为我有一个外置的?谢谢您的回复。再见

2019-09-04 11:26:58

作为第二个Spartan 6上的收发器来响应回送数据。截至目前,我可以传输Master 2 GTP收发器。 Slave GTP适当地响应并发回数据。在GTP_DUAL块中的某处,看起来好像已启用通道

2019-08-02 06:59:30

Virtex-5 RocketI0TM GTP是Xilinx公司根据高速串行接口开发市场对高性能GTP的特殊要求而开发的一款具有通用性、易用性、低功耗和低成本特性的GTP收发器。文章针对Virtex-5 RocketIOTM GTP收发

2010-07-22 17:08:27 30

30 利用RocketIO高速串行传输模块将数字图像和控制指令串行化,实现对高帧频、多通道数字图像的高速远程传输和反馈控制。利用Virtex2II Pro系列FPGA设计的光纤数字图像传输模块,可将

2010-09-22 08:34:12 36

36 摘 要:介绍了FPGA最新一代器件Virtex25上的高速串行收发器RocketIO。基于ML505开发平台构建了一个高速串行数据传输系统,重点说明了该系统采用RocketIO实现1. 25Gbp s高速串行传输的设

2010-09-22 08:41:18 43

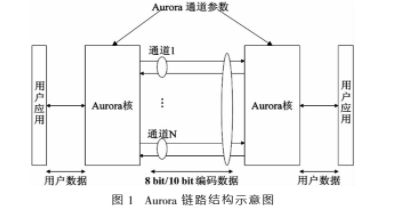

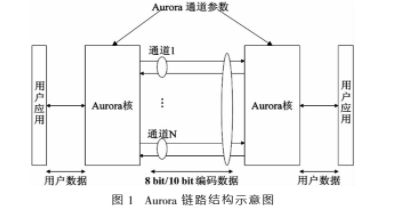

43 摘要: 串行传输技术具有更高的传输速率和更低的设计成本, 已成为业界首选, 被广泛应用于高速通信领域。提出了一种新的高速串行传输接口的设计方案, 改进了Aurora 协议数据帧

2010-09-22 08:42:29 31

31 采用Xilinx 公司Virtex- II Pro 系列FPGA 内嵌得SERDES 模块———RocketIO 作为高速串行协议的物理层, 利用其8B/10B的编解码和串化、解串功能, 实现了两板间基于数据帧的简单高速串行传输

2010-09-22 08:44:28 28

28 FPGA高速收发器设计原则

高速收发器(SERDES)的运用范围十分广泛, 包括通讯、计算机、工业和储存,以及必须在芯片与

2009-04-07 22:26:14 986

986 收发器的传输速率

不同的收发器产品由于转换接口的不同,传输速率也不同,典型接口传输速率如下:

2010-01-08 14:16:26 4038

4038 采用带有收发器的全系列40-nm FPGA和ASIC实现创新设计

人们对宽带服务的带宽要求越来越高,促使芯片供应商使用更多的高速串行收发器。因此,下一代应用采

2010-02-04 11:06:19 879

879

本文基于Virtex-5 FPGA的GTP单元给出了一种在高级电信计算架构(ATCA)机箱内实现单对差分线进行3.125Gbps串行传输的设计方案。

2011-09-16 09:52:19 1733

1733

GTP transceiver是FPGA里一种线速度达500Mb/sà6.6Gb/s的收发器,利用FPGA内部可编程资源可对其进行灵活地配置,使其适合不同的需要如以太网、SATA1.0接口

2018-07-14 06:45:00 17860

17860

了解如何在您的 UltraScale™ FPGA 设计中部署串行收发器。了解并利用串行收发器模块的特性,如 8B/10B 和 64B/66B 编码、通道绑定、时钟校正和逗点检测。其它专题

2017-02-09 08:04:41 327

327 赛灵思(Xilinx)公司FPGA器件的高速串行收发器类别如下

2017-02-11 11:11:30 5958

5958

线的过多会增加卫星重量,增加卫星发射成本。日前市面上的主流工业级FPGA芯片都集成各自开发的高速串行收发器,能达到很高的数据传输速率,但是卫星上使用的宇航级FPGA芯片中,却少有集成高速串行收发器,在国防军事卫星上使用国

2017-11-14 11:48:33 6

6 的数据传输,适用于多种高速数据传输协议。依据实际工程应用需求,提出了基于RocketIO的高速串行数据传输系统解决方案,实现了每通道2.5 Gb/s的传输速度。最后介绍了RocketIO在Aurora和PCI Express协议实现中的应用,并总结了高速通信系统的共性特征。

2017-11-24 20:37:49 1787

1787

经理。我从事FPGA工作已经有12年了。他们中后5人的主要工作是高速串行收发器应用。

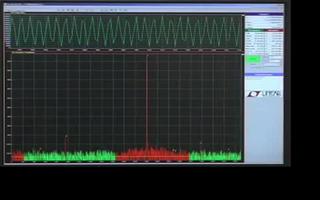

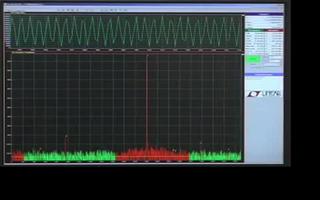

我们今天在这里演示新的Linear Technology LTC2274模数转换器怎样与具有嵌入式串行收发器

2018-06-20 05:28:00 4215

4215

展示7系列GTZ(高达28.05Gb / s)高速串行收发器的性能;

与Luxtera公司的不重定时光模块进行四路26G对接,实现100G应用。

2018-11-23 06:20:00 3057

3057 通过Virtex-7 2000T FPGA中的GTX收发器实现高速串行性能。

2018-11-22 06:27:00 3461

3461 本文档介绍如何在Spartan®6 FPGA中使用GTP收发器。•spartan-6 FPGA GTP收发器简称为GTP收发器。

•gtpa1_dual是实例化原语的名称,它实例化一组

2019-02-15 14:42:47 27

27 7系列FPGA GTP收发器的可定制Logicore™IP Chipscope™Pro集成误码率测试(IBert)内核用于评估和监控GTP收发器。该核心包括在FPGA逻辑中实现的模式生成器和校验

2019-02-20 14:30:00 25

25 UART(Universal Asynchronous Receiver Transmitter通用异步收发器)是一种应用广泛的短距离串行传输接口。常常用于短距离、低速、低成本的通讯中。

2019-08-12 17:46:18 722

722

FPGA 针对需要超高速串行连接的应用进行了优化,Virtex®-6HXT FPGA通过结合6.6 Gbps GTX收发器和11.18 Gbps GTH收发器,提供了业界最高的串行带宽,以实现下一代分组和传输,交换结构。 ,视频切换和成像设备。Virtex-6 FPGA系列

2021-04-14 11:53:31 4122

4122

介绍了基于模块化方法在FPGA上实现高速通信的设计方案。系统在Aurora协议下采用高速串行收发器Rocket I/O,解决了不同

2021-05-05 14:35:00 8915

8915

Virtex-5 RocketIOTM GTP收发器的串行高速系统接口开发过程中位宽转换的几个技术问题提出了解决方案,并以SATA2.0开发为例,通过Xilinx Virtex-5 XC5VLX50T FPGA验证方案进行了可行性验证。

2021-06-24 16:10:42 2510

2510

xilinx的7系列FPGA根据不同的器件类型,集成了GTP、GTX、GTH、GTZ四种串行高速收发器,可以支持多种协议如PCI Express,SATA,JESD204B等。

2022-03-01 17:17:20 3769

3769

此篇文章深入浅出介绍了关于高速串行收发器的几个重要概念和注意事项,为方便知识点复习总结和后续查阅特此转载。

2022-03-14 17:19:38 2541

2541 电子发烧友网站提供《Logos系列FPGA高速串行收发器(HSST)用户指南.pdf》资料免费下载

2022-09-26 10:25:17 22

22

正在加载...

电子发烧友App

电子发烧友App

评论