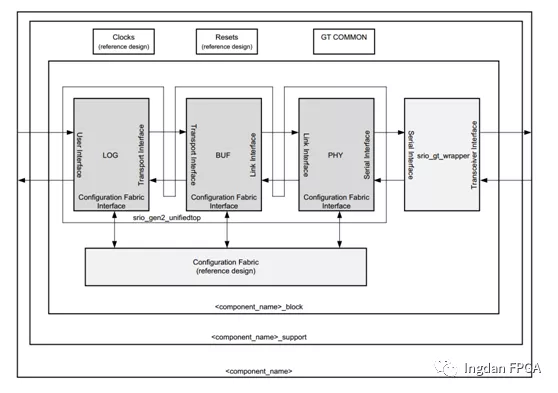

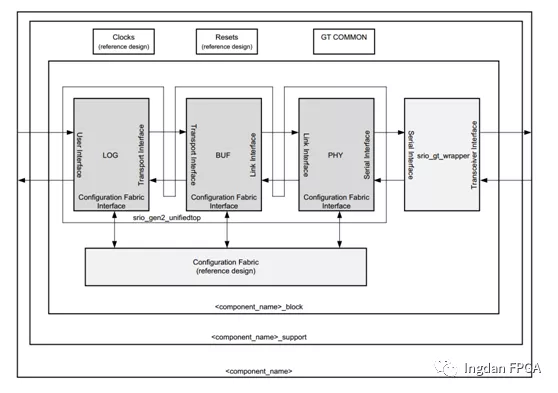

本文介绍一个FPGA常用模块:SRIO(Serial RapidIO)。SRIO协议是一种高速串行通信协议,在我参与的项目中主要是用于FPGA和DSP之间的高速通信。有关SRIO协议的详细介绍网上有很多,本文主要简单介绍一下SRIO IP核的使用和本工程的源代码结构。

2023-12-12 09:19:08 856

856

Keystone_SRIO_Init(&srio_cfg);之后,接收即终止了,之后也没办法继续接收FPGA传输的数据。而此时DSP可以正常向FPGA传输数据。

不知道是不是因为没有添加

2018-06-21 13:16:48

数据,这个时候观测交换芯片对应的端口的寄存器,发现端口状态出错,其值为0x84120306。

请问

1.是否可以这么理解,交换芯片和FPGA重新load程序之后,DSP的SRIO仍然处于已初始化的状态

2018-06-21 13:50:07

我已经研究过K1_STK中的SRIO例程,对SRIO的工作方式也很熟悉。现在将DSP板与FPGA板两板通过SRIO 4x进行背板连接,因为FPGA有专门的工具可以通过发送PRBS

2018-06-21 06:25:29

6678通过SRIO与FPGA通信,FPGA发起,向DSP的内存写数据,DSP再将数据写回FPGA。问题1:DSP如何得知何时发送完毕?是否必须通过中断(门铃中断或者GPIO中断)问题2:DSP

2019-01-09 10:58:04

各位专家好!请问:我现在想通过6678的SRIO接收来自FPGA的数据,DSP作为从属。用的是论坛给的KI_STK_V1.1的SRIO例程,在test between 2 DSPs的程序段里修改

2019-01-11 07:33:39

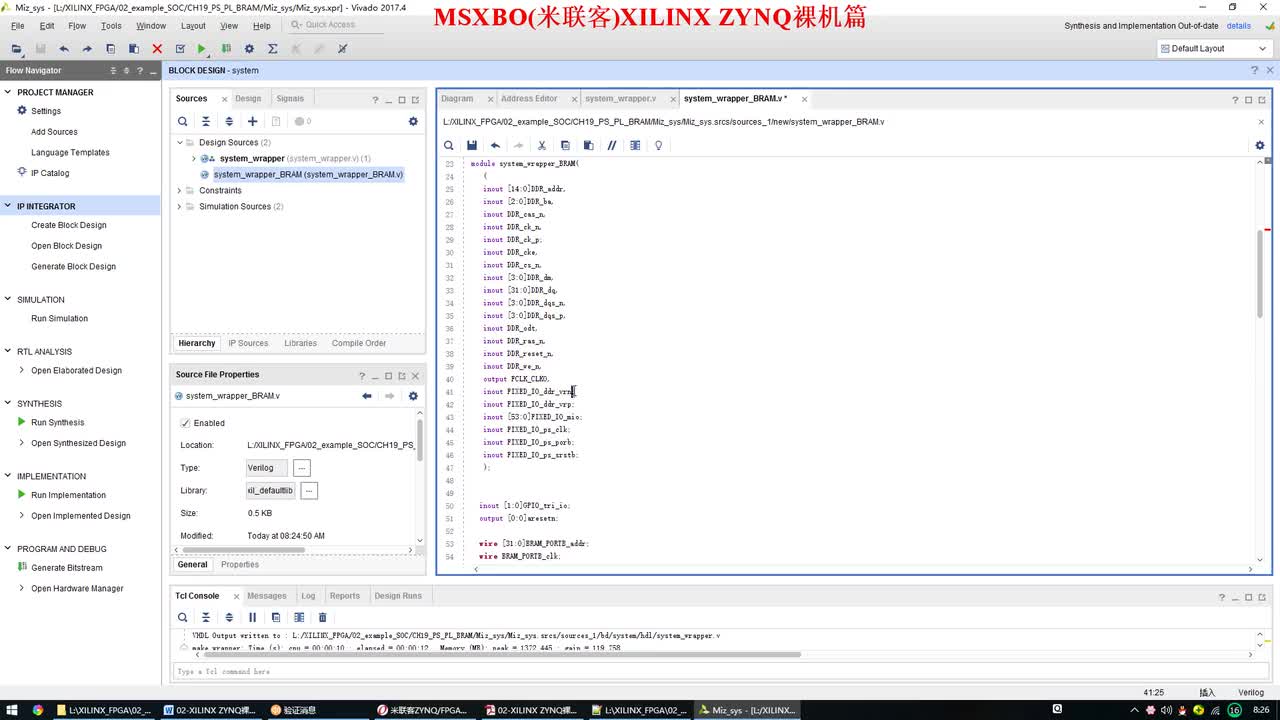

MicroBlaze挂载的外设。可以选择通过软件寄存器来控制用户IP。点击Next可以选择寄存器位宽和个数。其中IPIC是user_logic 与PLC总线之间数据交互的一系列信号。点击NEXT完成配置。(2)设计编写

2018-01-09 14:53:42

\device_srio.cport mode(port模式)SRIO通道有自回环(loopback)模式和普通模式(Normal),要使用SRIO实现FPGA和DSP的通信,必须将各port调至Normal模式,即

2020-09-23 11:08:36

\device_srio.cport mode(port模式)SRIO通道有自回环(loopback)模式和普通模式(Normal),要使用SRIO实现FPGA和DSP的通信,必须将各port调至Normal模式,即

2020-09-08 10:36:41

FPGA与6678调试SRIO通信过程中,如DSP修改后重新编译LOAD后,FPGA方无反应,需要断电再上电才能通信正常,请问可能是什么原因,根据论坛例程改编的DSP程序。。。

2018-08-07 07:28:46

CCS5.5DSP 6657FPGA XC7Z030FPGA 与 FPGA 之间SRIO传输成功;DSP 与 DSP 之间SRIO传输成功;问题 : FPGA 与 DSP 之间 ,PORT OK 可以通过,可是就是无法正确传输成功。 这会是什么问题呢?会是什么原因导致的呢?需要注意什么地方呢?

2019-01-10 11:17:28

IP CORE SRIO 2.1 ENDPOINT ECP3

2023-03-30 12:02:57

SITE LICENSE SRIO 2.1 ECP3

2023-03-30 12:03:00

各位好!

参考Ti给的例程,发现SRIO中断是直接配置寄存器,然后再SRIO_vector.asm文件中完成中断服务函数入口的映射,而主机PC和DSP的交互是通过利用CSL库函数来完成中断配置,我想问一下:两种中断配置方式能同时写在同一个函数里面吗?

谢谢!

2018-06-21 08:43:37

本人使用virtex 5 与dsp c6678 srio通信,fpga是从模式,一直使用的1x。现在调试4x的时候遇到问题,4x会自动变成1x通信,或者:dsp成4x,fpga也训练成4x,但是此时

2018-06-21 00:10:20

我用fpga nwrite方式向6678写数然后看ddr3内存 点内存界面的持续刷新时 内存数据不变 点刷新时内存数据变化 有的时候只有srio初始化的时候内存数据变一下 请问问题可能出在哪

2018-08-03 06:51:53

嗨, 我想通过srio协议将数据从我的模块(fpga)发送到其他模块(tc6678texas处理器)。我想知道是否有任何中断来启动转移?感谢致敬M LOKESWARA REDDYBEL

2020-04-30 09:31:47

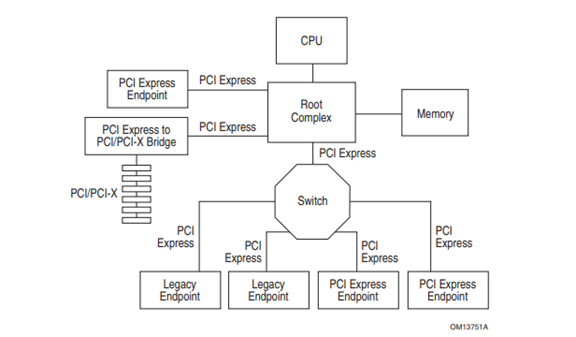

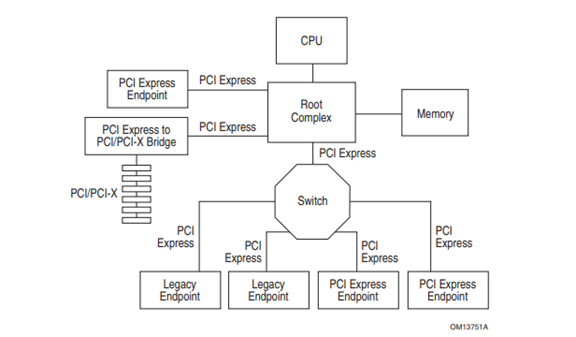

数据、万兆以太网数据、SRIO协议等数据的采集。采-存-传系统——存储高带宽大容量的存储能力是本系统的灵魂我们的系统采用高性能NVME SSD为存储介质,NVME SSD硬盘通过PCIe Gen3x4

2021-12-16 11:33:22

各位好,我正准备投板FPGA+DSP(c6657+kintex7)的一块板子,两者是通过SRIO口做数据的交互。目前,整个板子剩下SRIO口的电路还不是很确定,虽然在论坛也看过一些帖子,但

2018-06-19 01:47:15

请教SRIO通信问题,6672和FPGA的SRIO通信,2个lane连接,现象如下:

(1)两端都配置成2x,3.125G,FPGA显示port initial成功,link initial失败。

(2)把6672配置成2个1x,FPGA显示初始化成功,但无法进行数据通信。

请教是什么问题,谢谢。

2018-06-21 13:52:27

我在做EVMC6678L_EVM与FPGA用SRIO通信,首先我要做SRIO外部回环测试验证我的DSP能够向FPGA发包,硬件上,我做了一个互联底板,安装AMC插座和SMA插件,用连接线实现SRIO

2018-12-26 14:14:40

写数据进行比对,以检测SRIO传输是否有数据错误。1.1.3例程使用特别提示:例程使用,请参考下面章节顺序执行。确保ZYNQ PL程序要先运行,然后才能运行DSP程序。1.1.3.1 加载运行ZYNQ程序

2023-02-21 14:51:50

进行比对,以检测SRIO传输是否有数据错误。1.1.3 例程使用特别提示:例程使用,请参考下面章节顺序执行。确保ZYNQ PL程序要先运行,然后才能运行DSP程序。1.1.3.1 加载运行ZYNQ程序

2023-02-02 21:43:20

目前已调试完成两片DSP之间的SRIO通信,在进行DSP与FPGA之间的SRIO。现在遇到了如下几个问题。希望TI的工程师们有时间的时候给点帮助,不胜感激。1.DSP之间传输时一切正常,但是

2018-12-27 11:16:03

目前在调试多片6678与fpga通过cps1848交换芯片通信,使用的是论坛中keystone_srio例程调试过程中有几个问题。1.dap向dpga发数时而成功时而失败,失败时查看error

2019-06-04 11:03:34

你好!我现在尝试实现FPGA通过SRIO接口向DSP TMS320C6670发送数据,代码基于CCS5.0下的SRIO_Loopbacktestproject,但发现在sriodevice_init

2018-08-06 06:38:43

6678、FPGA,程序基于STK例程修改。流程:FPGA通过srio传输数据后,将传输完成标志置1。该传输完成标志位于DSP的SL2中。DSP查询该标志的状态。如果为1,则去读取数据。读取数据后

2018-08-03 09:20:22

进行修改,实现了c6678与FPGA之间的数据通信(数据通信功能已测试完成)。现在的问题是,原代码中可以正常接收到doorbell中断(即FPGA向C6778发送doorbell,在c6678一侧会成

2018-08-03 06:19:00

你好,

我想将FPGA上的数据 , 位宽 32bit, 速率500MHz 左右 实时传到 DSP上去,应该如何设计接口,不使用RAPID IO/SRIO 等接口。

2018-06-21 07:51:58

本帖最后由 一只耳朵怪 于 2018-6-25 14:20 编辑

大家好,我现在利用SRIO接口从FPGA向6678的共享内存发送数据,数据分段存储。例如将共享内存(共4M)分8段,轮询向这8

2018-06-25 01:31:27

基于ZigBee网与以太网间数据传输系统该怎样去设计?

2021-05-19 06:20:59

在现代各类仪器的开发中,人机交互功能正起着无可替代的作用。人机交互界面友好的仪器将更容易操作和使用,从而提高工作效率。液晶显示器(LCD)具有功耗低、价格低、寿命长、接口控制方便等特点,在科研

2019-10-21 07:48:41

如题,怎么将保存的的txt文件中的时间数据读出啊,用表格显示的话,时间数据总是显示0啊,怎么回事啊

2013-07-23 11:05:40

在现代各类仪器的开发中,人机交互功能正起着无可替代的作用。人机交互界面友好的仪器将更容易操作和使用,从而提高工作效率。液晶显示器(LCD)具有功耗低、价格低、寿命长、接口控制方便等特点,在科研

2019-08-22 07:50:27

我用quartus跑了cortexm3,但是不知道怎么和fpga进行数据交互,有偿求个大佬解答,解答就行,不需要代做,有的麻烦加一下我qq1661044013

2019-05-12 21:32:01

大家好,我想请教一个问题,我需要把一段离散的时间数据转换成连续的时间数据,如图左边,第1秒到第10秒的数据都是100,第10秒到第20秒的数据都是200,第20秒到第30秒的数据都是300,想转换成

2020-04-09 09:16:49

大家好,5396的手册网上只要简版的2页说明,想问下把5396的数据接口直接连到FPGA的GTX,能进行5396与FPGA的数据交互吗,还是需要相关的配置来完成5396余FPGA的交互呢?还有把数据

2018-01-07 23:02:05

本文介绍一种基于FPGA高精度时间数字转换电路的设计方法,利用片内锁相环(PLL)和环形移位寄存器,采用不高的系统时钟便可得到很高的时间分辨率,且占用较少逻辑资源。可作为功能电路独立使用,也可作为 IP核方便地移植到其他片上系统(SOC)中。

2021-05-07 06:10:43

我有一块TMS320C6670 的开发板,现在想和FPGA通信,想通过SRIO接口通信,求一个例程熟悉下?谢谢

2018-06-21 18:50:51

程序如图,但是运行后显示两列时间数据 ,如何才能只显示一列时间数据

2019-03-27 13:19:32

我在做fpga与dsp的SRIO通信,我用的是论坛上提供的SRIO test程序,目前dsp端能够实现端口0的外部回环测试。fpga端的协议还没做通,我想用dsp直接给fpga发包,fpga根据收到

2018-06-21 10:45:13

通过全局地址搬移,如从0x10800000搬移到0x13800000,那么请问如果是多核交互的话,是否其他核就是从MSMC,共享DDR,或者0x13800000对应的本地内存空间去取数据就可以了,还是

2019-01-02 15:23:29

现在用6678的SRIO从FPGA接收数据,FPGA做主!现在遇到一个问题,就是怎么判断FPGA发送过来的数据已经到达DSP指定的空间,比如我想把数据发送到6678的SL2,待数据完全到达我才能对数据

2019-01-03 11:36:07

本帖最后由 一只耳朵怪 于 2018-6-19 15:39 编辑

因为项目需求,一片C6670需要连接到两片FPGA,但是又觉得没必要使用SRIO SWITCH。所以我的问题是:C6670

2018-06-19 00:53:24

本帖最后由 一只耳朵怪 于 2018-6-19 14:49 编辑

本人使用的是6678芯片,现在需要编写6678核间数据交互部分的程序。看了资料,qmss,CPPI都可以用来进行核间数据

2018-06-19 02:42:49

你好我对DSP和SRIO之间的通信感兴趣。有人知道virtex-6 FPGA是否有srio引脚,以及如何配置?

2020-06-14 14:22:51

收不到数据,serdes loopback收到数据正确。采用的是6678平台,目前external loopback 硬件连接是:通过外部用线连RX,TX。SRIO external loopback

2018-06-19 06:26:42

怎样去设计数据采集与交互系统的软件部分?怎样去设计数据采集与交互系统的硬件部分?

2021-05-24 06:55:36

在论坛下载到SRIO的官方例程,移植到开发板后,使DSP与FPGA通讯,DSP向FPGA发送1K数据成功,更改传输数据的大小为1024*1024后编译成功,但是还是传输的1K数据,查看地址以及配置

2018-07-23 10:49:17

Hi,Ti guys,我在使用自己板上的c6678,利用论坛上keystone_srio程序调试dsp和fpga端的通信。同事从fpga(v6,srio核)看来收发地址都是34卫的,但我调DSP互联

2018-12-28 11:08:14

收发接口来说,驱动初始化完毕之后,是不是FPGA可以通过一个接口向DSP发送数据,而DSP也可以通过另一个反向接口发送数据,就是说对于一对SRIO接口来说,两边是不是都能通过这个接口主动发起数据读写操作啊?谢谢!

2018-06-19 03:02:21

本帖最后由 一只耳朵怪 于 2018-5-25 15:56 编辑

我们设计的系统是6678和Altera的FPGA利用SRIO进行通讯,FPGA利用SRIO 1X接口,对6678进行SRIO

2018-05-25 10:16:06

摘要:阐述了基于,’-- 的海量空间数据在线分发系统原理和关键技术,给出了海量影像空间数据在线浏览发布的实例。关键词:海量空间数据;影像数据发布;无缝影像数据库

2009-01-09 11:58:48 22

22 分析空间数据的特点和用常规方法进行空间数据聚类分析的难点与不足,提出一种基于改进的演化算法空间数据聚类方法——SDCEA。解决用传统方法进行空间数据聚类分析时存在的问

2009-04-10 09:29:24 28

28 利用数据库技术来管理海量的空间数据,有两种方法:一种是在数据库和用户应用系统间建立中间层,称为空间数据引擎SDE,利用SDE作为中间接口使数据库操作系统能存储和管理空

2009-08-07 09:56:31 9

9 本文在介绍空间数据挖掘、Agent 技术的概念和特点的基础上,提出一个基于Agent的分布式空间数据挖掘系统,描述了其实现过程。由于在实现过程中只传送执行挖掘功能的移动Agent

2009-12-25 13:38:56 14

14 什么是空间数据转换格式

空间数据转换格式是实施空间数据转换的标准中介格式。为实现转换,需要制订并遵循统一 的空间数据转换标准,包括现实世

2009-06-17 07:35:45 1549

1549 什么是空间数据库无缝连接

空间数据库的无缝连接是一个建立在用户与空间数据库接口基础上的概念,它是空间数据库 中空间数据集

2009-06-17 07:36:28 1145

1145 什么是空间数据交换中心

空间数据交换中心是指对不同范围、领域的空间信息及其元数据进行有效管理、给信息需求 者提供空间数据

2009-06-17 07:40:05 875

875 :根据现行文献中反复提到的空间数据处理内涵的理解,将空间数据处理分为空间数据处理技术和空间数据处理理论,简要论述了各自的主要内容,讨论了空间数据挖掘的现状和今后研究的重

2011-06-24 11:12:43 0

0 本文介绍了这种基于SRIO互联技术的高速实时数据处理硬件平台,并在该平台上研究了多DSP之间、DSP与FPGA之间的SRIO通信技术。

2012-01-10 15:07:55 3562

3562

基于FPGA的高精度时间数字转换 方法研究

2015-10-30 10:59:13 4

4 一种基于FPGA的时钟相移时间数字转换器_王巍

2017-01-07 22:23:13 2

2 基于Linux及Qt_Embedded的压铸车间数据采集系统设计_鲁遥遥

2017-02-07 18:11:35 0

0 空间数据系统咨询委员会(CCSDS)-直致力于空间任务安全性方面的工作,并成立了一个工作小组,旨在数据链路层为遥控遥测通信制定安全协议,即空间数据链路安全(SDLS)协议。该协议为已存在的空间数据

2017-11-07 15:29:37 19

19 难度大,实现复杂算法也比较困难。因此,结合多核DSP和FPGA的优势,构建基于异构处理器的信号处理系统成为当前一种发展趋势。异构处理器间的高速通信成为高速信号处理系统[1]的关键问题之一,本文基于SRIO协议设计和实现了DSP与FPGA之间的高速数据通信。

2017-11-17 03:11:01 28802

28802

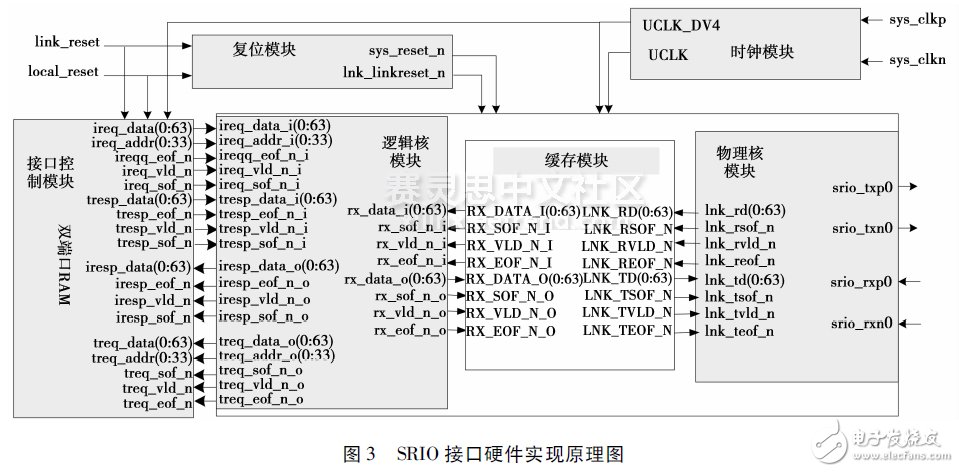

为了满足2ynq-7000系列芯片的SRIO数据传输要求,提出了一种基于FPGA控制DMA传输进行SRIO通信的设计方案,并完成了ARM与FPGA核间高吞吐率的数据交互操作。系统的FPGA部分主要

2017-12-21 11:37:03 30

30 随着信息技术的飞速发展和企业界新需求的不断提出,以面向事务处理为主的空间数据库系 统已不能满足需要,信息系统开始从管理转向决策处理,空间数据仓库就是为满足这种新的 需求而提出的空间信息集成方案,它有四个特点:

2018-09-05 16:58:11 21

21 SRIO是面向嵌入式系统开发提出的高可靠、高性能、基于包交换的新一代高速互联技术,已于2004年被国际标准化组织(ISO)和国际电工协会(IEC)批准为ISO/IECDIS 18372标准。SRIO则是面向串行背板、DSP和相关串行数据平面连接应用的串行RapidIO接口。

2020-06-17 11:48:12 2555

2555 本文为您分享基于C66x+FPGA的SRIO开发视频教程,适用于创龙TMS320C6678、TMS320C665x、Kintex-7、Artix-7平台。

2020-07-01 10:47:39 1760

1760 近年来,随着面向对象数据库技术成熟,使用大型的RDBMS管理海量空间数据成为可能,企业化GIS数据组织和处理就显得非常必要。空间数据共享是当前地理信息系统建设的重要课题,而空间数据转换是实现信息共享

2020-09-17 16:07:00 13

13 基于Oracle-Spatial空间数据共享系统设计(肇庆理士电源技术有限公司图片)-该文档为基于Oracle-Spatial空间数据共享系统设计总结文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-09-16 13:59:08 1

1 随着PCIe接口、以太网接口的飞速发展,以及SOC芯片的层出不穷,芯片间的数据交互带宽大大提升并且正在向片内交互转变;SRIO接口的应用市场在缩小,但是由于DSP和PowerPC中集成了SRIO接口,因此在使用DSP/Power PC + FPGA的使用场景中仍然占有一席之地。

2022-08-02 10:00:26 3112

3112

目前具备SRIO接口的硬件不多,推荐广州星嵌电子科技有限公司开发的DSP+FPGA+RAM开发板XQ6657Z35-EVM。

2022-11-08 17:22:21 743

743

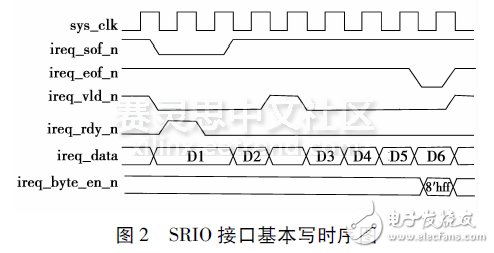

数据从远程设备(假设为DSP的SRIO端)传输过来,FPGA端(假设我们这端为FPGA的SRIO端口)通过RX接收到串行数据,先到达物理层进行时钟恢复,串并转换,之后进行8b/10b解码操作、CRC校验,这一系列的操作都在物理层完成,之后进入传输层

2023-03-03 10:19:53 725

725 摘要: 现代 信号 处理系统通常需要在不同处理器之间实现高速数据 通信 ,SRIO协议由于高效率、低延时的特性被广泛使用。本文研究了在 FPGA 和 DSP 两种处理器之间实现SRIO协议的方法

2023-03-20 15:00:01 1324

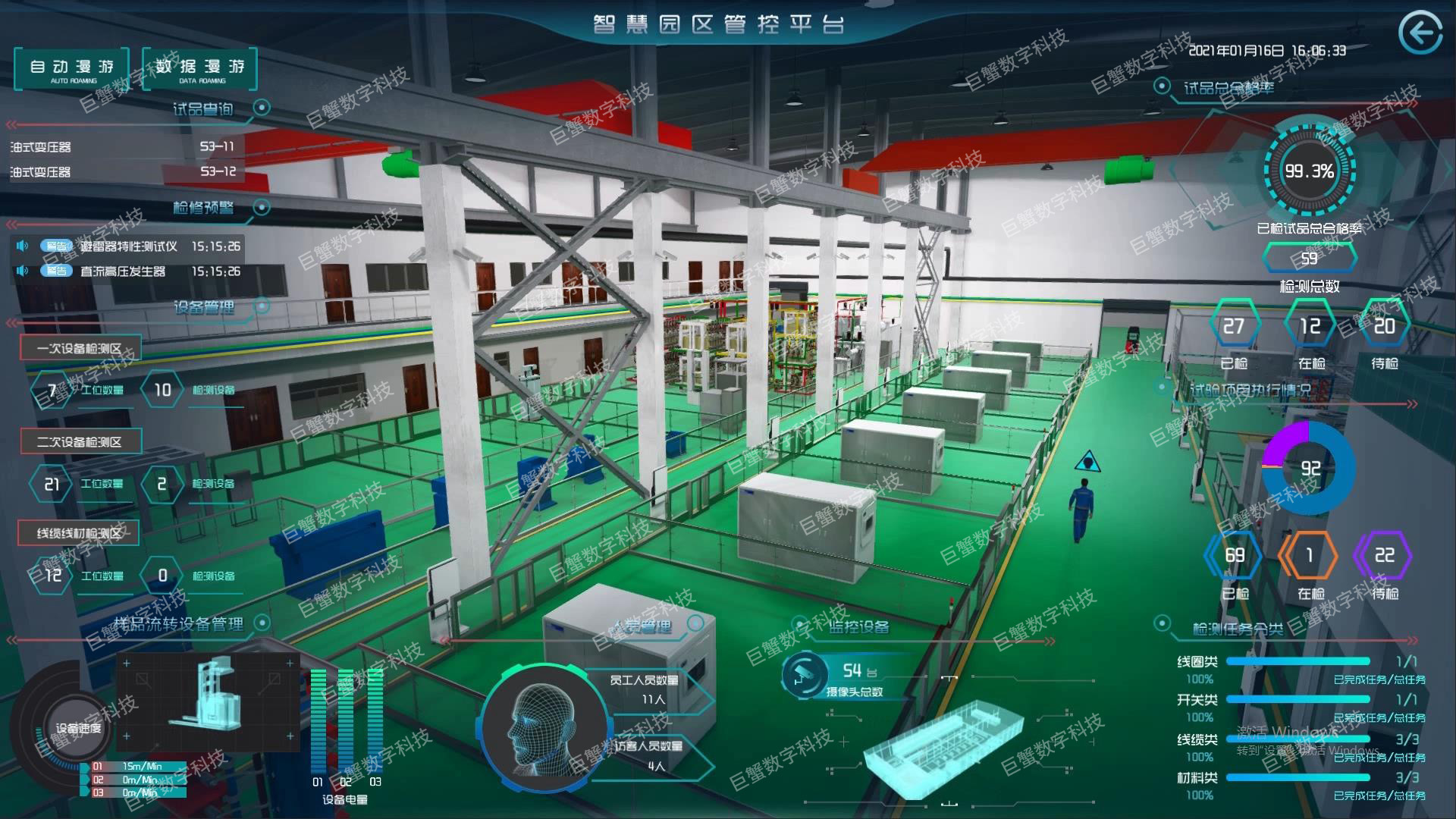

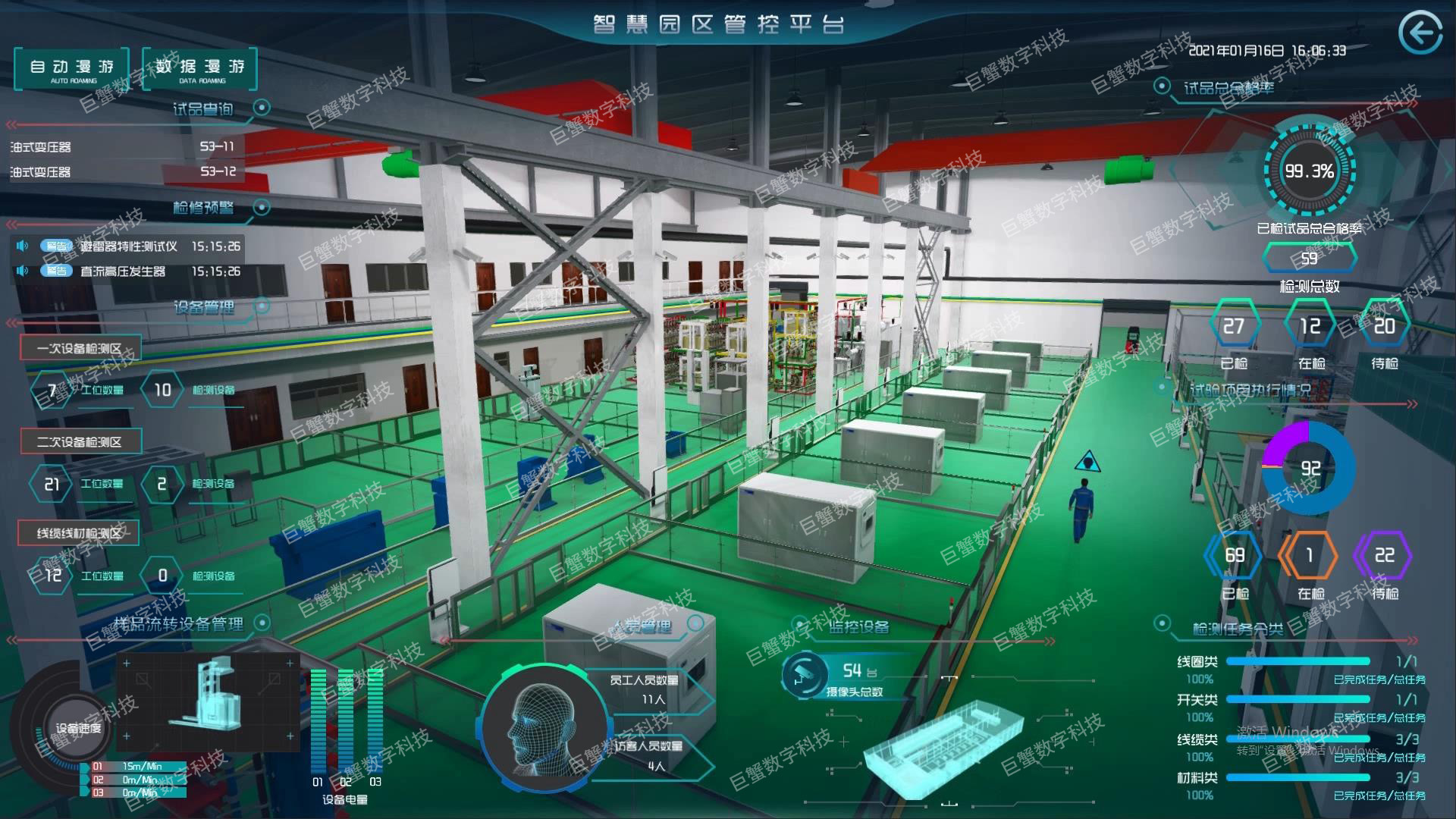

1324 河南郑州洛阳数字孪生智慧工厂,工厂车间数字化三维仿真交互,3d可视化数据大屏展示系统。在推动制造业迈向智能化的诸多技术之中,数字孪生备受关注,也被寄予厚望。巨蟹数字科技通过虚实融合,不仅可以实现可视化展示,还可以实现精准预警以及运营优化,成为传统工厂数智化建设转型的热门技术。

2023-03-31 14:18:42 478

478

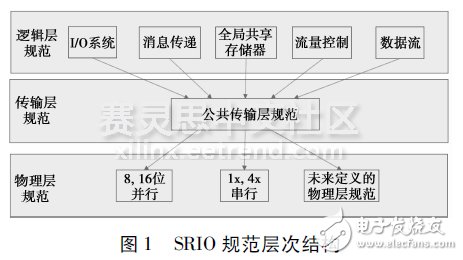

SRIO这种高速串口复杂就复杂在它的协议上,三层协议:逻辑层,传输层以及物理层。

数据手册会说这三层协议是干什么的呢?也就是分工(【FPGA】SRIO IP核系统总览以及端口介绍(一)(User Interfaces 之 I/O Port))

2023-04-25 11:20:55 1176

1176

目的:实现上位机与FPGAuart交互

开发环境:quatus prime 18.1,芯片 altera :EP4CE15F23C8。

实验现象: 1.使用uart:bps=9600(参数可调整

2023-05-08 10:28:33 2

2 本文介绍一个FPGA常用模块:SRIO(Serial RapidIO)。SRIO协议是一种高速串行通信协议,在我参与的项目中主要是用于FPGA和DSP之间的高速通信。有关SRIO协议的详细介绍网上有很多,本文主要简单介绍一下SRIO IP核的使用和本工程的源代码结构。

2023-09-04 18:19:18 683

683

等领域,以实现设备之间的高速、低延迟数据交互。SRIO交换芯片的出现,极大地提升了数据传输效率和系统性能。

2024-03-16 16:40:42 1567

1567

正在加载...

电子发烧友App

电子发烧友App

评论