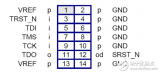

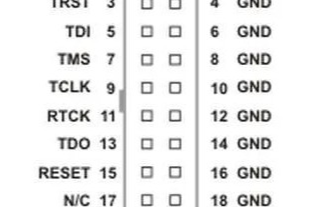

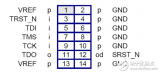

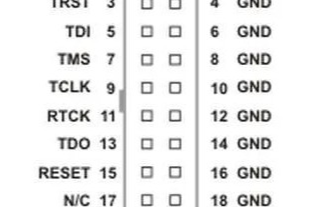

JTAG接口主要包括以下四个引脚:TMS TCK TDI和TCO及一个可选配的引脚TRST,用于驱动电路模块和控制执行规定的操作。

2014-09-15 12:44:31 22903

22903

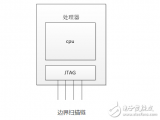

ARM系列处理器正是通过JTAG 接口使用内部集成的ICE 功能, 并采用这种方式实现在线调试。此外CPLD、FPGA 等器件大多都可以使用JTAG 接口实现在线编程或下载。因此,JTAG 接口已经成为复杂芯片系统的必备接口, 在芯片测试、调试及实现其他特殊功能方面发挥着重要作用。

2018-10-16 08:11:00 5801

5801

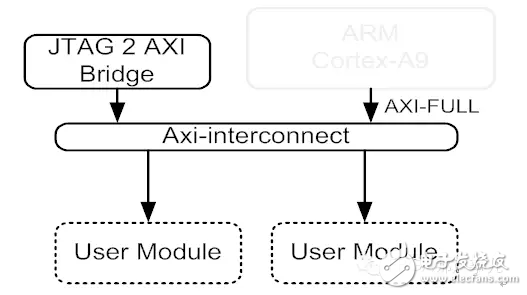

AXI接口虽然经常使用,很多同学可能并不清楚Vivado里面也集成了AXI的Verification IP,可以当做AXI的master、pass through和slave,本次内容我们看下

2023-07-27 09:19:33 633

633

的输出信号都在上升沿时变化。 2.ARESETn 全局复位信号,低电平有效。在复位期间,所有的xxVALID信号必须复位为低电平。其他的信号可以是任意值。 主机(master)控制的信号

2021-01-08 16:52:32

的axi quad spi ip core。 线连接如下所示:slave_io0_i - master_io0_o slave_io1_o - master_io1_i slave_clk_i

2020-04-17 10:13:04

Axi4ReadOnlyDecoder对于Axi4读操作而言,其指令的完成由ar、r两个通道完成,相较于写操作,其通道数虽然少了一个,但也是两个方向的数据流:ar:master——>

2022-08-04 14:28:56

“hw_axi_1”作为上面的第二个参数?如果您知道只有一个JTAG到AXI IP连接到调试集线器,为什么还需要一个列表(这是一个列表?)。 UG825(v2016.2)的第250页将此参数称为“并将其描述为”关联

2020-05-20 09:11:18

,如下截图。有时候手动选择JTAG 调试时 JTAG Device Chain下面没有可以选择的东西,只能选择SW调试,选JTAG 有时报错我没截到图。有没有大虾可以帮帮忙,求助?

2019-03-22 04:26:17

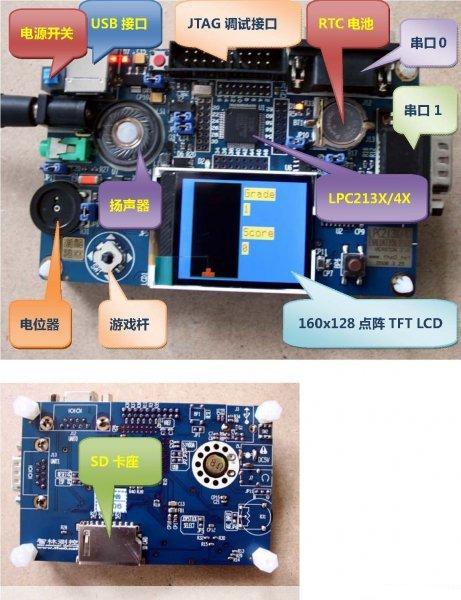

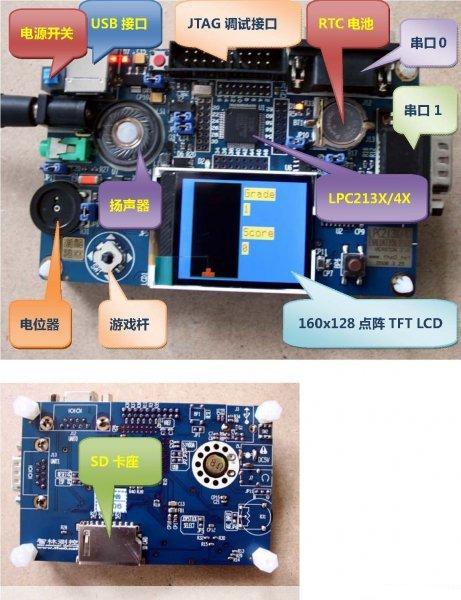

JTAG 作为一个通用的标准器件功能测试接口, 具有灵活高效、易于实现等优点, 是微控制器、微处理器、DSP、SoC 等器件的重要外部接口。它不但可以用来测试内部功能模块状态, 而且可以实现在线调试

2019-08-27 06:18:54

JTAG调试:协议转换器解释上位机传送过来的命令,通过JTAG控制ARM执行z Angel调试:协议转换器可以直接做为目标板的Firmware的一部分。直接执行从宿主机传送过来的调试命令;并回送相应

2017-11-07 14:53:44

CPU核通信,实现了完全非插入式调试,不使用片上资源,不需要目标存储器,不占用目标系统的任何端口。由于JTAG调试的目标程序是在目标板上执行,使得仿真更加接近于目标硬件[1]。目前针对嵌入式系统

2019-10-18 06:33:42

ARM-JTAG调试原理

2012-08-03 22:00:11

ARM.JTAG.调试原理

2018-02-05 09:43:30

[hide]ARM.JTAG.调试原理/[/hide]

2013-10-20 16:53:24

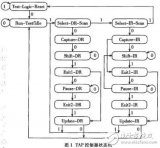

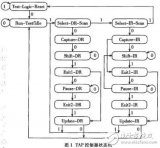

这篇文章主要介绍 ARM JTAG 调试的基本原理。 基本的内容包括了 TAP (TEST ACCESSPORT) 和 BOUNDARY-SCAN ARCHITECTURE 的介绍, 在此基础上

2017-11-07 14:56:55

正确执行任何其他读取操作。在PSoC创建者中显示以下错误:dg.M033:选定的调试目标“CY8C5688 AXI-060未分配”与项目选定的设备“CY8C5688 AXI-060 ES1”不兼容

2019-04-02 14:17:24

API函数实现JTAG to AXI Master的读写通过调用SDK里的API函数,可以实现通过JTAG线与FPGA内部逻辑通信。即在FPGA内部例化SDK里的IP(JTAG转localbus或者

2020-09-27 10:45:13

用中断,波特率1000,片选、ENA管脚用作普通的IO口。程序工作过程:570主设备发送一个字符到从设备,从设备立即把这个字符返回发给主设备570。

出现的问题:在使用JTAG单步调试的时候

2018-06-21 09:36:14

大部分器件的接口要求,提供互联架构的灵活性与独立性。

(1)AXI总线

总线是一组传输通道,是各种逻辑器件构成的传输数据的通道,一般由数据线、地址线、控制线等构成。在ZYNQ中支持三种AXI总线

2023-11-03 10:51:39

ARM JTAG调试时检测不到目标系统 答:调试前,请把目标板连接好,然后用调试软件检测目标系统。如果检测不到目标系统,请做以下的检查。A - 有些芯片是可以加密的,加密后JTAG接口就自动被禁

2011-11-30 10:18:29

我根据以下快速拍摄视频完成了我的设计:http://www.xilinx.com/video/hardware/using-jtag-to-axi-master-in-vivado.html在视频

2020-08-12 09:16:08

user_clk从端点连接到AXI configuredILA的时钟端口时,似乎永远不会出现在硬件管理器中(在调试探针窗口中)。 a)这是否必须对自由运行时钟要求做些什么? b)我使用了缓冲的系统时钟(来自

2019-09-25 09:26:14

AXI总线在FPGA设计中使用越来越频繁,但初学的同学经常会因为对协议的理解不够深入,写出来的代码经常会出现死锁等问题,对FPGA设计与调试带来很多不必要的麻烦。为了解决这个问题,我们可以

2022-10-09 16:08:45

幸运的是,isee“Zynq-7000示例设计 - 使用Master AXI GP访问AXI Slave的CPU吞吐量”。以下列表是结果。我能否得出结论,使用Master AXI GP访问AXI

2019-11-01 09:31:44

调试ARM,要遵循arm的调试接口协议,JTAG就是其中的一种。当仿真时,IAR、KEIL、ADS等都有一个公共的调试接口,RDI就是其中的一种,那么我们如何完成RDI-->arm调试协议

2022-05-24 15:53:14

嵌入式系统交叉调试方法一般分为两种,一种是基于JTAG的片上调试方法,一种是基于调试代理的远程调试方法。JTAG是一种国际标准芯片测试协议,目前大多数CPU体系都支持JTAG。基于JTAG的片上调试

2017-12-18 10:55:39

我对AXI互连有疑问,1.我的AXI4 Masterwith数据宽度为32位。我有64位数据宽度的AXI3从器件。互连如何工作?2.如果我有64位的PL AXI3 Master,我想连接到PS

2019-04-01 10:10:35

求大佬分享uart2axi_master_intf程序源码

2022-02-22 06:43:59

是通过配置ZYNQ系统自动生成的;axi_gp_top.v模块以及其下的两个子模块,是这个实例我们自己动手编写的逻辑。axi_gp_ctrl.v模块对AXI GP总线的控制、地址时序进行译码

2019-11-12 10:23:42

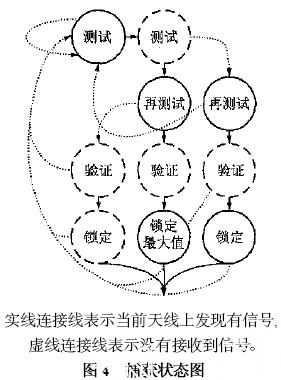

测试机。IBERT是针对高速串行接口的在线调试和验证。通过IBERT的检测,可以确认FPGA内部的高速串行口传输数据的可靠性和稳定性。JTAG-to-AXI Master,即JTAG-to-AXI主机

2019-05-24 15:16:32

我使用vivado 2014.4使用JTAG到AXI Master进行调试设计。当我运行实现时,系统有错误[Drc 23-20]规则违规(RPBF-2)IO端口驱动逻辑 - 设备端口clk驱动逻辑

2020-05-01 15:01:24

是:使用designware AHB2AXI IP,将AHB master转换成AXI master,同时设置AXI总线上的pipeline options(当然相应的也要将原先的AHB slave改为AXI slave

2021-06-23 09:01:13

的Linux的xdevcfg设备来编程PL部件。有趣的解决方案是通过在同一芯片的PS部分运行的XVC远程调试基于Zynq的设计。假设我将XAPP1251中描述的AXI-JTAG控制器添加到我的设计中,是否

2020-07-30 13:51:19

JTAG先进的功能和系统设计,JTAG Advanced Capabilities and System Design

The JTAG bus, originally intended

2009-05-16 09:57:30 32

32 JTAG调试原理(推荐):ARM JTAG 调试原理

2009-05-27 08:59:49 21

21 JTAG调试原理(推荐):温度循环监测仪

2009-05-27 10:38:59 54

54 JTAG调试原理(推荐):这篇文章主要介绍ARM JTAG调试的基本原理。基本的内容包括了TAP (TEST ACCESS PORT) 和BOUNDARY-SCAN ARCHITECTURE的介绍,在此基础上,结合ARM7TDMI详细介绍了的JTAG调试原

2009-05-27 10:44:50 147

147 这篇文章主要介绍ARM JTAG调试的基本原理。基本的内容包括了TAP (TEST ACCESS PORT) 和BOUNDARY-SCAN ARCHITECTURE的介绍,在此基础上,结合ARM7TDMI详细介绍了的JTAG调试原理。这篇文章主要是

2009-07-14 23:19:49 82

82 嵌入式ARM 软、硬件调试技术依赖于ARM 处理器调试硬件,本文在分析JTAG 边界扫描结构的基础上,介绍了EmbeddedICE、嵌入式跟踪等实时调试技术,并给出了一个嵌入式调试开发系统

2009-08-14 15:55:42 5

5 ARM与JTAGJTAG(Joint Test Action Group ,联合测试行动小组 ) 是一种国际标准测试协议,主要用于芯片内部测试及对系统进行仿真、调试, JTAG 技术是一种嵌入式调试技术,它在芯片内

2009-09-13 10:57:35 85

85 嵌入式JTAG调试方法步骤

嵌入式系统JTAG调试步骤1. 将PC与调试器Multi-ICE用并口连接;调试器与开发板用14或20针的JTAG线连接。2. 依次打开调试器

2010-03-01 16:24:20 34

34 什么是jtag接口

JTAG(Joint Test Action Group ,联合测试行动小组 ) 是一种国际标准测试协议,主要用于芯片内部测试及对系统进行仿真、调试, J

2007-12-20 13:40:08 47060

47060

JTAG技术是一种嵌入式调试技术,芯片内部封装了专门的测试电路TAP(测试访问口),通过专用的JTAG测试工具对内部节点进行测试和控制,目前大多数ARM器件支持JTAG

2008-08-24 13:10:39 8144

8144

JTAG调试快速入门

提要:本文介绍 AVR Studio Debug:调试运行方式及QuickWatch实时查看变量的数值。

以下的degug方式,英文版来自 AVR St

2008-10-31 21:58:10 2055

2055 一种嵌入式系统实现的JTAG调试器

JTAG 作为一个通用的标准器件功能测试接口, 具有灵活高效、易于实现等优点, 是微控制器、微处理器、DSP、SoC 等器

2009-10-06 09:53:55 1106

1106

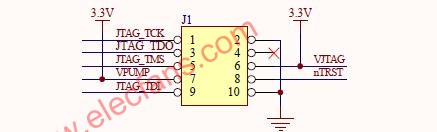

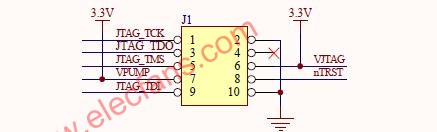

JTAG调试接口电路

注:VPUMP和VJTAG需要接3.

2010-03-17 09:25:56 2554

2554

基于JTAG仿真器的调试是目前ARM开发中采用最多的一种方式。大多数ARM设计采用了片上JTAG接口,并将其作为测试、调试方法的重要组成。

JTAG仿真器通过ARM芯片的JTAG边界扫描

2010-06-30 15:20:03 3001

3001

本内容向大家提供了JTAG功能及系统设计 JTAG也是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。现在多数的高级器件都支持JTAG协议,如DSP、FPGA器件等。标准的JTAG接口是

2011-03-30 10:04:32 0

0 本内容提供了ARM JTAG调试头和Altera下载线合并电路 详细列举了电路原理图

2011-03-31 17:19:22 209

209 ARM处理器采用一种基于JTAG的ARM的内核调试通道,它具有典型的ICE功能,基于ARM的包含有Embedded ICE(嵌入式在线仿真器)模块的系统芯片通过JTAG端口与主计算机连接。

2011-08-16 09:51:08 2371

2371

这篇文章主要介绍ARM JTAG调试的基本原理。基本的内容包括了TAP (TEST ACCESS PORT) 和BOUNDARY-SCAN ARCHITECTURE的介绍,在此基础上,结合ARM7TDMI详细介绍了的JTAG调试原理。 这篇文章主要是总结了

2011-11-15 17:35:39 0

0 Altera JTAG下载和调试接口电路图如下图所示:

2012-08-15 14:25:22 13966

13966

电子发烧友网站提供《H-JTAG调试软件下载.exe》资料免费下载

2012-12-18 13:15:34 57

57 STM32 调试器不能通过 JTAG 连接器件

2015-12-07 17:52:55 0

0 IAR+H_JTAG调试FLASH说明及例程。

2016-02-18 15:11:44 4

4 ARM JTAG 调试原理对于了解jtag结构由很好的帮助。

2016-03-10 14:08:48 10

10 H-JTAG 用户使用手册简单介绍了 H-JTAG 和 H-FLASHER 的基本使用和配置,手册同时也提供了一

些简单的例子供用户参考

2016-05-03 15:15:08 6

6 AXI总线的MicroBlaze双核SoPC系统设计

2017-10-31 08:54:44 8

8 JTAG编程方式是在线编程,传统生产流程中先对芯片进行预编程实现再装到板上因此而改变,简化的流程为先固定器件到电路板上,再用JTAG编程,从而大大加快工程进度。JTAG接口可对PSD芯片内部的所有部件进行编程

2017-12-10 10:20:22 9779

9779

调试ARM,要遵循ARM的调试接口协议,JTAG就是其中的一种。当仿真时,IAR、KEIL、ADS等都有一个公共的调试接口,RDI就是其中的一种,那么我们如何完成RDI--》ARM调试协议(JTAG)的转换呢?

2017-12-10 10:40:02 10967

10967 JTAG(JointTestActionGroup,联合测试行动小组)是一种国际标准测试协议,主要用于芯片内部测试及对系统进行仿真、调试,JTAG技术是一种嵌入式调试技术,它在芯片内部封装了专门

2018-01-11 09:45:50 28818

28818

本文从引脚、调试方式、仿真器的支持和硬件接口四个方面对jtag和swd进行了详细的对比区别。

2018-01-11 10:06:23 133181

133181

者能够通过JTAG接口,用开放的硬件和软件系统进行烧写、校验和调试。他们都基于JTAG调试接口协议。

2018-01-30 09:29:10 17445

17445

IARMSP430项目编译与JTAG仿真调试步骤。

2018-04-19 08:29:09 5

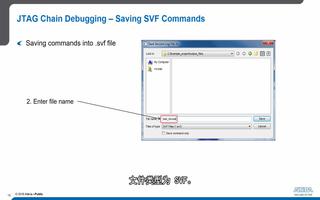

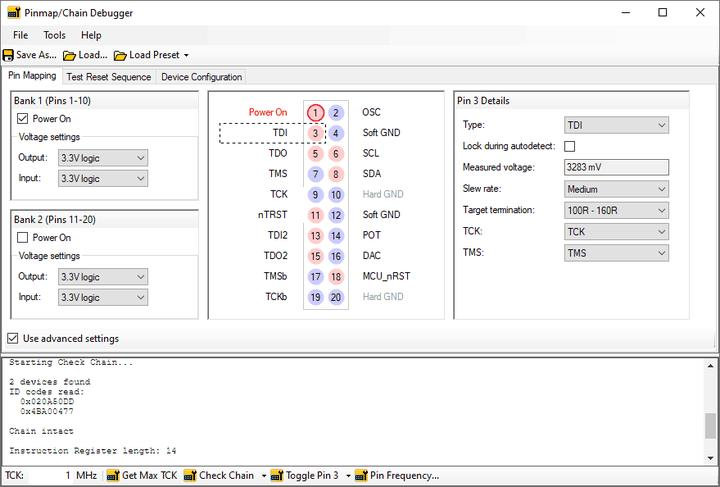

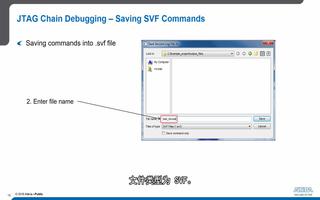

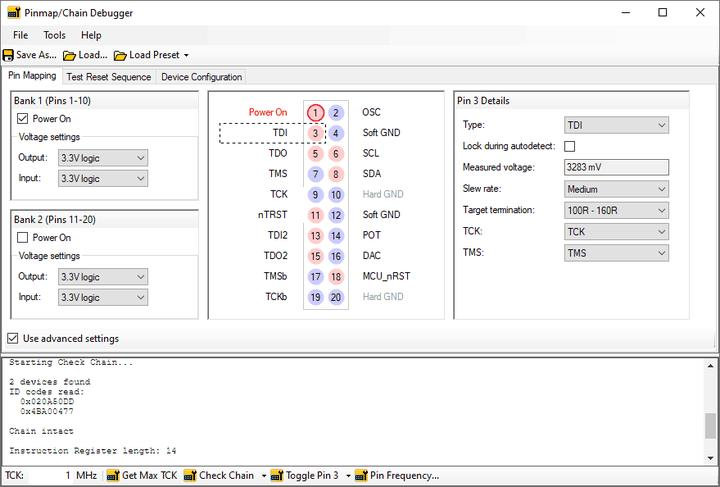

5 JTAG 链调试程序工具

2018-06-20 01:00:00 3687

3687

了解如何使用Xilinx AXI验证IP有效验证和调试AXI接口。

该视频回顾了使用的好处,以及如何使用示例设计进行模拟。

2018-11-20 06:38:00 3561

3561 了解如何使用Vivado Design Suite IP Integrator有效地调试AXI接口。

本视频介绍了如何使用该工具的好处,所需的调试步骤和演示。

2018-11-29 06:00:00 3680

3680 产品名称:Jtag调试小板

2019-11-13 09:53:10 2071

2071

RK3399系统调试架构,支持 JTAG/SW 和 TRACE_DATA 两种输出接口。这里主要介绍JTAG/SW 。

2019-12-17 16:40:39 19

19 bug 最有效直接的方式,今天我们要聊的是调试里最基础的东西,即接口标准。ARM 内核原生支持 2 种业界通用的接口标准,分别是 JTAG 和 SWD。本节课痞子衡先给大家详细讲讲 JTAG 接口。

2020-02-12 16:03:37 6072

6072

JTAG是Joint Test Action Group的缩写,是IEEE 1149.1标准。使用JTAG的优点:JTAG的建立使得集成电路固定在PCB上,只通过边界扫描便可以被测试。在ARM7TDMI处理器中,可以通过JTAG直接控制ARM的内部总线、I/O口等信息,从而达到调试的目的。

2020-08-10 16:42:33 2022

2022 JTAG是Joint Test Action Group的缩写,是IEEE 1149.1标准。使用JTAG的优点:JTAG的建立使得集成电路固定在PCB上,只通过边界扫描便可以被测试。

2020-08-27 14:18:48 2860

2860 在FPGA程序设计的很多情形都会使用到AXI接口总线,以PCIe的XDMA应用为例,XDMA有两个AXI接口,分别是AXI4 Master类型接口和AXI-Lite Master类型接口,可通过

2020-10-30 12:32:37 3953

3953

新的赛灵思器件设计中不可或缺的一部分。充分了解其基础知识对于赛灵思器件的设计和调试都很有帮助。 本篇博文将介绍赛灵思器件上的 AXI3/AXI4 的相关基础知识。首先,我们将从一些通俗易懂的知识、理论

2020-09-27 11:06:45 5857

5857

器 简单来说,下载调试器是将PC(例如通过USB协议)发送的命令转换为MCU(负责MCU内部外围设备)理解的语言(例如SWD或JTAG协议)的设备,加载代码并精确控制执行。 2 调试器协议标准 1.什么是标准? 简单来说,标准是一组规则和协议,特定行业中的每个参与者都同意遵循并执行。 2.调试器协议混乱现

2020-10-27 09:29:17 16100

16100

为 MCU(负责 MCU 内部外围设备)理解的语言(例如 SWD 或 JTAG 协议)的设备,加载代码并精确控制执行。 2、调试器协议标准 1. 什么是标准? 简单来说,标准是一组规则和协议,特定行业中的每个参与者都同意遵循并执行。 2. 调试器协议混乱现象 在 SWD 和 JTAG 之类的协

2022-11-28 11:44:06 3840

3840 在 AMBA 系列之 AXI 总线协议初探 中,了解到 AXI 总线交互分为 Master / Slave 两端,而且标准的 AXI 总线支持不同的位宽,既然是总线,那么必须要支持总线互联,多 Master,多 Slave的场景

2022-02-08 11:44:02 12802

12802 在 AMBA 系列之 AXI 总线协议初探 中,了解到 AXI 总线交互分为 Master / Slave 两端,而且标准的 AXI 总线支持不同的位宽,既然是总线,那么必须要支持总线互联,多 Master,多 Slave的场景

2021-02-23 06:57:00 45

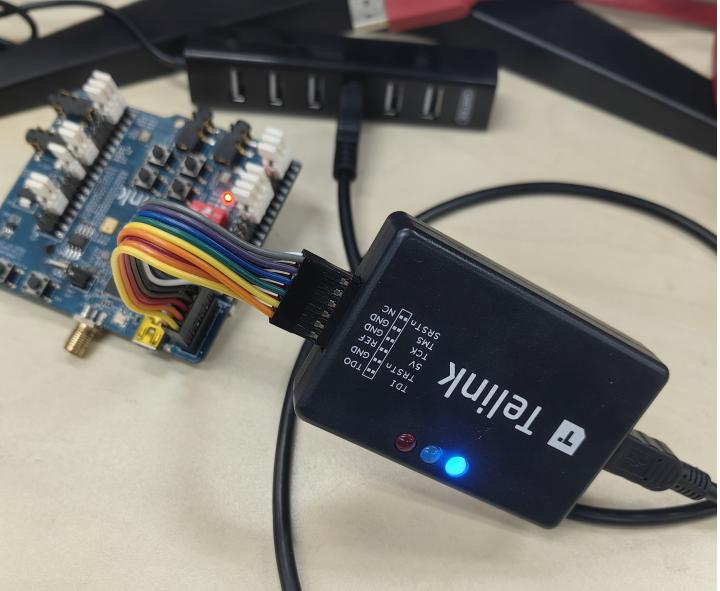

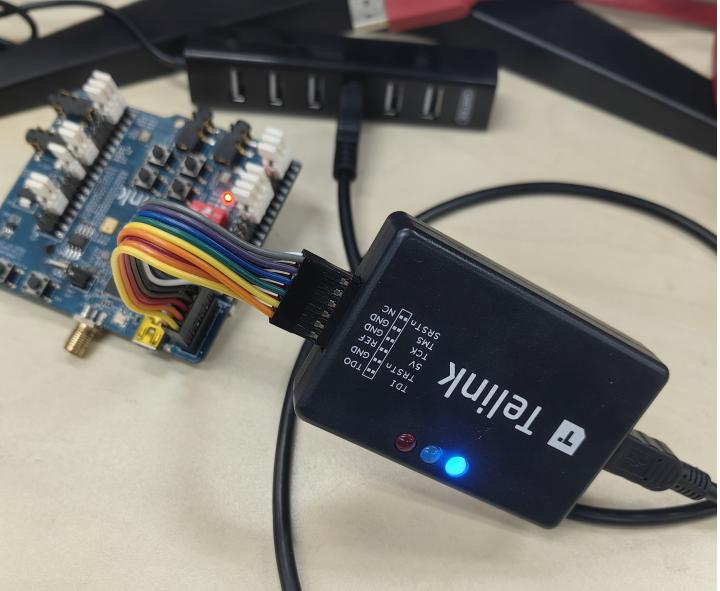

45 开发板(在本文中将其简称为“FPGA开发板”)和专用 JTAG 调试器(在本文中将其简称为“JTAG 调试器”)。

2021-03-23 10:00:28 41

41 在传统上,JTAG调试技术主要是用于硬件Bring-Up,如今也常常被用于配合基于代理的调试(agent-based debugging)。然而,在多核和多处理的环境中,片上调试(on-chip

2021-04-05 10:19:00 2988

2988

在一个项目中,当你使用microblaze作为控制器来进行系统调度的时候,一般是建议将所有模块封装成AXI形式的IP核,这样好管理,也容易调试。

2021-04-27 11:17:36 5652

5652

STM32F103C8T6 核心板最小系统 Jtag调试下载接线图如图jtag模式1 VDD 棕3 TRST----PB4 红5 TDI----PA15 橙7 TMS/SWDIO----PA13

2021-11-18 10:21:06 59

59 JTAG与SWD的含义与引脚前言一、JTAG二、SWD总结前言最近使用M0搭建了一个最基础的SoC但是在使用keil进行软件调试的过程中遇到了不小的问题,这里对常见的两种调试方式做一个总结

2021-12-22 19:05:58 17

17 uart2axi_master_intf程序源码:/**************************************************** Module Name

2021-12-28 20:04:42 14

14 对FPGA进行上板调试时,使用最多的是SignalTap,但SignalTap主要用来抓取信号时序,当需要发送信号到FPGA时,Jtag Master可以发挥很好的作用,可以通过Jtag Master对FPGA进行读写测试

2022-02-16 16:21:36 1900

1900

本文给大家提供利用axi_master接口指令端的几个静态参数的优化技巧,从扩展总线接口数量,扩展总线位宽,循环展开等角度入手。最核心的优化思想就是以资源面积换取高带宽的以便并行计算。

2022-07-01 09:39:14 1015

1015 对 AXI master的全面讨论变得困难。我还没有(还)想出如何简化材料来写一篇关于如何构建通用 AXI master器的帖子,这已经够难了——通常来说,寻址就是那么难。

2022-07-29 11:27:17 991

991 AXI IIC 和 PS IIC 控制器都符合 NXP IIC 总线规范。用户必须确保其选择使用的从设备的时序参数与UM10204 的第 48 页上的“表 10”中的参数相同。

2022-08-25 10:29:08 1169

1169 AXI总线在FPGA设计中使用越来越频繁,但初学的同学经常会因为对协议的理解不够深入,写出来的代码经常会出现死锁等问题,对FPGA设计与调试带来很多不必要的麻烦。为了解决这个问题,我们可以

2022-10-08 16:07:11 3846

3846 JTAG链调试器(JTAG Chain Debugger),随XJTAG的安装包一起安装,是一个功能强大的工具,旨在帮助您解决JTAG链的问题。

2023-07-19 14:41:07 319

319

AXI接口虽然经常使用,很多同学可能并不清楚Vivado里面也集成了AXI的Verification IP,可以当做AXI的master、pass through和slave,本次内容我们看下AXI VIP当作master时如何使用。

2023-07-27 09:16:13 792

792

LogiCORE JTAG至AXI Master IP核是一个可定制的核,可生成AXIAXI总线可用于处理和驱动系统中FPGA内部的AXI信号。AXI总线接口协议可通过IP定制Vivado

2023-10-16 10:12:42 410

410

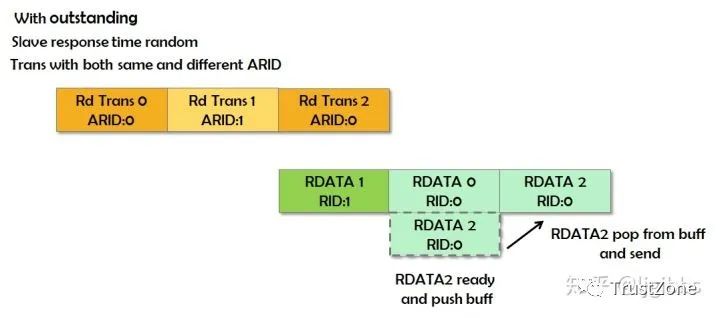

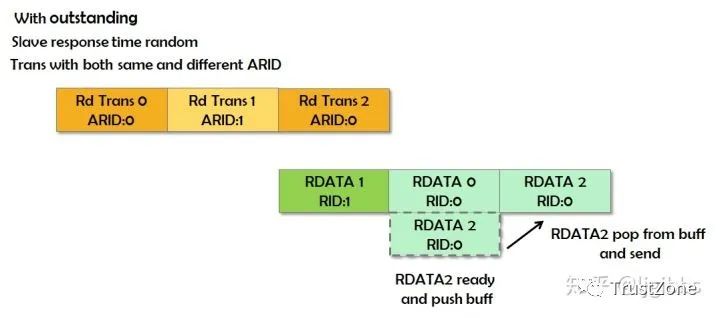

AXI的控制和数据通道分离,可以带来很多好处。地址和控制信息相对数据的相位独立,可以先发地址,然后再是数据,这样自然而然的支持显著操作,也就是outstanding 操作。 Master访问

2023-10-31 16:53:09 432

432

Group”的缩写,是一种硬件调试和测试技术,常被用于在集成电路中诊断和调试问题。JTAG的正式名称为IEEE 1149.1标准,是一种通过扫描链(scan chain)实现的测试方法,该方法可以在不破坏芯片的情况下,对集成电路进行测试和调试。JTAG技术广泛应用于数字集成电路、嵌入式系统和电路板等硬件开

2023-12-20 10:00:03 490

490

因为目前软件的限制,RISCV的逻辑不能同时共用JTAG,所以如果想要同时去调试逻辑和RISCV的话,可以通过RISCV的soft Jtag来实现。soft Jtag就是通过GPIO来实现的软件

2024-02-23 16:16:12 110

110

电子发烧友App

电子发烧友App

评论