CNN已经广泛用于图像识别,因为它能模仿生物视觉神经的行为获得很高识别准确率。最近,基于深度学习算法的现代应用高速增长进一步改善了研究和实现。特别地,多种基于FPGA平台的深度CNN加速器被提出,具有高性能、可重配置、快速开发周期等优势。

尽管目前FPGA加速器已经展示了相比通用处理器更好的性能,加速器设计空间并没有很好发掘。一个严重的问题是,一个FPGA平台的计算吞吐并未很好匹配内存带宽。因此,已有的方案要么未充分利用逻辑资源,要么未充分利用内存带宽,都不能获得最佳性能。同时,深度学习应用不断增加的复杂度和可扩展性让这个问题更加严重。

为了克服这个问题,我们利用roofline模型提出一种设计分析方法。对于任意CNN设计方案,我们量化分析它使用不同优化技术(循环分块、变换)的计算吞吐和所需内存带宽。在roofline模型帮助下,我们可以发现最好性能和最低FPGA资源需求的解决方案。

作为案例研究,我们在VC707 FPGA板卡上实现了一个CNN加速器,并将它与之前的方案对比。我们的实现在100MHz工作频率下可获得61.62GFLOPS的峰值处理能力,大大优于之前的方案。

【1. 简介】

CNN是著名的深度学习架构,从人工神经网络扩展而来,它已经大量用于不同应用,包括视频监控,移动机器人视觉,数据中心的图像搜索引擎等【6】【7】【8】【10】【14】

受生物视觉神经行为的启发,CNN用多层神经元相连处理数据,在图像识别中可获得很高准确率。最近,基于深度学习算法的现代应用快速增长进一步改善了DCNN的研究。

由于CNN的特殊计算模式,通用处理器实现CNN并不高效,所以很难满足性能需求。于是,最近基于FPGA,GPU甚至ASIC的不同加速器被相继提出【3】【4】【9】以提升CNN设计性能。在这些方案中,基于FPGA的加速器由于其更好的性能,高能效,快速开发周期以及可重配置能力吸引了越来越多研究者的注意【1】【2】【3】【6】【12】【14】。

对于任意CNN算法实现,存在很多潜在解决方案,导致巨大的设计空间。在我们的实验中,我们发现使用同样FPGA逻辑资源的不同方案性能有最大90%差距。寻找最优解不无价值,尤其当考虑FPGA平台计算资源和内存带宽限制时。实际上,如果一个加速器结构并未仔细设计,它的计算吞吐与内存带宽不匹配。未充分利用逻辑资源或内存带宽都意味着性能下降。

不幸的是,FPGA技术进步和深度学习算法同时将该问题复杂化了。一方面,当前FPGA平台不断提升的逻辑资源和内存带宽扩大了设计空间,采取不同FPGA优化技术(如循环分块、变换)会进一步扩大设计空间。另一方面,为了满足现代应用需求,深度学习可扩展性和复杂性在持续增长。因此,在巨大的设计空间中寻找最优解就更加困难,亟需一种高效检索基于FPGA的CNN设计空间的方法。

为了高效检索设计空间,本文提出了分析设计的方法。我们的工作优于以前的方法,原因有二:

首先,【1,2,3,6,14】主要关注计算引擎优化,要么忽视了外部存储器操作,要么直接将他们的加速器接入外部存储器。我们的工作则考虑了缓冲区管理和带宽优化。

其次,【12】通过数据重用减少了外部数据获取从而获得加速。但是这种方法不必导致最优全局性能。另外他们的方法需要对每层重新配置,不太方便。我们的加速器无需重编程FPGA就能执行不同层的计算。

本文主要贡献如下:

* 量化分析可能解决方案的计算吞吐和所需内存带宽;

* 在计算资源和内存带宽限制下,我们用roofline模型识别所有可能的解决方案,讨论了不同层如何寻找最优解;

* 我们提出一种CNN加速器设计,对每层使用统一的循环展开因子;

* 实现了CNN加速器,获得61.62GFLOPS处理性能,是目前最优的;

【2. 背景】

2.1 CNN基础

CNN受神经科学研究的启发,经过长达20多年的演变,CNN在计算机视觉、AI(【11】【9】)领域越来越突出。作为一种经典有监督学习算法,CNN使用前馈处理用于识别,反馈用于训练。在工业实践中,很多应用设计者离线训练CNN,然后用训练好的CNN实现实时任务。因此,前馈计算速度是比较重要的。本文关注用基于FPGA的加速器设计前馈计算加速。

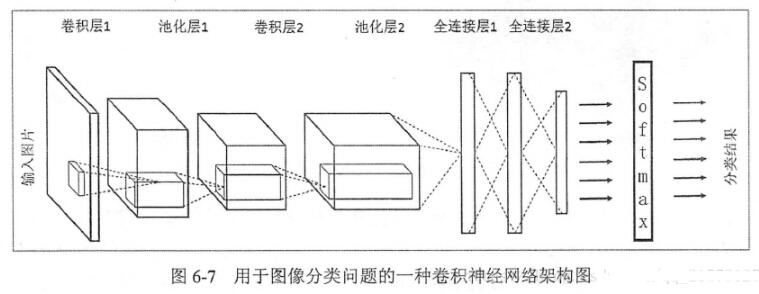

一个典型CNN由两部分组成:特征提取器 + 分类器。

特征提取器用于过滤输入图像,产生表示图像不同特征的特征图。这些特征可能包括拐角,线,圆弧等,对位置和形变不敏感。特征提取器的输出是包含这些特征的低维向量。

该向量送入分类器(通常基于传统的人工神经网络)分类器的目的是决定输入属于某个类别的可能性。

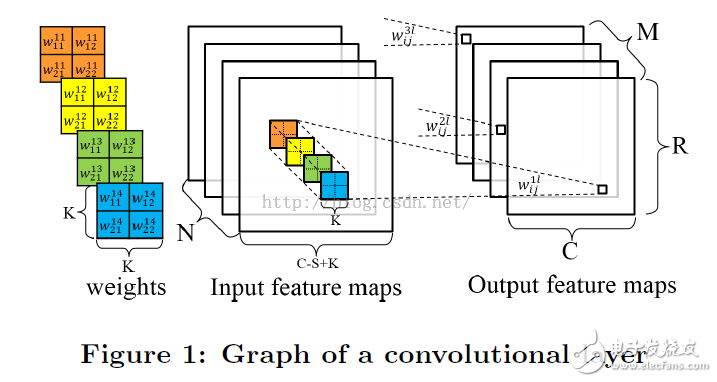

一个典型CNN包括多个计算层,例如,特征提取器可能包括几个卷积层和可选的下采样层。图1展示了卷积层的计算。

卷积层收到N个特征图作为输入,每个输入特征图被一个K * K的核卷积,产生一个输出特征图的一个像素。滑动窗的间隔为S,一般小于K。总共产生M个输出特征图用于下一卷积层。卷积层的伪代码如下:

for(row = 0; row < R; row ++)

{

for(col = 0; col < C; col ++)

{

for(to = 0; to < M; to ++)

{

for(ti = 0; ti < N; ti ++)

{

for(i = 0; i < K; i++)

{

for(j = 0; j < K; j++)

{

output_fm[to][row][col] += weights[to][ti][i][j] * input_fm[ti][S * row + i][S * col + j];

}

}

}

}

}

}

在前馈计算角度,之前的论文【5】证明卷及操作会占据超过90%的总计算时间,所以本文我们关注加速卷积层。后面会考虑集成其他可选层,如下采样层、最大池化层。

一个真实的CNN

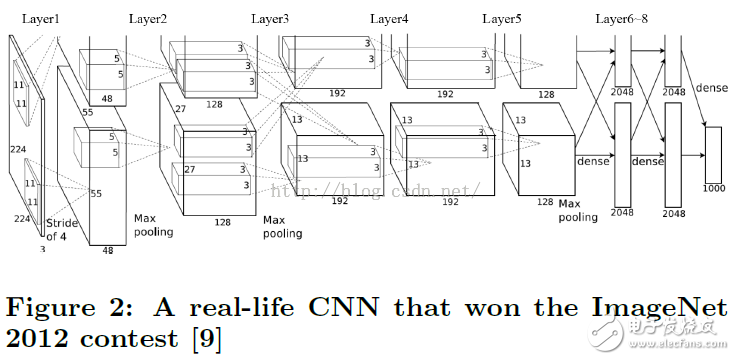

图2展示了一个真实CNN应用,摘自【9】。该CNN包括8层,前5层为卷积层,第6~8层为全连接人工神经网络。该算法接收3通道224x224输入图像(从原始256x256三通道RGB图像变换而来),输出1000维向量表示1000个类别的可能性。

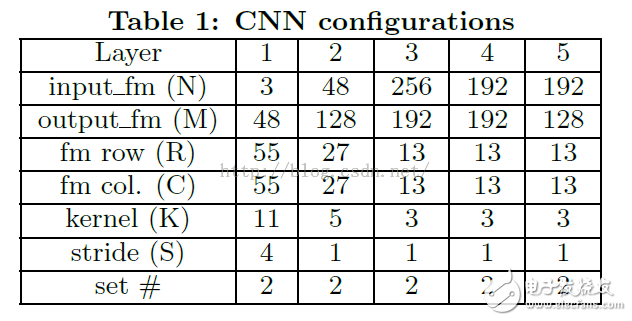

第一层输入为3个224x224分辨率的特征图,输出96个55x55分辨率的特征图,输出分为两个集,每个48组特征图。表1记录了该CNN的配置。

2.2 Roofline模型

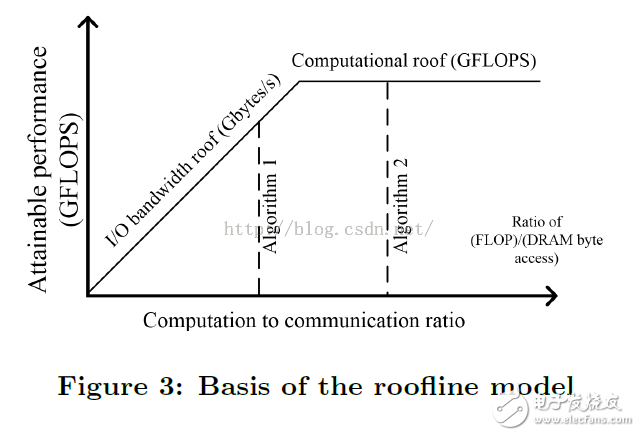

计算和通信是系统吞吐优化的两个基本限制。一个实现可能是计算受限的或访存受限的。【15】开发了roofline性能模型来将系统性能同片外存储带宽、峰值计算性能相关联。

公式(1)表示了特定硬件平台的可达吞吐率,用GFLOPS作为评估指标。

一个应用实际GFLOPS不会高于这两项中的最小值:第一项为所有可用计算资源提供的峰值计算能力(计算上限),第二项为给定计算-通信比时系统访存带宽可支持的最大浮点性能(IO带宽上限)。计算-通信比,又称每DRAM传输运算量,表示特定系统实现所需的DRAM访问量。

图3将roofline模型可视化,分别展示了计算上限和IO带宽上限。算法2相比算法1有更高计算-通信比,或更好的数据重用.从图中看到算法2充分利用所有硬件计算资源,性能优于算法1。

【3. 加速器设计探索】

本节首先提供了我们的加速器结构概览,介绍了FPGA平台上的几个设计挑战。为了克服这些挑战,我们提出了相应的优化技术。

3.1 设计概览

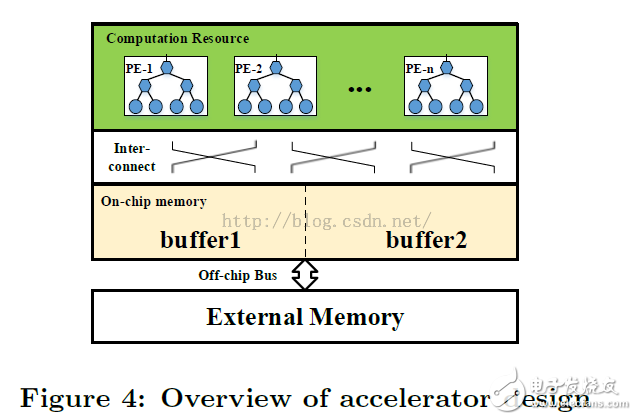

如图4所示,一个CNN加速器设计包括:处理单元(PE),片上缓存,外部存储器以及片内外互联。PE是卷积的基本计算单元。用于处理的所有数据放在外部存储器。由于片上资源限制,数据首先缓存到片上buffer,之后送入PE。这里使用双缓冲将传输时间掩盖于计算时间。片上互联用于PE和片上缓冲的通信。

在FPGA平台上有这样几个设计挑战阻碍了高效的CNN加速器设计:首先,片上数据只有很小一部分,故循环分块(loop tiling)是必要的,不合适的循环分块可能降低数据重用和数据并行处理效率。

其次,PE和缓冲区组织及其互联应仔细考虑,这样能高效处理片上数据。第三,PE的数据处理吞吐应该匹配FPGA平台的片外访存带宽。

本节我们从Code1开始优化,提供了连续步骤获得最优处理效率。

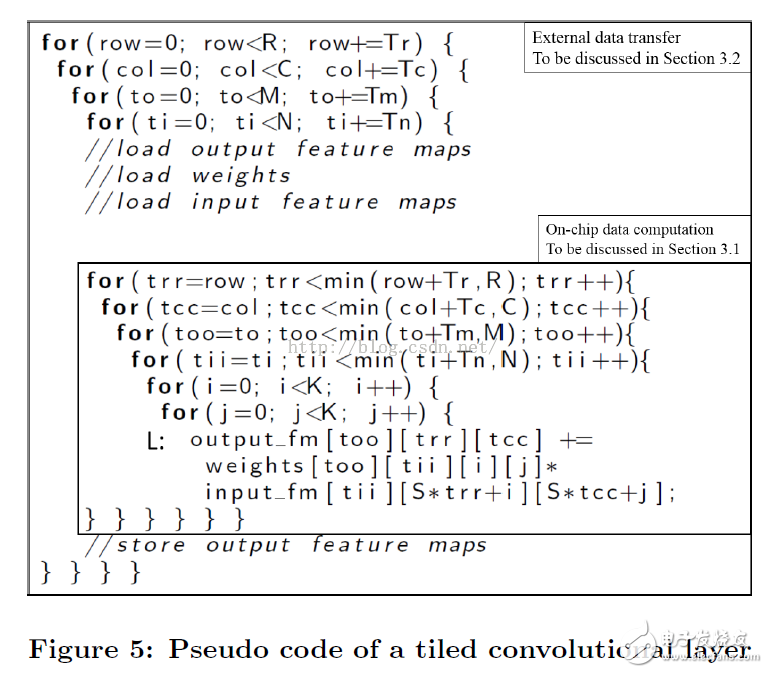

使用了循环分块的代码如下:

注意到循环变量i和j并未分块,因为CNN中卷积层kernel尺寸K太小(3~11)。

第二,我们讨论了计算引擎优化并将计算性能与分块系数建立联系。

第三,我们使用数据重用技术减少外存访问,建立了计算-访存比和分块系数的联系;

第四,利用上述两个变量,我们定义了设计空间,在FPGA平台上找最优解;

第五,我们讨论了怎样为多层CNN应用选择最好的加速器。

电子发烧友App

电子发烧友App

评论