摘要: 随着集成电路设计技术的发展和芯片集成度的提高,验证已经成为芯片设计流程中的主要瓶颈。本文设计了一个基于FPGA的智能卡验证平台,并对验证方法做了详细阐述。本文对于双界面智能卡芯片验证的成功实践,不仅是对FPGA验证理论的证实,而且验证的思路和方法对其他芯片有一定的指导意义。

引言

随着EDA技术和半导体制造工艺的不断发展,单芯片的功能越来越强,结构越来越复杂,设计和制造成本也大幅增加。尤其是进入90 nm后,芯片总体设计成本增加了20%左右,即使采用130 nm工艺,单次芯片制造的成本也在数十万美元,这使得验证工作在整个设计过程中的作用显得越来越重要。验证贯穿集成电路设计整个过程,从制定系统SPEC,验证工作就已经开始,从架构设计、行为级的系统建模到模块化的设计和实现,再到生成网表和后端布局、布线等一系列过程中,验证工作都一直伴随其中,通过各个阶段的验证,可以避免把上一个阶段的问题带到下一个阶段。

如今,整个集成电路行业逐步形成了IC设计、芯片制造、芯片封装三大行业。在IC设计行业中,设计和验证领域发展不均衡,验证技术的发展水平要远远落后于设计的发展水平。对于验证,传统方法是通过软件仿真来达到验证设计的目的,但由于软件仿真速度和仿真模型的局限性,当芯片复杂度和规模达到一定程度时,验证往往难以达到令人满意的效果。特别是对于模拟前端验证,由于仿真模型的局限性导致仿真结果与实际器件的工作情况不一致,往往难以保证所设计电路的可靠性。

为了克服现有的验证方法在效率和可靠性上面的不足,本文提供一个新型验证平台。一方面,该验证平台能够实现智能卡芯片设计中的硬件模块,让软件可以在真正的硬件环境中高速运行,从而在功能上验证设计的可行性;另一方面,该验证平台可以直接与MP300 TCL2型非接触式智能卡测试仪以及各类读卡器进行通信,在不同的通信环境下,通过调整验证平台本身的性能参数,可以找到最优的工作模式,从而对设计上性能的改善提供参考依据。

1 验证平台的设计方案

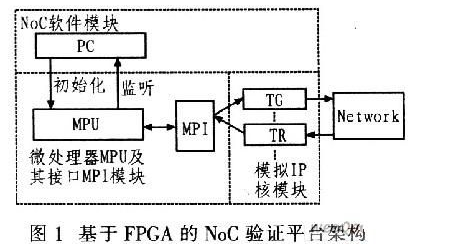

基于FPGA的智能卡验证平台总体设计方案如图1所示。本验证平台主要由可调线圈、模拟前端部件、数字逻辑部件和存储器部件4部分构成。其中可调线圈是模拟前端获取能量和信号的通道,模拟前端对信号进行调制和解调,同时为数字部分和存储器提供能量,数字逻辑部分完成信号的处理,存储器则对系统软件和用户数据进行储存。本验证平台实现了非接触式智能卡应有的基本功能,可以直接与市面上读卡器进行通信,通过测试通信过程中验证平台上的模拟或数字信号,可以达到验证设计方案是否合理的目的。

图1 智能卡验证平台的总体设计方案

1.1 可调线圈的设计

可调线圈的感应线圈部分是由非接触式智能卡卡基制作而成,其电感值为2.1 μH;然后与感应线圈并联一个SG1036ND型可调电容,其电容值从0.9~30 pF可调,由谐振频率计算公式:ω=1/L×C可知,在电感不变的情况下,通过改变谐振电路中的电容值可以相应地改变谐振电路的谐振频率;最后与感应线圈串联一个3296W-101型可调电阻,其阻值从0~100 Ω可调,由品质因数(Q值)计算公式:Q=(1/G)C/L可知,通过改变谐振电路中的电阻可以相应地改变谐振电路的Q值。可调线圈的结构如图2所示。

图2 可调线圈的结构

由上所述,本验证平台的可调线圈可以实现非接触式智能卡谐振频率和Q值的灵活调节。

1.2 模拟前端部件的设计

模拟前端部件由LDO芯片AMS11173.3和AMS11171.8、天线接口、与数字逻辑交互的接口以及模拟前端芯片BES2416C组成。模拟前端部件的主要功能是验证智能卡芯片内的模拟部分,为了保证每一部分电路都能得到有效的验证,BES2416C内部的大部分电路构成与智能卡芯片保持一致,包括整流电路、限流电路、时钟提取电路、锁相环、基准电压产生电路、上电复位电路、调制电路和解调电路。模拟前端芯片与智能卡不同之处在于智能卡受封装的限制只能封出接触式的Vcc、RST、CLK、GND、DATA 五个信号,而模拟前端芯片BES2416C为64引脚封装,模拟与数字交互的信号以及表征上述模拟各部分电路工作状态的信号都通过引脚拉出到芯片外部,因此可以通过测量上述信号实时监测模拟前端各部分电路的工作状态,通过这种手段可以帮助设计者找出所设计电路的最佳的工作模式并将此模式设计到智能卡芯片中。

1.3 数字逻辑部件的设计

数字逻辑部件由Xilinx公司的XC5VLX110型FPGA芯片、与模拟前端交互的接口、与存储器交互的接口组成。数字逻辑部件的主要功能是验证智能卡芯片内的数字部分,本文采用基于FPGA的快速系统原型验证,这种验证方法的本质在于能够快速地实现智能卡芯片设计中的数字逻辑部分的硬件模块,让软件模块在真正的硬件环境中高速运行,从而实现设计的软硬件协同验证。由于智能卡芯片采用低功耗设计,使用了较多的门控时钟,因此本文选择了一款具有较多全局时钟网络的FPGA芯片,该FPGA包含110 000个逻辑单元,32个全局时钟网络、1 200个用户I/O、16.4 Mb块存储区。由于FPGA最大特点就是具有静态可编程的特性或在线动态重构特性,使硬件的功能同软件一样可以通过编程来修改,因此本验证平台不仅可以验证已经设计完成的数字逻辑,还可以对设计过程中数字逻辑的改动部分进行实时验证。

1.4 存储器部件的设计

存储器部件是由LDO芯片AMS11173.3和AMS11171.8、容量为64 Kb的Eflash芯片BES2416B_E、与数字逻辑交互的接口组成。存储器部件的主要功能是验证智能卡芯片内的Eflash部分,本文使用的Eflash芯片内部的IP核与智能卡芯片保持一致,并且为64引脚封装,所有地址总线、数据总线和控制信号都通过引脚拉出到芯片外部,可以利用FPGA内的数字逻辑控制其读、擦、写操作,因此该芯片不仅能够作为存储器存储片内操作系统和数据,还可以直观验证智能卡内数字逻辑对Eflash的控制时序是否正确。

2 验证方法

验证方法分为功能验证和性能验证两个部分,下面详细阐述本平台的验证方法。

2.1 功能验证

验证平台与读卡器通信的前两步的数字逻辑是在FPGA中实现的,如果读卡器第一步发出寻卡请求信号,验证平台能够应答,并且读卡器在第二步能够成功选卡,说明验证平台的接收和发射功能正常,反之可以按照通信过程中各模块的工作顺序测试各部件测试点上的信号定位出有问题的模块。

进一步验证对Eflash的擦写功能,读卡器向验证平台分别发送读、擦、写Eflash的指令,如果验证平台给读卡器回复操作成功的信号,说明Eflash功能正常,反之需要测试存储器部件测试点上的信号找出对Eflash操作中时序出现的问题,然后修改代码在FPGA中重新实现数字逻辑。

利用读卡器向Eflash芯片中写入符合PBOC2.0标准的片内操作系统,使验证平台支持电子钱包和电子存折功能,如果验证平台能够成功完成PBOC2.0规定的圈存、圈提、消费、取余额等所有功能,说明验证平台的交易功能正常。

综上,如果通过以上三步验证,能够说明所设计智能卡芯片在功能上是正常的。

2.2 性能验证

谐振频率和Q值的调节:ISO/IEC 14443协议规定了非接触式智能卡通信用载波频率为13.56下MHz±7 KHz,但对智能卡本身的谐振频率并未规定标准值,因此,客观上造成了目前流通的智能卡谐振频率的多样性。通过测试发现,智能卡在不同谐振频率下的工作性能是不同的,每家智能卡厂商的芯片都有自己的最佳工作频率范围,但单纯通过理论分析无法定位这个区域,而本验证平台可以通过调节可调线圈上的可调电容改变验证平台的谐振频率,因此可以在不同的谐振频率下与读卡器进行通信找出智能卡芯片工作的最佳谐振频率;同理通过调节可调线圈上的可调电阻改变验证平台的Q值可以找出最有利于智能卡芯片工作的Q值。

工作场强范围的验证:ISO/IEC 14443 TypeA协议规定非接触式智能卡应在1.5~7.5 A/m的场强范围内正常工作。本验证平台可以与MP300 TCL2型非接触式智能卡测试仪器正常通信,首先将可调线圈置于TCL2的测试架上并调节TCL2发射的磁场强度到1.5 A/m,然后按照功能验证的步骤进行测试,如果通过验证说明智能卡在1.5 A/m场强下的功能正常,再调节场强到1.6 A/m进行同样的验证,按照以上方法将验证平台从1.5~7.5 A/m工作的情况做出统计,然后对验证平台通信不正常的场强区域进行详细测试,按照通信过程中各模块的工作顺序测试各部件测试点上的信号定位出有问题的模块并改进该模块的设计,然后重复本验证过程直到所有场强点都可以正常工作,最后将通过验证的电路结构设计到智能卡中。

接收性能的验证:ISO/IEC 14443 TypeA协议规定读卡器发出的信号为100% ASK调制,读卡器发送的数据0用pause表示,pause的波形由4个参数t1、t2、t3、t4决定,并且给出了这4个参数的取值范围。根据测试经验可知,智能卡的接收性能由t1和t2的决定,并且在t1和t2为两种极限的情况下智能卡接收最困难,这两种极限情况分别是:t1=3 μs、t2=0.5 μs以及t1=2 μs、t2=0.7 μs。首先将可调线圈置于TCL2的测试架上并调节TCL2发送的pause波形到一种极限情况,然后按照功能验证的步骤进行测试,如果通过验证说明智能卡在这种极限情况下的接收性能良好,再调节pause波形到另一种极限情况进行相同的验证,如果验证平台在任意一种情况下不能正常通信,则配置模拟前端芯片内解调电路解调阈值调节的控制字,然后重新进行接收性能的验证,如此反复直到验证平台在两种极限pause波形下正常工作,最后将通过验证的解调电路的工作模式设计到智能卡中。

发送性能的验证:ISO/IEC 14443 TypeA协议规定智能卡发送的负载波调制深度应至少达到22/H0.5 mV。首先将可调线圈置于TCL2的测试架上并调节TCL2发射的磁场强度到1.5 A/m,然后利用TCL2的ISO 103736测试脚本计算出在当前场强下的负载调制深度并与协议要求值进行比较,如果满足要求则说明智能卡的负载调制深度在当前场强下发送性能良好,再调节场强到2.0 A/m进行同样的验证,按照以上方法将验证平台从1.5~7.5 A/m的负载调制深度做出统计,如果负载调制深度在某些场强下不满足协议要求,则配置模拟前端芯片内调制电路负载调制深度的控制字,然后重新进行发送性能的验证,如此反复直到验证平台的负载调制深度在各场强点上都满足协议要求,最后将通过验证的调制电路的工作模式设计到智能卡中。

Eflash操作时间的验证:TBIT是标志本验证平台的Eflash芯片操作状态的信号,TBIT信号为高表示正在操作,TBIT信号为低表示操作完成。对Eflash的操作包括读、擦、写三个动作,下面对这三个操作的时间分别进行验证:首先将可调线圈置于读卡器线圈上并将示波器的一个通道接到TBIT信号测试点上,然后读卡器向验证平台发送读取Eflash中1字节的指令,通过示波器抓取TBIT信号高电平的持续时间,这段时间就是Eflash读取1字节的时间;读卡器向验证平台发送擦除Eflash中1页的指令,通过示波器抓取TBIT信号高电平持续的时间,这段时间就是Eflash擦除1页的时间;读卡器向验证平台发送向Eflash写入1字节的指令,通过示波器抓取TBIT信号高电平持续的时间,这段时间就是Eflash写入1字节的时间。经过以上对Eflash操作时间的验证,可以使研发人员精确地计算出智能卡与读卡器交互过程中硬件操作需要的时间,用这个时间和实际智能卡操作时间作对比来评估片内操作系统的效率,为软件性能的改善提供参考依据。

综上这些验证方法可以帮助研发人员及时发现芯片设计中的不足,以便在流片前做出改进,提高智能卡芯片开发的成功率。

结语

本平台可以适用于其他通信芯片的设计验证中,具有很好的工程应用价值。

参考文献

[1] 黄丽. 百万门级专用集成电路的FPGA验证[D]. 西安:西安电子科技大学,2007:16.

[2] 傅永杰. 关于FPGA在ASIC设计中的作用问题探讨[J]. 今日电子,1996(2).

[3] 全国金融标准化技术委员会. 中国金融集成电路(IC)卡规范第二部分:电子钱包/电子存折应用规范[M]. 北京: 中国金融出版社, 2010: 1938.

[4] 周宏华,李树国,周润德. 高安全性的智能卡芯片结构与设计[J]. 清华大学学报, 2003,43(4).

[5] Xilinx. Virtex5 FPGA User Guide. , 2009: 2536.

[6] Akihiro Higashi, Kazuhide Tamaki, Takayuki Sasaki.Verification Methodology for a Complex SystemonaChip[J]. FUJITSU Sci. Tech. J.,2000(6):2430.

陈博(硕士生),主要研究方向为芯片验证、测试和嵌入式系统设计;于忠臣(教授),主要研究方向为SoC设计和嵌入式系统。

电子发烧友App

电子发烧友App

评论