设计来满足各种约束 用不用的指令来探索多个HLS解决方案 2.实验内容 实验中文件中包含一个矩阵乘法器的实现,实现两个矩阵inA和inB相乘得出结果,并且提供了一个包含了计算结果的testbench

2020-12-21 16:27:21 3153

3153 的Zynq 7000, 找了一个HLS的教程,就开始了如下入门实验,体验高级语言综合设计IP。Vivado HLS是Xilinx 推出的高层次综合工具,采用C/C++语言进行FPGA设计。HLS提供了一些

2020-10-14 15:17:19 2881

2881

WebPACK许可证PetaLinux工具许可证Vivado HLS评估许可证哪个许可证支持Vivado RTL合成/实现/写入比特流?2)基于激活的许可证显示为灰色。我无法访问它们?我该怎么办才能获得30天

2018-12-06 11:31:19

像素访问对应方法2.3 用HLS实现OpenCV应用的实例(快速角点滤波器image_filter)我们通过快速角点的例子,说明通常用VivadoHLS实现OpenCV的流程。首先,开发

2021-07-08 08:30:00

)配合优化综合的视频库和Vivado IP集成器,为一个特定的视频应用打造一个定制化的加速器。该设计流程可以在兼具高性能和低功耗的条件下快速地实现许多计算机视觉算法。此设计流程还可以让设计人员能够在

2013-12-30 16:09:34

我在Vivado HLS中有以下错误的合成。我试图更新许可证文件但没有成功。请给我一个建议。@E [HLS-72]许可证签出不成功。确保可以访问许可证或通过环境变量指定适当的许可证。 执行

2020-05-20 09:13:21

1.实验目的通过例程探索Vivado HLS设计流用图形用户界面和TCL脚本两种方式创建Vivado HLS项目用各种HLS指令综合接口优化Vivado HLS设计来满足各种约束用不用的指令来探索

2021-11-11 07:09:49

,着力于解决大数据处理、人工智能等复杂高性能算法处理。新的设计工具的推出,vivado HLS,更加注重嵌入式系统的系统级建模,通过HLS工具,用户只需要编写C语言代码,就可以让工具自动转换和生成HDL代码。随着异构架构和片上系统技术的不断发展,协同设计、协同仿真和协同调试将成为未来嵌入...

2021-11-09 06:43:27

本帖最后由 FindSpace博客 于 2017-4-19 16:57 编辑

在c simulation时,如果使用gcc编译器报错:/home/find/d/fpga/Vivado_HLS

2017-04-19 16:56:06

vivado可以正常使用,但是HLS总是出现图片中的错误。请问该如何解决?谢谢!

2020-08-12 01:36:19

你好!如果我想使用vivado hls来合成具有axi流接口的代码,是否有必须遵循的标准编码风格?

2020-04-21 10:23:47

,int b);最后经过编译可以生成VHDL等硬件描述文件与IP核文件.我想调用自己写的IP核(add函数)我在vivado 中添加了自定义IP核与PS(处理系统)我知道网上说用AXI Steam? 来连接

2016-01-28 18:40:28

,int b);最后经过编译可以生成VHDL等硬件描述文件与IP核文件.我想调用自己写的IP核(add函数)我在vivado 中添加了自定义IP核与PS(处理系统)我知道网上说用AXI Steam? 来连接

2016-01-28 18:39:13

大家好我可以在Matlabwith Vivado上安装Xilinxsystem生成器吗?有了ISE,有一个应用程序调用System Generator Matlab Configuration

2018-12-27 10:57:02

设计一个高性能的HLS, 可以用任何优化策略,在保持函数功能的同时尽可能提高性能。希望论坛里的大神给予具体优化的指导,最近几天调试太费劲了,希望大神给予保罗loop unroll, pipeline

2016-08-27 21:11:26

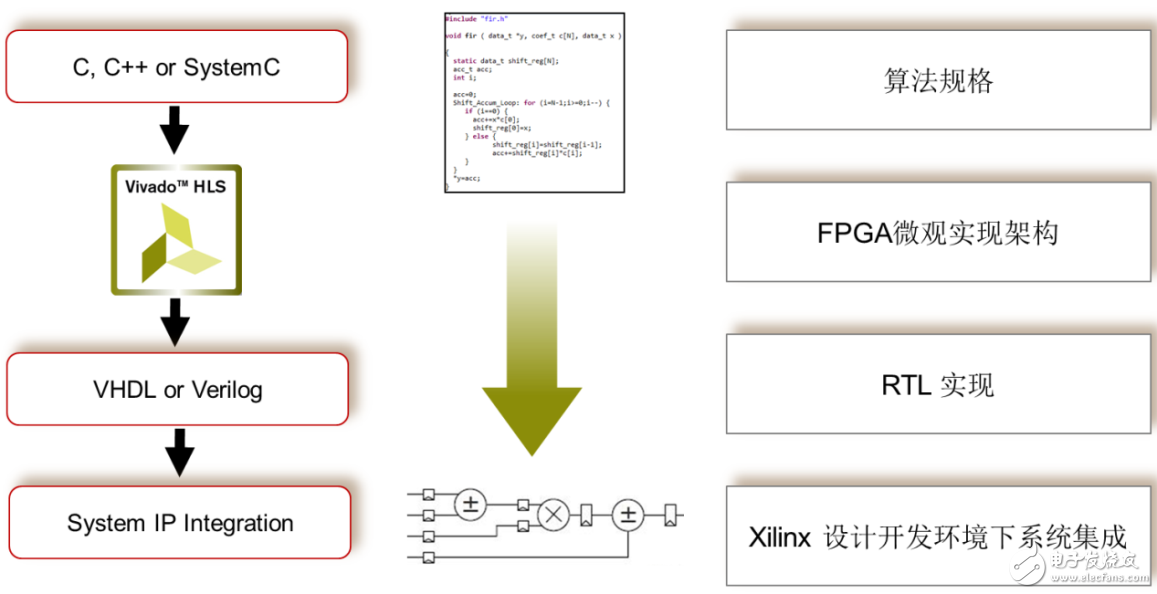

,找到了计算强度最大的部分,HLS工具就能帮助您加速这些函数,同时仍能继续使用C++编写。Vivado HLS用C、C++或SystemC代码生成高效的RTL实现方案。 此外,以IP为中心

2014-04-21 15:49:33

各位大侠 最近看到一段矩阵分解程序但不知是用的什么分解算法 有点像UD分解 最后输出上三角阵 但不确定求助大侠指点 谢谢void factor(Matrix* P_){// ne pas v

2015-05-14 09:25:46

1、HLS最全知识库介绍高层次综合(High-level Synthesis)简称HLS,指的是将高层次语言描述的逻辑结构,自动转换成低抽象级语言描述的电路模型的过程。对于AMD Xilinx而言

2022-09-07 15:21:54

,基于FPGA的矩阵乘法加速器,运算效率可以比通用CPU提高一个数量级以上,非常适合大规模科学计算和深度学习应用。

本文主旨

通过Xilinx Vitis HLS设计一个高效矩阵乘法kernel

2023-10-13 20:11:51

主要可以从“设计的重用”和“抽象层级的提升”这两个方面来考虑。Xilinx推出的Vivado HLS工具可以直接使用C、C++或System C来对Xilinx系列的FPGA进行编程,从而提高抽象的层级

2020-10-10 16:44:42

【资料分享】Vivado HLS学习资料

2013-11-02 11:21:14

Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后为了统一将HLS集成到Vitis里了,集成之后增加了一些功能,同时将这部分开源出来了。Vitis

2022-09-09 16:45:27

请问一下Xilinx公司发布的vivado具体的作用是什么,刚刚接触到,以前一直用quartus ii,没有使用过ise,后来今天听说了vivado,不知道是做什么用的,希望大家都能参与讨论中,谢谢。

2015-04-15 16:51:00

嗨,大家好,我有一个问题,在VIVADO HLS 2017.1中运行C \ RTL协同仿真。我已成功运行2014和2016版本的代码。任何人都可以告诉我为什么报告NA仅用于间隔

2020-05-22 15:59:30

Vivado 2017.4、Xilinx VivadoHLS 2017.4、Xilinx SDK 2017.4。Xilinx Vivado HLS(High-Level Synthesis,高层次综合)工具支持

2021-02-19 18:36:48

你好,我使用Vivado HLS生成了一个IP。从HLS测量的执行和测量的执行时间实际上显着不同。由HLS计算的执行非常小(0.14 ms),但是当我使用AXI计时器在真实场景中测量它时,显示3.20 ms。为什么会有这么多差异? HLS没有告诉实际执行时间?等待回复。问候

2020-05-05 08:01:29

嗨,我是HLS的新手,想要将opencv用于zynq-7000。我有两个主要问题:1)一旦我可以从xx1167运行Video_Library_Windows.bat但现在我收到以下错误:我还更改

2020-03-26 07:59:19

案例的使用说明,适用开发环境: Windows 7/10 64bit、Xilinx Vivado2017.4 、Xilinx Vivado HLS 2017.4 、Xilinx SDK 2017.4

2023-01-01 23:52:54

案例的使用说明,适用开发环境: Windows 7/10 64bit、Xilinx Vivado2017.4 、Xilinx Vivado HLS 2017.4 、Xilinx SDK 2017.4

2023-08-24 14:40:42

Vivado2017.4 、Xilinx Vivado HLS 2017.4 、Xilinx SDK 2017.4。

Xilinx Vivado HLS (High-Level Synthesis

2023-08-24 14:52:17

Vivado2017.4 、Xilinx Vivado HLS 2017.4 、Xilinx SDK 2017.4。Xilinx Vivado HLS (High-Level Synthesis,高层次

2023-01-01 23:50:04

7/10 64bit、Xilinx Vivado2017.4 、Xilinx Vivado HLS 2017.4 、Xilinx SDK 2017.4。Xilinx Vivado HLS

2023-01-01 23:46:20

7/10 64bit、Xilinx Vivado2017.4 、Xilinx Vivado HLS 2017.4 、Xilinx SDK 2017.4。Xilinx Vivado HLS

2023-08-24 14:54:01

前 言本文主要介绍HLS案例的使用说明,适用开发环境:Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx Vivado HLS 2017.4、Xilinx

2021-11-11 09:38:32

前 言本文主要介绍HLS案例的使用说明,适用开发环境:Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx Vivado HLS 2017.4、Xilinx

2021-11-11 16:02:09

的经验几乎为0,因此我想就如何解决这个问题提出建议。这就是我的想法:1 - 首先,用Vivado HLS转换VHDL中的C代码(我现在有一些经验)2 - 在Vivado HLS中生成IP核(如果我

2020-03-24 08:37:03

你好我正在尝试在vivado HLS中创建一个IP,然后在vivado中使用它每次我运行Export RTL我收到了这个警告警告:[Common 17-204]您的XILINX环境变量未定义。您将

2020-04-03 08:48:23

completly提到xilinx hls网站上提到。请帮助我从过去三天起因为这个问题我无法工作。vivado_HLS_problem.docx 2610 KB

2020-04-09 06:00:49

我照着xapp1167文档,用HLS实现fast_corners的opencv算法,并生成IP。然后想把这个算法塞到第三季的CH05_AXI_DMA_OV5640_HDMI上,这个demo里

2017-01-16 09:22:25

您好我有一个关于vivado hls的问题。RTL是否来自xivix FPGA的vivado hls onyl?我们可以在Design Compiler上使用它进行综合吗?谢谢

2020-04-13 09:12:32

您好Xilinx的用户和员工,我们正在考虑购买Zynq 7000用于机器视觉任务。我们没有编程FPGA的经验,并希望使用Vivado HLS来指导和加速我们的工作。关于这种方法的一些问题:您对

2020-03-25 09:04:39

你好,我有一个与switch语句的合成有关的问题。我开始使用Vivado HLS并且我已经创建了一个小的file.cpp,仅用于学习,但是当Vivado HLS合成文件时,我没有得到任何开关语句

2019-11-05 08:21:53

请问Vivado HLS出现这种情况是什么原因呢

2021-06-23 06:13:13

Vivado HLS设计流程是怎样的?

2021-06-17 10:33:59

嗨伙计,在我的PC Vivado设计套件2015.2和SDK 2015.2工作,但只有vivado HLS 2015.2没有打开,这就是为什么我想重新安装Vivado HLS 2015.2。如何下载

2018-12-27 10:57:49

非负矩阵分解(Nonnegative Matrix Factorization,NMF)是一种新近被提出的方法,它以非线性的方式实现对非负多元数据的纯加性、局部化、线性和低维描述。NMF 可使数据中的潜在结构、特征

2009-11-24 15:55:29 13

13 Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高层次综合 (HLS) 进行 FPGA 设计的简介

2016-01-06 11:32:55 65

65 testbench来验证设计。 Integrate带有Xilinx IP Block的 HLS IP 这里展示了在IP Integrator中,如何将两个HLS IP blocks跟Xilinx IP FFT结合在一起 ,并且在Vivado中验证设计。

2017-02-07 17:59:29 4179

4179

应用Vivado HLS IP 这里集成了HLS IP和由HLS创建的软件驱动,目的是控制在Zynq器件上实现的IP设计。

2017-02-07 18:08:11 3207

3207

HLS非常适合一些信号处理模块的快速实现。下面是一个实际的例子,由于使用了HLS,非常高效的就完成了模块的rtl的实现,比用手工coding节约了大量的时间! 需求描述: 在一个项目里面,需要快速

2017-02-08 02:33:36 623

623

,Xilinx Vivado HLS是一个高级综合工具,能够将C语言转换成硬件描述语言(HDL),也就是说我们可以用C语言来实现HDL模块编程了。 图1 Vivado HLS工作流程 第一位Hacker

2017-02-08 20:01:59 550

550

大,我是否能够利用Vivado HLS完成这项要求较高的运算呢? 我开始从软件方面考虑这个转换,我开始关注软件界面。毕竟,HLS创建专用于处理硬件接口的硬件。幸好Vivado HLS支持创建AXI slave的想法,同时工作量较少。 我发现Vivado HLS编码限制相当合理。它支持大多数C + +语言

2017-02-09 02:15:11 310

310 本实验练习使用的设计是实验1并对它进行优化。 步骤1:创建新项目 1.打开Vivado HLS 命令提示符 a.在windows系统中,采用Start>All Programs>Xilinx

2017-02-09 05:07:11 411

411

在使用高层次综合,创造高质量的RTL设计时,一个重要部分就是对C代码进行优化。Vivado Hls总是试图最小化loop和function的latency,为了实现这一点,它在loop

2017-11-16 14:44:58 3362

3362 接口(ORI)标准压缩算法可以分析其对信号保真度,延迟以及实现成本。Vivado HLS是一个评估实现压缩算法非常高效的软件平台。 无线数据带宽的增长使得新一代的网络要具备新的能力,例如更高阶MIMO

2017-11-17 02:25:41 1267

1267

如果您正在努力开发计算内核,而且采用常规内存访问模式,并且循环迭代间的并行性比较容易提取,这时,Vivado® 设计套件高层次综合(HLS) 工具是创建高性能加速器的极好资源。通过向C 语言高级算法描述中添加一些编译指示,就可以在赛灵思FPGA 上快速实现高吞吐量的处理引擎。

2017-11-17 18:12:01 1647

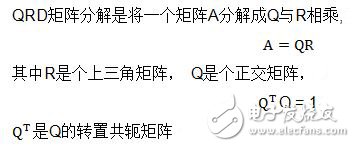

1647 浮点具有更大的数据动态范围,从而在很多算法中只需要一种数据类型的优势。本文介绍如何使用Vivado HLS实现浮点复数矩阵分解。使用HLS可以快速,高效地实现各种矩阵分解算法,极大地提高生产效率, 降低开发者的算法FPGA实现难度。

2017-11-18 12:00:11 852

852

1 Vivado HLS简介 2创建一个Vivado-HLS工程 2.1打开Vivado HLS GUI 2.2创建新工程 在 Welcome Page, 选择Create New Project

2017-12-04 10:07:17 0

0 (包括奇异值分解(SVD)和非负矩阵分解(NMF))的推荐算法、奇异值分解推荐算法以及因子分解机推荐算法进行手机App推荐。实验表明,因子分解机算法取得了较好的推荐效果。这说明因子分解机在手机应用推荐的场景中可以更好地描述用户

2017-12-22 16:43:00 0

0 在实际工程中,如何利用好这一工具仍值得考究。本文将介绍使用Vivado HLS时的几个误区。

2018-01-10 14:33:02 19813

19813

的数据动态范围,从而在很多算法中只需要一种数据类型的优势。Xilinx Vivado HLS工具支持C/C++ IEEE-54标准单精度及双精度浮点数据类型,可以比较容易,快速地将C/C++ Floating-Point算法转成RTL代码。

2018-01-12 05:43:54 9950

9950 本文内容介绍了基于用Vivado-HLS为软件提速,供参考

2018-03-26 16:09:10 7

7 Vivado HLS 是 Xilinx 提供的一个工具,是 Vivado Design Suite 的一部分,能把基于 C 的设计 (C、C++ 或 SystemC)转换成在 Xilinx 全可编程芯片上实现用的 RTL 设计文件 (VHDL/Verilog 或 SystemC)。

2018-06-05 10:31:00 6326

6326

Vivado HLS是Xilinx公司推出的加速数字系统设计开发工具,直接使用C、C++或SystemC开发的高层描述来综合数字硬件,替代用VHDL或Verilog实现FPGA硬件设计[6],实现设计的功能和硬件分离,不需要关心低层次具体细节,具有很强的灵活性,有效降低数字系统设计开发周期。

2018-10-04 10:41:00 7096

7096

了解如何使用GUI界面创建Vivado HLS项目,编译和执行C,C ++或SystemC算法,将C设计合成到RTL实现,查看报告并了解输出文件。

2018-11-20 06:09:00 3651

3651 了解如何使用Tcl命令语言以批处理模式运行Vivado HLS并提高工作效率。

该视频演示了如何从现有的Vivado HLS设计轻松创建新的Tcl批处理脚本。

2018-11-20 06:06:00 2887

2887 Vivado HLS有助于降低整体系统功耗,降低材料成本,提高系统性能并加快设计生产率。

我们将向您展示如何使用C,C ++或SystemC创建更高效的规范。

2018-11-27 06:43:00 3392

3392 了解如何使用Vivado设计套件的电路板感知功能快速配置和实施针对Xilinx评估板的设计。

2018-11-26 06:03:00 3062

3062 空间调制(SM) 系统中性能最优的最大似然( ML)检测算法复杂度很高,用基于信道矩阵QR分解的M算法(QRD-M)可以降低复杂度,但传统QRD-M算法检测时,每层都保留固定的M个节点,仍会造成额外的计算量。

2018-12-11 11:36:14 2

2 尽管 Vivado HLS支持C、C++和System C,但支持力度是不一样的。在v2017.4版本ug871 第56页有如下描述。可见,当设计中如果使用到任意精度的数据类型时,采用C++ 和System C 是可以使用Vivado HLS的调试环境的,但是C 描述的算法却是不可以的。

2019-07-29 11:07:16 5072

5072

介绍了如何利用Vivado HLS生成FIR滤波算法的HDL代码,并将代码添加到ISE工程中,经过综合实现布局布线等操作后生成FPGA配置文件,下载到FPGA开发板中,Darren采用的目标板卡是Spartan-3 FPGA。

2019-07-30 17:04:24 4554

4554 接着开始正文。据观察,HLS的发展呈现愈演愈烈的趋势,随着Xilinx Vivado HLS的推出,intel也快马加鞭的推出了其HLS工具。HLS可以在一定程度上降低FPGA的入门门槛(不用编写

2019-07-31 09:45:17 6232

6232

在Vitis HLS下,一个Solution的Flow Target可以是Vivado IP Flow Target,也可以是VitisKernel Flow Target,如下图所示。前者最终导出来

2020-11-05 17:43:16 37066

37066 本文介绍如何一步一步将设计从SDSoC/Vivado HLS迁移到Vitis平台。

2022-07-25 17:45:48 3058

3058

本文介绍如何一步一步将设计从SDSoC/Vivado HLS迁移到Vitis平台。

2021-01-31 08:12:02 8

8 基本的非负矩阵分解应用于图像聚类时,对异常点的处理不够鲁棒,稀疏性较差。为了提高分解后的矩阵的稀疏性在基本的非负矩阵分解算法中引入了L,范数,对基本的非负矩阵分解模型进行了改进,从而实现稀疏性,提升

2021-05-08 16:06:54 7

7 多个HLS解决方案2.实验内容实验中文件中包含一个矩阵乘法器的实现,实现两个矩阵inA和inB相乘得出结果,并且提供了一个包含了计算结果的testbench文件来与所得结果进行对比验证。...

2021-11-06 09:20:58 6

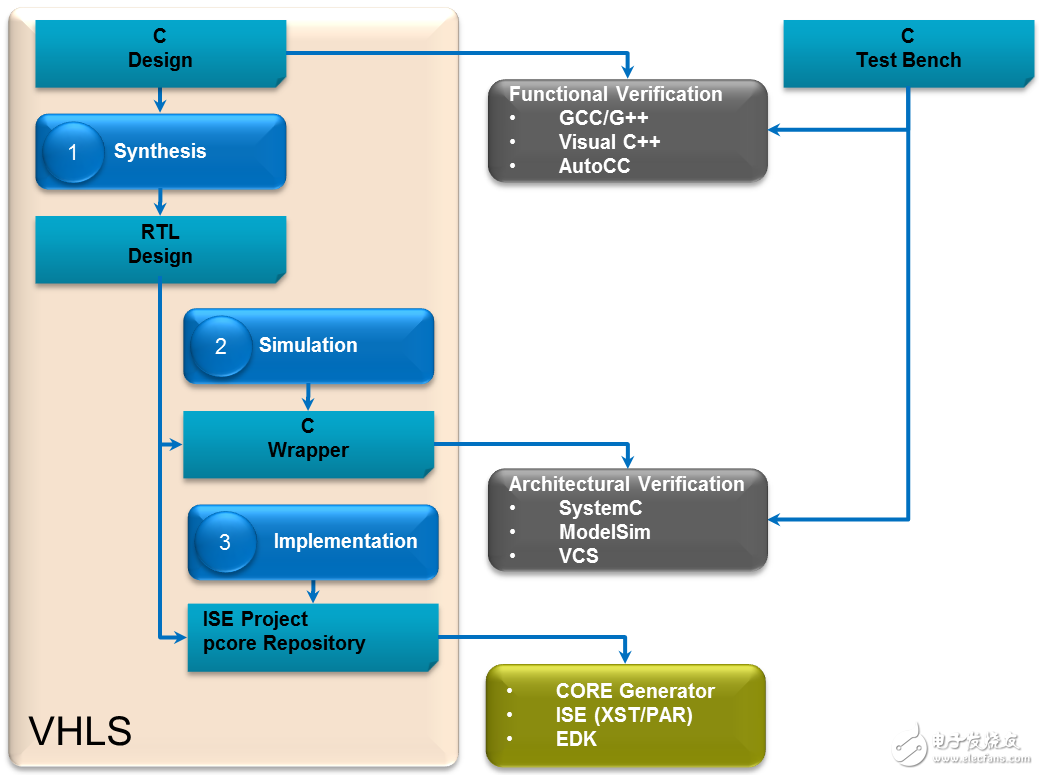

6 在整个流程中,用户先创建一个设计 C、C++ 或 SystemC 源代码,以及一个C的测试平台。通过 Vivado HLS Synthesis 运行设计,生成 RTL 设计,代码可以是 Verilog,也可以是 VHDL。

2022-06-02 09:48:17 6129

6129 HLS的FPGA开发方法是只抽象出可以在C/C++环境中轻松表达的应用部分。通过使用Vivado(Xilinx)或Intel(Quartus)工具,HLS工具流程基本上可用于任何BittWare板。

2022-08-02 09:18:32 1340

1340

对于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后为了统一将HLS集成到Vitis里了,集成之后增加了一些功能,同时将这部分开源出来了。Vitis HLS是Vitis AI重要组成部分,所以我们将重点介绍Vitis HLS。

2022-09-02 09:06:23 2857

2857 vivado本身集成了opencv库以及hls视频库了,opencv不能被综合导出为RTL电路,hls视频库的功能有所欠缺,因此引入xfopencv作为既可以被综合导出为RTL电路,也能够实现opencv丰富的功能。

2022-09-09 15:07:05 997

997 对于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后为了统一将HLS集成到Vitis里了,集成之后增加了一些功能,同时将这部分开源出来了。Vitis HLS是Vitis AI重要组成部分,所以我们将重点介绍Vitis HLS。

2023-01-15 11:27:49 1317

1317 是Vitis HLS。在Vivado 2020版本中替代原先的Vivado HLS, 功能略有差异。 HLS 的机理 简单地讲,HLS采样类似C语言来设计FPGA 逻辑。但是要实现这个目标,还是不容易

2023-01-15 12:10:04 2968

2968 今天推出Xilinx已发布的《Vivado使用误区与进阶》系列:用TCL定制Vivado设计实现流程。

2023-05-05 09:44:46 674

674

Xilinx平台的Vivado HLS 和 Vitis HLS 使用的 export_ip 命令会无法导出 IP

2023-07-07 14:14:57 338

338

)hls_fft.h。实际上,在HLS中调用该库实现FFT,其实是Vivado中的那个FFT核实现的,但是HLS中的配置和给定输入输出数据比较方便,并且对其外部封装其他类型的总线接口非常容易。

2023-07-11 10:05:35 580

580

电子发烧友网站提供《UltraFast Vivado HLS方法指南.pdf》资料免费下载

2023-09-13 11:23:19 0

0 电子发烧友网站提供《将VIVADO HLS设计移植到CATAPULT HLS平台.pdf》资料免费下载

2023-09-13 09:12:46 2

2 电子发烧友网站提供《使用Vivado高层次综合(HLS)进行FPGA设计的简介.pdf》资料免费下载

2023-11-16 09:33:36 0

0

正在加载...

电子发烧友App

电子发烧友App

评论