在使用Altium Designer绘制FPGA相关的电路原理图的过程中,我们会遇到这样的问题:FPGA和外围设备以及相互之间需要进行信号线相连,由于在大型系统之中,使用到的FPGA和相关芯片具有大量的引脚(很多情况下多达千根以上),在引脚分配和信号线相连的过程之后中,需考虑很多其他的问题,比如引脚的输入输出、差分和电平标准等特性,后期PCB布线时候的信号线是否交叉和长短,FPGA在连线过程中是否使用同一个Bank,Bank利用率与GC引脚的特性等。很多情况下设计步骤是先进行Verilog/VHDL逻辑设计,然而有的时候也需要先制作PCB板,再在此基础上进行开发。因此整个过程会因为考虑的因素众多以及管脚数量巨大而非常麻烦。

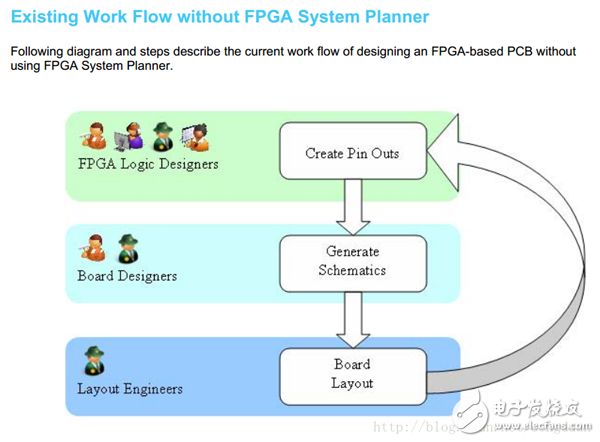

首先是FPGA的引脚分配问题。Xilinx公司的FPGA都有相关的Pinout and Package文档,介绍某种型号FPGA引脚的功能、分类、排布以及封装信息。但是工程师还是会遇到许多挑战,包括创建最初引脚分配、FPGA与原理图相结合、以及确保FPGA的合理布线。Cadence OrCAD FPGA SystemPlanner正是为了解决这类问题的工具,下面一段介绍摘自

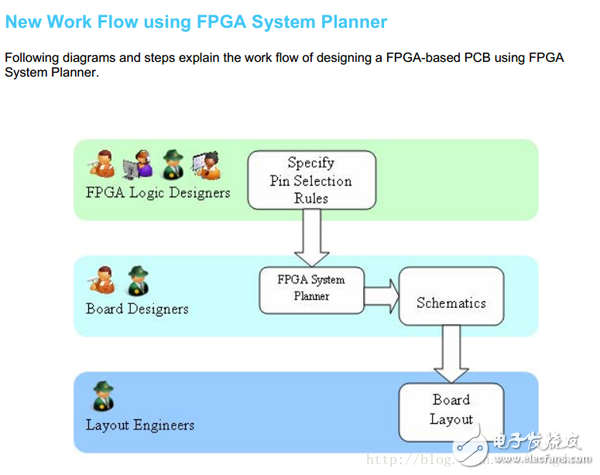

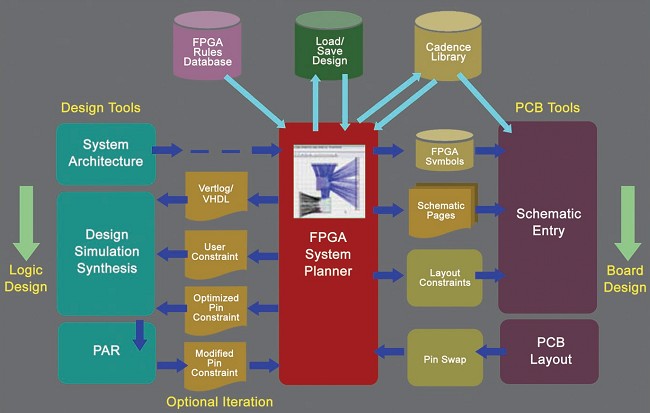

当工程师在PCB板上设计大规模引脚FPGA时,他们将遇到一些挑战:包括创建最初引脚分配、FPGA与原理图相结合、以及确保FPGA的合理布线。Cadence OrCAD FPGA SystemPlanner正是为了应对如此的挑战,该模块为FPGA和PCB的协同设计提供了一个完整的、并具有可扩展性的解决方案,它能使以创建最优“器件-规则-准确”为目标的引脚分配过程自动进行。使用自动引脚分配综合技术来代替以前容易出错的手动操作过程,就可通过这个独特的布局解决方案减少在PCB板设计过程当中出现的反复迭代次数,同时缩短了创建最优引脚分配所需要的时间。

在PCB板上进行大规模引脚的FPGA设计

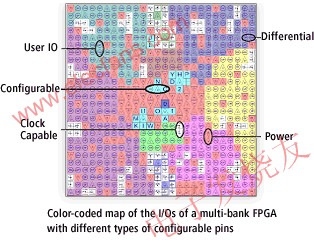

在PCB板上集成结构复杂的FPGA需要花费大量的时间,并且要延长设计周期,这些FPGA有很多不同种类的分配规则和需要用户配置的引脚,通常这些FPGA的引脚是用户通过手工操作一个挨着一个进行配置的,这些配置是在忽略PCB板上关键元件的摆放位置的情况下进行的,而这些关键元件恰恰是和FPGA相连接的。如果忽略以上操作给将来的PCB布线带来的影响,基于FPGA的设计工程将被迫面临两个困难的选择:非最优的引脚分配,这可能增加所设计的PCB板的叠层数;或者在设计周期的最后阶段要进行一些不必要的设计迭代。即使经过多次反复,这种较容易出错手动操作过程带来的后果仍然是不必要的PCB重复设计。

如果使用手动操作对FPGA的引脚进行分配,这将增加对FPGA进行引脚分配的时间,用户将不能在所提供的不同FPGA器件和其子系统当中使用的器件设计之间进行权衡,因为进行权衡意味着用户将同时处理两个不同工程,而他们两者之间并没有设计相互借鉴之处。

Cadence OrCADFPGA System Planner为FPGA和PCB之间的协同设计提供了一种全面的、可扩展的解决方案,它能使用户创建一个正确的、最优的引脚分配。FPGA的引脚分配是根据用户的指定、基于接口的连接(设计目标)、FPGA的引脚分配规则(FPGA规则)和FPGA在PCB板上的实际位置(相对位置)来进行自动综合的。自动引脚分配综合避免了用户在手动操作过程当中容易出现的错误,同时缩短了在PCB板上创建FPGA初始引脚分配的时间(关系到被摆放的FPGA的引脚分配综合),这种独特的、关系到摆放位置的引脚分配方法消除了在手动操作过程当中容易出现的不必要的设计反复。

OrCAD FPGA System Planner集成在了OrCAD Capture和OrCAD PCB Editor当中,它可以读取Capture当中的原理图和元器件符号。另外,它可使用OrCAD PCB Editor当中现有的封装库。如果FPGA在布线过程中的摆放位置发生了变化,可在OrCAD PCB Editor当中直接调用FPGA System Planner进行的引脚优化。

特点

OrCAD FPGASystem Planner技术

一个FPGA系统是整个PCB电路板设计下面的一个组成部分,其中包括其他和该FPGA相连接的一个或多个FPGA,以及其他的非FPGA元件。

传统的引脚分配方法是典型的基于手动操作的引脚分配,或者常常要依靠一个电子表格来进行引脚分配。这些工具要求用户在不考虑其他元器件的摆放位置,以及接口和信号线的可布线性的情况下进行引脚分配。首先,没有在线规则检查能确保为FPGA引脚指定的信号线分配到的引脚种类是正确的。这样做带来的后果是,用户要在基于电子表格的工具和FPGA厂商提供的工具之间要进行很多的重复操作。

这样做影响到了在当前电路板层上不能完成对FPGA引脚进行布线的PCB布线设计者和接受这些PCB布线设计者纸面上或者口头上引脚分配建议的FPGA设计者,在他们两者之间常常增加很多不必要的重复操作。一旦FPGA设计者改变了最初的引脚分配,硬件设计者就得在所设计的原理图当中改变其引脚分配。这些不必要的重复操作将使设计周期延长几周或者几天的时间,同时给设计团队成员增加了很多麻烦。由于是手动操作过程,未发现的错误很可能导致电路板必须重新制作,这是十分昂贵的。

虽然FPGA设计者、硬件设计者和PCB布线设计者可同时对引脚分配作自动更改,但是这样做没有解决导致这些重复操作的根本问题。引脚分配并非受以下的的三个因素所制约:FPGA资源可用性、FPGA供应商的引脚分配规则、以及FPGA在PCB板上的布线可行性——在设计进程的最后要进行很多的重复操作,从而延长了在PCB板上集成如今复杂的、大规模引脚FPGA所要花费的时间。

指定设计意图

OrCAD FPGA System Planner

使用FPGA器件库来帮助用户选择所要使用到的元器件。它可使用OrCAD PCB Editor的封装功能来查看FPGA的平面图,它可以使用户对FPGA系统元件进行快速布局。OrCAD FPGA System Planner能确定在FPGA子系统当中各元件的可连接性,这是在高层次所定义的接口中进行的。用户能创建诸如DDR2、DDR3、以及PCI总线的接口,这样做便可确定FPGA和内存DIMM模块之间的可连接性,以及两个FPGA之间的可连接性。OrCAD FPGA System Planner可以识别差分信号、电源信号、以及时钟信号。

FPGA器件规则

OrCAD FPGA System Planner

提供一个精确的FPGA模型器件库,元件库里模型符合由FPGA器件供应商指定的引脚分配规则和电气规则。这些FPGA模型可在综合引擎下面使用,这样做确保其严格遵守由FPGA供应商指定的电气使用规则。这些规则约束诸如时钟及时钟区域的选择、库的分配、SSO预算、利用缓冲区驱动、I/O标准电压基准水平等等。在综合过程中,OrCAD FPGA SystemPlanner自动检查数百个这样的规则,以确保FPGA的引脚得到准确和最佳的利用。

关系到摆放位置的引脚分配综合

OrCAD FPGA System Planner

向用户提供一种使用OrCAD PCB封装来创建FPGA系统摆放位置的方法,用户使用诸如DDRx、PCI Express、SATA、前端总线等等的接口在各元件之间以及各FPGA之间使用元件放置视角来确定其连接性,这些接口在设计当中和FPGA以及其他元件相连接,这样做缩短了用于确定FPGA系统设计方案的时间。

一旦确定了子系统当中FPGA和其他元器件的连接,OrCAD FPGA System Planner根据用户的设计意图、现有的FPGA资源、FPGA周围元器件的摆放位置、以及FPGA供应商的引脚分配规则来对FPGA的引脚分配进行综合。

OrCAD FPGA System Planner有一个内置的DRC引擎,它能结合由FPGA供应商提供的一些规则,比如引脚分配、参考电压和终端设备等。这些符合规则的引擎能使FPGA得到正确的连接,从而防止了在PCB板制作过程当中的重复制作。

引脚分配算法可使对某组引脚分配的接口信号线最优化,这样做减少了PCB板上的网络交叉,改进了PCB板上网络的布通率。

与Cadence创建的设计紧密相连

OrCAD FPGASystem Planner为FPGA子系统生成了OrCAD Capture原理图文件。它使用的是OrCAD Capture元器件库里现有的FPGA元器件符号。如果用户愿意的话,FPGA System Planner产品还可以为FPGA创建单独的符号,这需要基于每个元件库的单个元器件符号的可连接性。

与FPGA供应商提供工具集成

除了集成OrCAD PCB设计工具以外,OrCAD FPGA System Planner还和FPGA进行着紧密的通讯。它生成并读取所支持FPGA供应商的引脚分配约束文件。这些功能使得FPGA设计者能根据FPGA所需要的功能来评估引脚分配。FPGA设计者根据这些要求所做的更改可直接导入OrCAD FPGA SystemPlanner,使得整套引脚分配保持同步。

预布线过程中引脚分配的最优化

考虑到FPGA在PCB板上的摆放位置和布线的最初的引脚分配,如果要减少FPGA设计者、PCB布线设计者和硬件设计者之间的设计迭代,在达到这个目标之前有一段很长的路要走。PCB布线设计者一旦确定要在FPGA的接口和信号线上开始布线,它要进一步完善基于设计意图、叠层约束、扇出选择的FPGA引脚分配。OrCADFPGA System Planner为用户提供了一种优化FPGA引脚的方法,这种优化在摆放FPGA之后,或者对FPGA的接口和信号线进行布线之后。

FPGA System Planner支持器件系列

Artix-7

Kintex-7

Spartan-3

Spartan-3A

Spartan-6 LX

Virtex-4

Virtex-4 FX

Virtex-4 LX

Virtex-4 SX

Virtex-5

Virtex-5 LX

Virtex-6 LXT

Virtex-7

Zynq

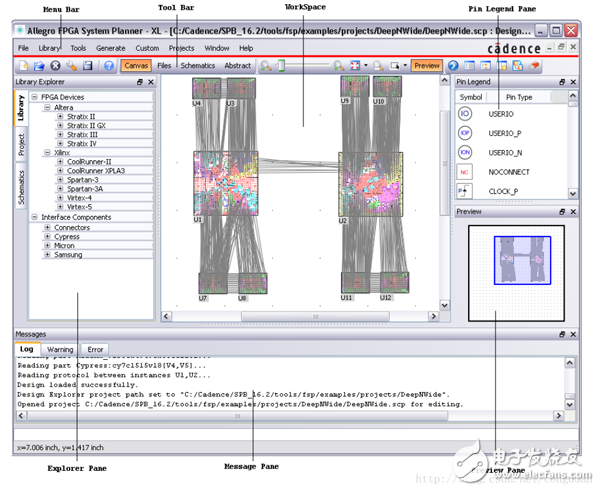

CandanceFPGA System Planner 使用介绍

具体使用可以参考该产品用户指南《Allegro® FPGA System Planner User Guide》

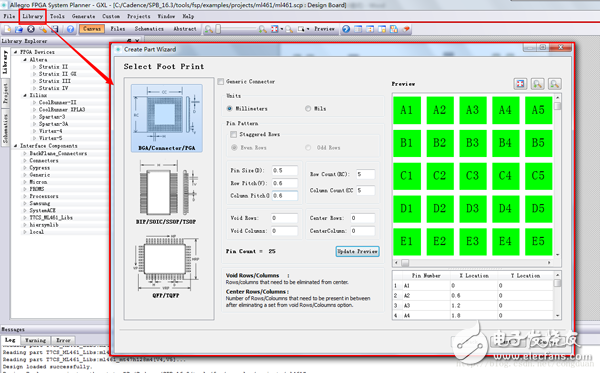

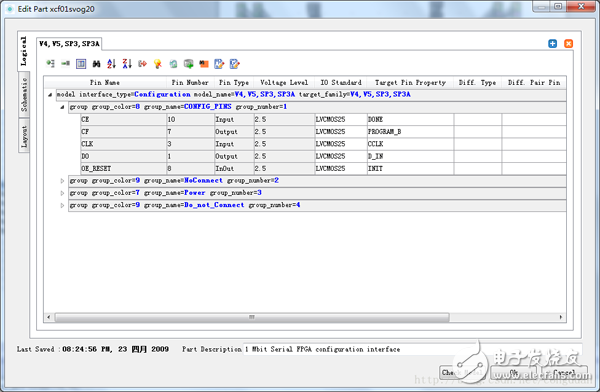

该工具自带Xilinx和Altera两个公司的主流FPGA库,基本不需要自己创建相关的元器件,另外包括一些常用的接口,处理器,SystemACE等库。如果实际使用用使用到了其他的器件,可以自己创建相关的Part,使用相应的菜单和向导即可,但是只提供8种类型的封装,平常使用已经足够。

自定义的器件不仅可以自定义管脚的数量,间距等信息,还能定义相关的IO方向,电平标准以及分类管理。

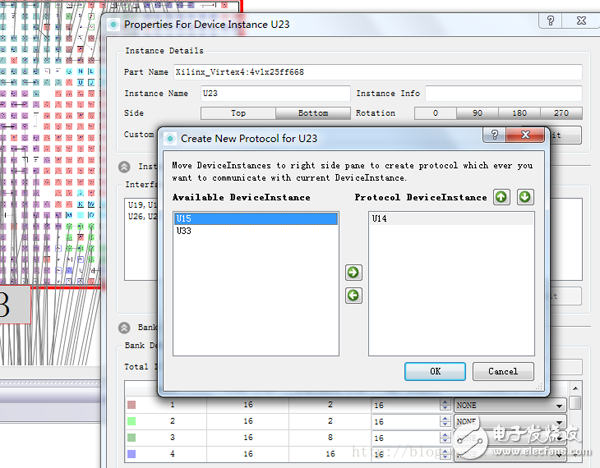

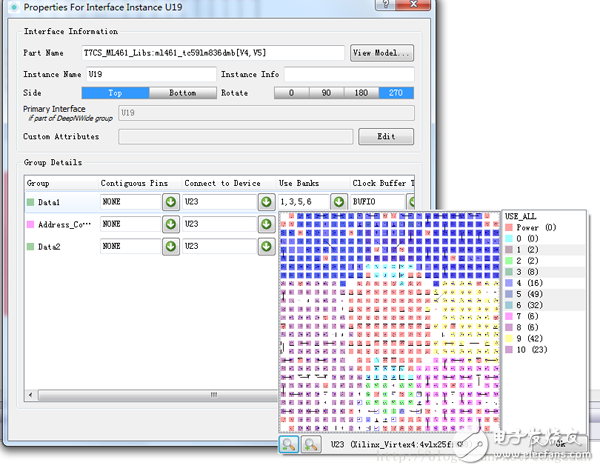

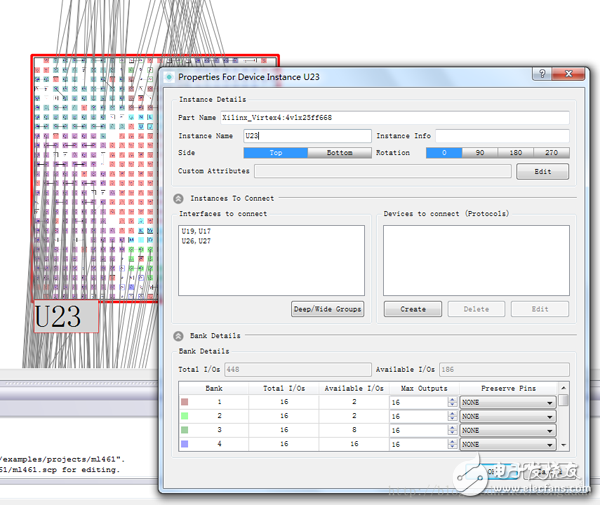

连线的时候,可以右键编辑相应的器件实例对象,选择要连接的其他器件,并定义器件之间的连接规则(是否在同一Bank或哪几个特定的Bank,时钟域以及管脚连续分配),另外还提供一种叫做Deep and Wide的连接,可以相同器件的相同管脚连接到同一片FPGA的某些相同的管脚上,非常方便。

使用时只需要拖放相应的器件到绘图区,自动生成元器件的实例对象,该对象可以进行旋转,平移等编辑操作,配置好相应的连接关系,直接点击Tools→Run design即可生成连接线。生成之后可以修改连接信号名称,导出NetList等文件。

AltiumDesigner Scripting脚本系统

在完成连线之后,需要在Altium Designer中放置对应引脚之间的网络标号NetLabel,由于Altium没有提供相应的自动化功能,这个工作在大规模引脚设计的时候如果手工操作也是十分繁重的工作量,也很容易出现错误。

幸好Altium Designer提供一套强大的脚本系统和完善的API,我们通过编写JavaScript/Pascal/Delphi/VB等脚本,根据前面使用Candance FPGA SyatemPlanner导出的Netlist文件自动完成网络标号的添加,整个设计过程将会省去很多麻烦。

AltiumDesigner支持的脚本可以直接调用其提供的API,包括系统操作,Workspace和Project管理,Schemetic以及PCB编辑,也支持语言标准库的调用。代码示例可以从+Examples+Reference#JScriptScripts找到,

不过Altium Designer自带的脚本开发编辑器除了代码智能提示之外没有过多的亮点,使用的时候可能不会很顺畅,读者可以自行体验。

电子发烧友App

电子发烧友App

评论